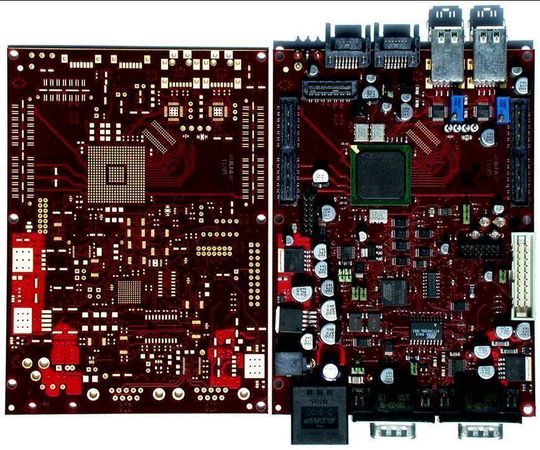

Die Leiterplatte 2010 – das Finale Referenzdesign für High-Speed-Baugruppen

Das Projekt „Die Leiterplatte 2010“ liefert Ergebnisse. Drei aktive Jahre sind vergangen seit der ersten spontanen Idee, mit der Konstruktion einer High-Speed-CPU-Baugruppe eine Referenz für stabile Hardware im Hinblick auf das High-Speed- und EMV-Verhalten zu schaffen. Das Ergebnis sind praxiserprobte Lösungsansätze für die Realisierung von High-Speed-Baugruppen.

Anbieter zum Thema

Wir wissen, wie sehr sich unser Arbeitsalltag verändert hat. Ohne hochwertige und zuverlässige Elektronik geht nichts mehr. Moderne elektronische Baugruppen können nur noch mit Fachwissen, fertigungstechnischer Kompetenz und sensiblem Kommunikationsverhalten erfolgreich umgesetzt werden.

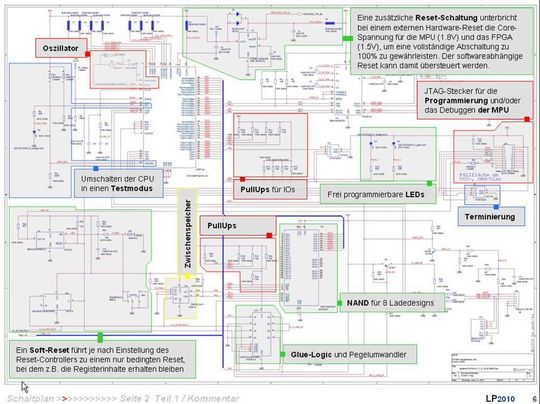

Das Projekt „Die Leiterplatte 2010“ hat deshalb unterschiedliche Aufgabenstellungen gleichrangig eingebunden. Das Handling der Constraints an einem CAD-System, die Verarbeitung dünner Laminate in hochlagigen Multilayern, die Produktion von Baugruppen mit all ihren kleinen Komplikationen und die Dokumentation der Ergebnisse für die Aus- und Weiterbildung gehören dazu. Die Ergebnisse sind richtungsweisend für die Disziplinen CAD-Design, Leiterplatten-Fertigung und Baugruppenproduktion.

Die originale Vorlage für die „Leiterplatte 2010“ ist das High-Speed-CPU-Board „meltemi“ der Firma unitel aus Graz, das Gerhard Eigelsreiter entwickelt hat. Die Anforderungen an diese Baugruppe sind hoch: bei einer zuverlässigen Datentransferrate von mehr als 4 GBit/s werden verbindliche Anforderungen an das EMV-Verhalten und die Signalintegrität gestellt.

Kern des CPU-Board ist ein FPGA. Bei der Signalführung müssen differenzielle Impedanzen beachtet werden. Um die Funktion der Baugruppe unter Last stabil zu halten, wurde besondere Sorgfalt auf die Stromversorgung gelegt. Auf die klassische Entkopplung über die übliche Phalanx an Kondensatoren wurde verzichtet.

Dafür ist der Lagenaufbau des Multilayers mit einem gestapelten Stromversorgungssystem ausgestattet, einem sogenannten Multi-Power-System (MPS), beschrieben im Kompendium „Die Leiterplatte 2010“ in Kapitel 4. Das MPS ist ergänzt um berechnete Kondensatorgruppen (nach der „Methode Dirks“), beschrieben im Kompendium „Die Leiterplatte 2010“ in Kapitel 13.

(ID:321015)

:quality(80)/p7i.vogel.de/wcms/9f/13/9f13686bb894142875a93de7f6c3aabe/0131278942v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e1/9c/e19ca48e7ee7b6604240bdb1a02a3a7d/0131251245v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/8c/f0/8cf0a380137d81e18ab1683a061b7531/0131171547v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/40/00/4000cee04363c2ad502a5cfadded2e0e/0131287222v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/4b/c1/4bc195078a1cc19f3f42f3fdea3cc8c5/0131260433v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/42/65/426590889d9cc3c850ba2ed6184b28d8/0131183751v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/17/71/1771c0b139e32eced60c0f60abd045dc/0131202175v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ab/6e/ab6ee4358adb3ef565a3af4e923dae6b/0131202314v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a0/b7/a0b74e201c3d9a12af0a204e1e578aad/0131136338v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d2/1c/d21cea8a73c1dc8b94322e896fb7cc2b/0131036508v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/be/81/be8197dbe5f61c3c5ade3732457725af/0131041847v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/5b/f2/5bf2fc2e46775b70614326a4003940ea/0131238162v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/58/ed/58ede6960020a2ded5f6771bd9b8e49d/0131277913v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/77/06/77065703c81be2dd11397359059b74ca/0131276872v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/2e/78/2e789ef76c84f5fcdf02b5697a22f9ab/0131062677v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d4/1d/d41d81ec84a42b4fd5d732d36d0021ce/0130877962v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9c/79/9c798ab2b4c18ba0a2c24f2491798d36/0130550888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/e7/b6e755d9e704319c0bb59dc1ac2d67e8/0130537290v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/aa/79/aa79a807ba1ce61e6656226679e05f9c/0131288690v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/34/1f/341f0c9b899c7509a01c9a13383af6cf/0131148001v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ca/8c/ca8cda9df29d8b2cf6f7b09abd8b7dda/0131065542v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/c2/35c2b1da065361aefeea668c786531c9/0131280558v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/05/83/0583267ea76f0beb94c4acef52d485e1/0130855074v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b5/54/b5548923d20a751319550a3eb159af21/0131159519v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/87/b6/87b60368567da3c6b65107c55f5f69ec/0130689118v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/7d/5b/7d5bd7b3575dd8745fac17cf8619a7c2/0131253052v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/94/82/948296f1541e8d3b2060978cfeae90e8/0131311058v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/42/fa424fa7fe94e1ba17869e270e2b2422/0131203375v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/19/75/1975839f578e6bed7a0db82789cd96a4/0131312221v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/69/9c/699c6104d5166/logo-pp-rot-quadratzuschnitt-inv512px.png)

:fill(fff,0)/p7i.vogel.de/companies/60/f6/60f6829670d63/beta-layout-logo.jpeg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/68800/68851/65.jpg)

:quality(80)/p7i.vogel.de/wcms/80/7b/807bc9dc4d65da8b9d67314d544b9e13/0128113873v4.jpeg)

:quality(80)/p7i.vogel.de/wcms/5e/6b/5e6b5884a3188984c14796fdad74d307/0125018815v2.jpeg)