Anbieter zum Thema

Darüber hinaus verstärken die neuen Multi-Die-3D-Chipgehäusetechniken wie SiP (System-In-Package), PoP (Package-On-Package) und andere nur noch die Schwierigkeiten, die sich den Ingenieuren bei Validierung, Tests und Debugging auf der Chip-Ebene stellen.

Ältere kontaktgebundene Technologien wie ICT-Systeme (In-Circuit Test) nutzen eine Testanordnung, bei der eine Sonde verwendet wird. Die Sonden werden an Testpads auf der Leiterplatte (Prüfling) angelegt, um Testsignale mitzuverfolgen (Bild 1).

Bestückungsdichte auf Leiterplatten nimmt stetig zu

Das Verschwinden von Anlegepunkten für Sonden ist eine der größten Schwierigkeiten für ältere, kontaktgebundene Testgeräte. Viele Leiterplatten sind mittlerweile so dicht bestückt, dass der Platz, der früher Testpunkte vorbehalten war, einfach nicht mehr vorhanden ist. Zudem werden jetzt viele Boards im Mehrschichtverfahren gefertigt, wodurch der direkte Zugang zu den Leiterbahnen auf den inneren Schichten praktisch vollkommen versperrt ist. Darüber hinaus wurden bei Komponentengehäuse in Chipgröße wie bei BGAs die Bausteinpins, die früher das Anlegen einer Testsonde ermöglicht haben, mit Lötverbindungen unter dem Die ersetzt, die nicht mit einer Sonde getestet werden können.

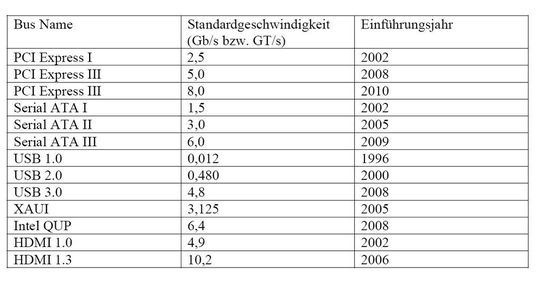

Im Laufe der Jahre sind die Geschwindigkeiten von I/O-Bussen auf Leiterplatten beständig gestiegen (Tabelle 1).

Tool-Techniken für Embedded-Instrumentierung

Verschiedene softwarebasierte, berührungslose Techniken, die ohne Sonden auskommen, können die Basis für Tools bieten, die von Embedded-Instrumentierung profitieren. Dazu zählen Boundary-Scan (basierend auf dem IEEE 1149.1 und oft als JTAG bezeichnet), PCT-Tests (Processor-Controlled Test), bestimmte Instrumentierungstechniken für Highspeed-I/O-Busse sowie Techniken, die Instrumente auf Chip-Ebene ansteuern.

Artikelfiles und Artikellinks

(ID:23795960)

:quality(80)/p7i.vogel.de/wcms/37/ec/37ece4c276f37114e8f40696ff5dcd66/0130537789v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/46/7c/467c0afffbfd10c3553c2888a4a6289f/0130479810v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/12/3d/123d9eb2c2e4ce13296371a2ad3718a4/0130412664v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/e7/b6e755d9e704319c0bb59dc1ac2d67e8/0130537290v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/8b/10/8b10d1edceb749de99c1df3ad97be01e/0130564619v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ac/da/acda3bafe46d3bf8e104a2a7bc2ac557/0130535476v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ca/9b/ca9b681785123f9700518a46897f9779/0130428786v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/38/cb/38cbe19e814dd30b94780bc3946547ab/0130446533v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/88/c28805ea7b2261235475146a5b0c61f8/0130313028v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/8d/fa8dedee195f29c33c89d86311c258ee/0130104146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/7a/697a270ed7538378d1fbc0f0b240ed25/0130534691v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/e7/a4/e7a4e048491e60cb30e22a860f5d68bc/0130519425v4.jpeg)

:quality(80)/p7i.vogel.de/wcms/1b/f0/1bf02d41e3eac721823841a4c1228753/0130519149v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1a/53/1a539631c940d184689460600bd2b395/0130410666v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/10/45/1045969e69a1db4aaa73d0f74f55cc02/0129962687v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/e4/bae4e54395e5a53088060531ef99b814/0130359274v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/af/35af7dd326d198475d06fbb69aa600b5/0130175971v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/2e/c02e7bf72bfc434888c37100e2511681/0130127767v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/e1/0b/e10bc04827e33786548587e32bbae422/0130438700v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/06/3506f2a8d33a696aaef12a30771bd8d8/0130496747v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/ed/e5ed08c670c44565a9130e95a760dddc/0130494578v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ce/33/ce336bc438b912829effe8d4704dc159/0130480307v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/3a/72/3a722ed2ad6ac4894c352e6ce87b6560/0130567207v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e4/d1/e4d122a8ecce14b98c8298c1cc130194/0130561462v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/3c/55/3c5505dd3ca3971cddd09c583a4c907d/0130458429v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/47/ce/47ce64bad7990f276f68cbb24505f6dd/0130472850v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/2e/95/2e9597b5dc1873771c7fe9c32ac41e82/0130549010v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/15/56/15564dea31861c376a385658c3b961a3/0130465243v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bf/2a/bf2aad428ab1a80e6738fdbdc2efeb7e/0130453420v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/66/1f/661fa8e004810/heitec-logo-2024-1200px-ae.png)

:fill(fff,0)/p7i.vogel.de/companies/69/7c/697cbb83628bc/logo-16-9.png)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/72000/72046/65.jpg)

:quality(80)/p7i.vogel.de/wcms/b3/65/b365dd5433c8b6d36c56c92b72f5b368/0130401081v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/4f/22/4f2287af1f07561a5703d6a20f39494b/0128418964v2.jpeg)