Halbleiter-Taktgeneratoren PLLs ersetzen Quarz-Oszillatoren für perfektes Timing

Es gibt gute Gründe, herkömmliche Quarze und Oszillatoren durch Halbleiter-Taktgeneratoren zu ersetzen. Je nach Anwendung sparen PLL-ICs Platz und reduzieren die Anzahl der benötigten Bauteile. Dies macht die Schaltungen günstiger und den gesamten Clock-Tree zuverlässiger.

Anbieter zum Thema

Die hohe Leistungsfähigkeit und verhältnismäßig geringen Kosten quarzbasierter Oszillatoren machten diese zur branchenweit ersten Wahl bei der Generierung von Taktsignalen. Eine Alternative dazu sind die neusten Halbleiter-Takt-ICs. Sie bieten zahlreiche Vorteile: Beispielsweise lässt sich mit ihnen Platz auf der Leiterplatte einsparen, und sie können die Leistungsfähigkeit des gesamten Clock-Trees verbessern.

Das Potenzial, Platz einzusparen, ist der wohl größte Vorteil der Halbleiter-Taktgeneratoren. Denn neben der Möglichkeit, kompakter zu bestücken, lässt sich mit den Takt-ICs auch die Anzahl an Bauteilen verringern. Bei mehreren Phase-Locked Loops (PLLs) auf einem Chip reicht ein einziger Takt-IC zur Generierung unterschiedlicher Ausgangsfrequenzen. Dabei muss der Frequency-Select-Pin nur auf High oder Low gelegt werden. Ein einziger Takt-IC kann somit mehrere Quarze ersetzen.

EMV-Werte mit Takt-ICs verbessern

Takt-ICs sparen auch Platz, da weniger diskrete Bauelemente erforderlich sind, um die EMV-Vorschriften einzuhalten. Um die EMV-Werte zu verbessern, kann der Entwickler den Taktausgängen wahlweise eine Bandspreizmodulation (Spread Spectrum) hinzufügen. Diese ist günstiger und einfacher als herkömmliche Maßnahmen wie Abschirmung, Ferrite und EMV-Dichtungen.

Die Möglichkeit, mit einem einzigen Baustein den Takt umzuschalten, zu puffern und zu verteilen, trägt ebenfalls dazu bei, Gesamtzahl der Bauelemente reduzieren. Ein Halbleiter-Takt-IC kann beispielsweise zusätzlich zu anderen Frequenzen vier Ausgänge mit der gleichen Frequenz bereitstellen, dazu noch die Timing-Quelle und den Puffer. Ein Clock-Tree in einem einzigen Baustein ermöglicht zudem eine bessere Kontrolle des Bitversatzes (Skew) und der Signallaufzeit.

Einige Takt-ICs unterstützen die In-System-Programmierung (ISP) über zahlreiche Funktionen: I2C- oder JTAG-Schnittstelle, nicht flüchtiger Speicher, mehrere PLLs, Steuerungslogik und konfigurierbare I/Os sowie Routing. Damit lässt sich ein kompletter Clock-Tree in einem programmierbaren und rekonfigurierbaren Chip implementieren. Designs können somit einem Update unterzogen werden, das über Software oder Firmware erfolgt.

Bessere Leistung und niedrigere Kosten

Die Leistungsfähigkeit von Clock-Trees profitiert ebenfalls vom halbleiterbasierten Timing, da sich Taktausgänge mit unterschiedlichen Frequenzen synchron zu einander erstellen lassen. Beim Digital-TV oder bei Set-Top-Boxen bedeutet dies, dass die gleichen Frequenzfehler eines 27-MHz-Video-Takts und eines 12,288-MHz-Audio-Takts eine optimale Lip-Sync (Lippensynchronisation) ermöglichen.

Auch die Genauigkeit lässt sich mit Halbleiter-Takt-ICs verbessern. Ein Takt-Synthesizer-IC, der an eine hochgenaue Quelle angeschlossen ist, weist dann die gleiche Frequenzgenauigkeit wie die Quelle auf. In einem System mit einem temperaturgesteuerten Oszillator (TCXO), der bei 19,2 MHz mit ±2,5 ppm Genauigkeit läuft, kann die Referenzierung eines Takt-ICs an den TCXO einen Ausgang mit 12,288 MHz und der gleichen Genauigkeit hervorbringen. Damit kann ein zweiter TCXO im System entfallen.

Höhere Leistung bei geringeren Kosten

Da die Frequenzen in Halbleiter-Takt-ICs gegenseitig festgelegt sind, vereinfacht sich die Kopplung zwischen unterschiedlichen Taktebenen. Die Leistungsaufnahme lässt sich effizient über Taktdrosslung verwalten, beispielsweise indem ein USB-Takt zur Stromeinsparung abgeschaltet wird, solange der Anschluss nicht in Betrieb ist.

Halbleiterbasiertes Timing bietet neben der besseren Systemleistungsfähigkeit auch Kostenvorteile. Ersetzt man mehrere Quarze durch einen einzigen programmierbaren Halbleiter-Takt-IC, muss anstelle mehrerer Bausteine nur ein Bauteil gelagert und verwaltet werden.

Die Verfügbarkeit ist ebenfalls besser, da die Lieferzeiten für Silizium meist kürzer sind als für Quarzoszillatoren. Denn die Herstellung der sehr dünnen Quarzscheiben – vor allem bei HF-Oszillatoren – verursacht längere Lieferzeiten. Dies beeinflusst auch die Qualität und Gesamtzuverlässigkeit des Systems, da empfindliche Quarzbausteine durch robustere Halbleiterbauelemente ersetzt werden.

Quarzersatz durch Takt-ICs

Beachtet man einige wenige Grundregeln, lassen sich mit Takt-ICs Quarze einfach ersetzen. Die Eingangsanforderungen des Zielbausteins sind dabei entscheidend, da sich die Taktcharakteristika eines jeden Chips – Frequenzgenauigkeit, Stabilität, Tastverhältnis und Jitter – selbst bei Bausteinen des gleichen Herstellers unterscheiden können.

Die erforderliche Genauigkeit hängt von der Applikation ab: Während Mikroprozessoren mit einer Frequenzgenauigkeit von 200 ppm arbeiten, benötigen andere Anwendungen, wie zum Beispiel serielle Kommunikationsverbindungen, eine Genauigkeit von 20 ppm für SONET oder 500 ppm für USB.

Es ist hilfreich, anstelle einer eigentlichen Jittermessung die Jitter-Performance aus dem Datenblatt als Maßstab zu verwenden. Die meisten Bausteine werden nicht auf Jitter getestet. Ihre Daten basieren dann auf der Jitter-Spezifikation des Oszillators.

Kommt es auf eine genaue Jitteranalyse an, verwendet IDT spezielle Messgeräte und -verfahren, um den Halbleitertakt an eine bestimmte Applikation und den Clock-Tree anzupassen. Applikationen, in denen kurzzeitige und zyklusweise Jitter- oder EMI-Störungen verringert werden sollen, erfordern eine gute Entkopplung. Um längerfristigen Jitter zu verringern, stehen eine Reihe von Filterlösungen für die Stromversorgung zur Verfügung (Bild 1).

Clock-Trees in naher Zukunft

Der Ersatz von Quarzen und Oszillatoren durch halbleiterbasiertes Timing verringert nicht nur die Bauteilanzahl und den Platzbedarf auf der Leiterplatte – ein gesamter Clock-Tree lässt sich in einen einzigen Chip integrieren. Takt-ICs können auch Leistungsaufnahme- und EMI-Merkmale verwalten und ermöglichen durch ihre In-System-Programmierfähigkeit flexiblere Designs, die für die Zukunft gerüstet sind.

Der PLL als Taktgeber

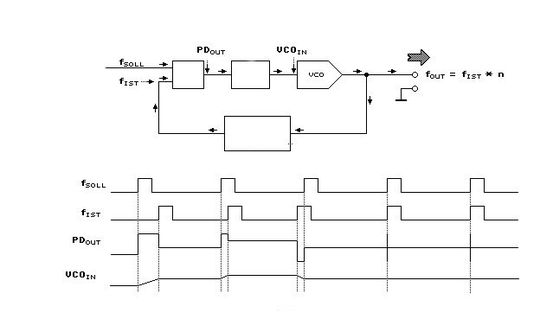

Ein PLL ist ein phasengekoppelter Regelkreis. Er eignet sich unter anderem zum Abgleich von Frequenzen und zur Erzeugung von Taktsignalen.

Zur Taktgeneration benötigt der PLL eine Referenzfrequenz (fref), die meist ein sehr genauer Quarzoszillator bereitstellt. Im PLL selbst ist ein spannungsgeregelter Oszillator (VCO) integriert. Dessen Taktfrequenz synchronisiert der Regelkreis auf die Referenz fref: Ein Frequenzteiler teilt das vom VCO generierte Signal in den Bereich von fref herunter.

Ein Phasendiskriminator vergleicht nun die Phasendifferenz des geteilten VCO-Signals und fref und gibt eine entsprechende Regelspannung an den VCO weiter. Dadurch wird die VCO-Frequenz genau auf fref synchronisiert. Mithilfe des Teilers lassen sich so auch Takte vom Vielfachen von fref erzeugen, die mit dem Referenzsignal in Phase sind.

Zwischen den Ausgang des Phasendiskriminators und den Eingang des VCO ist ein Tiefpass geschaltet. Dieser filtert zum einen Schwingungen heraus, die dem Gleichspannungssignal des Diskriminators überlagert sind. Eine weitere wichtige funktion des Tiefpasses ist es, sehr kleine Regelsignale zu unterdrücken und damit einen Toleranzbereich für das Ausgangssignal zu schaffen. Ansonsten können bei sehr schnellem Nachregeln minimaler Abweichungen Oberschwingungen entstehen.

*Jan Gazda ist Director Applications Engineering der MicroClocks Division von IDT.

(ID:225459)

:quality(80)/p7i.vogel.de/wcms/f5/5e/f55e737a7d227f2d048c579cab8e6985/0130834955v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/33/b4/33b4ab2c6baf7bd98f6f31747f105ab7/0130823277v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/96/97/96978cf39fdc205e816e3218f39499e5/0130663068v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/14/e8/14e887156fd8fb66138bfc7972c4cd3f/0131074909v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/51/08/5108a9dea8ae93ecddbcf8beaf0540f8/0131047719v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/4d/ba4d85f7677531f446b5258a0cd242bf/0131025523v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/2e/78/2e789ef76c84f5fcdf02b5697a22f9ab/0131062677v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d9/92/d9920f978cf2b03bb4f2b4e6cfbface3/0131055455v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d2/1c/d21cea8a73c1dc8b94322e896fb7cc2b/0131036508v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/be/81/be8197dbe5f61c3c5ade3732457725af/0131041847v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/0d/34/0d34c0b5b16676a55682e081ca59da32/0130890395v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c5/42/c542a36bfc0e9beb119924d176f19e06/0131065166v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/71/b7/71b7507ed6f501a79b26477f34c8b28c/0130974158v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d4/1d/d41d81ec84a42b4fd5d732d36d0021ce/0130877962v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9c/79/9c798ab2b4c18ba0a2c24f2491798d36/0130550888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/e7/b6e755d9e704319c0bb59dc1ac2d67e8/0130537290v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ca/8c/ca8cda9df29d8b2cf6f7b09abd8b7dda/0131065542v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/71/fa71d141fca285824eb23f3aba1333f2/0131012876v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e1/39/e13927f73987c9fb63d6f7145a597e6a/0130656559v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/87/b6/87b60368567da3c6b65107c55f5f69ec/0130689118v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b4/55/b455edd54c7e92e0f5bf2d059e2cc5ca/0130990400v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9b/96/9b96763092ce22624400387c5f264287/0130960582v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/82/71/8271e36a4b6aa180fa903edd1de396f1/0130907348v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f6/e7/f6e70a7430db9783176d5e3bf25f5707/0131063190v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/ec/6b/ec6bb7201f5a2e41cd4942d59b23b999/0131074433v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/0a/350a177ef33b960e8f24c9be3717c653/0131061473v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ae/92/ae92a78425f17c6358d01ffd9b1c90ed/0131050297v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fc/5e/fc5e77b8434779834850aab40a903347/0131047752v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/43/c2439a5f7ecd10d2d7f02a4a5f38e97d/0131046056v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/110300/110321/65.png)

:fill(fff,0)/p7i.vogel.de/companies/61/a8/61a8d8e6ca4c2/glyn-logo-profilbild.jpeg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/9600/9682/65.jpg)

:quality(80)/p7i.vogel.de/wcms/42/cb/42cbcb66dffa2ef6548d5fb2edee4b4a/0130519441v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/61/6c/616c1e8041dbfc3c2faaa29430c62f8d/0127093746v2.jpeg)