Anbieter zum Thema

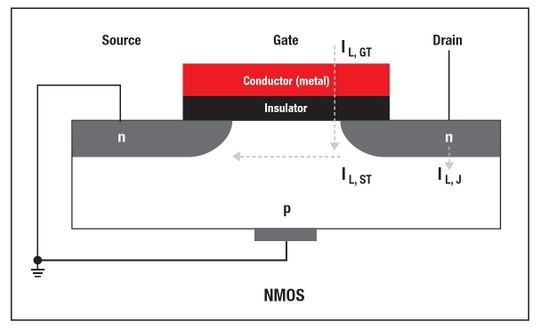

Auf Transistorebene ist der statische Energieverbrauch PS das Produkt aus der Versorgungsspannung Vss und IL. Bestandteile des Leckstroms sind der Leckstrom unterhalb des Schwellenwertes (I < SUB < L,ST(sub)) im abgeschalteten Zustand des Transistors, der Leckstrom im durchgeschalteten Zustand (IL,J); und der Tunnel-Leckstrom (IL,GT) (Bild 1).

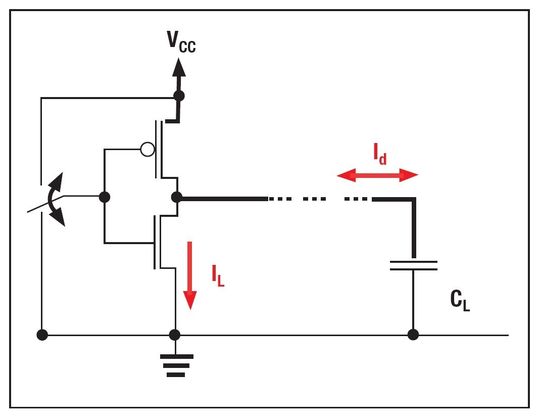

Andererseits stellt der dynamische Energieverbrauch eine Funktion der Taktgeschwindigkeit (Geschwindigkeit der Transistorschaltvorgänge) und der kapazitiven Ausgangslast des Transistors dar. Er hängt ebenfalls von der physikalischen Transistorgeometrie ab. Es gilt folgender Zusammenhang: I = C dV/dt und PD = ID Vcc = C f Vcc², wobei C die kapazitive Last (Transistor und Anschlussleitung), f die Schaltfrequenz und Vcc die Versorgungsspannung ist.

Im Idealfall beträgt der statische Energieverbrauch null, wodurch der Gesamtenergieverbrauch dem Wert PD entspricht. Bild 2 zeigt den Leckstrom und den dynamischen Strom, die durch einen CMOS-Inverter fließen. Die Weiterentwicklung der Prozesstechnik führt auch dazu, dass der statische Energieverbrauch schneller zunimmt als der dynamische.

Betriebsspannungsanpassung und deren Auswirkung

Im Allgemeinen nehmen die Strukturgrößen ab und die Feldstärken innerhalb des Elements zu. Um den dynamischen Energieverbrauch zu reduzieren, passen die Entwickler daher in der Regel die Betriebsspannung an. Jedoch gewinnt dabei die statische Energieaufnahme, die exponentiell mit dem Leckstrom zunimmt, an Bedeutung. Der unter dem Schwellenwert liegende Leckstrom nimmt bei steigender Temperatur ebenfalls exponentiell zu.

Ein höherer statischer Energieverbrauch führt darüber hinaus zu weiteren Problemen, da er die Leistungsdichte über der gesamten aktiven Chipfläche beeinflusst. Damit steigt das Risiko, dass energiekritische Punkte (sogenannte Hot Spots) entstehen können. Die Beherrschung des statischen und des dynamischen Energieverbrauchs ohne Beeinflussung der Leistungsfähigkeit erfordert daher ein bestimmtes Ausmaß an Intelligenz und Anpassungsfähigkeit. Dies gilt sowohl auf der Chip- als auch auf der Systemebene.

Artikelfiles und Artikellinks

Link: TMS320TCI648x User Guide

(ID:263742)

:quality(80)/p7i.vogel.de/wcms/f5/5e/f55e737a7d227f2d048c579cab8e6985/0130834955v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/33/b4/33b4ab2c6baf7bd98f6f31747f105ab7/0130823277v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/96/97/96978cf39fdc205e816e3218f39499e5/0130663068v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/37/59/37594ae9b98dc4acb8eeab90c835c984/0131089404v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/39/2b/392b7f42b33965cee9d46984d8e1c021/0131069829v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/14/e8/14e887156fd8fb66138bfc7972c4cd3f/0131074909v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/2e/78/2e789ef76c84f5fcdf02b5697a22f9ab/0131062677v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d9/92/d9920f978cf2b03bb4f2b4e6cfbface3/0131055455v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d2/1c/d21cea8a73c1dc8b94322e896fb7cc2b/0131036508v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/be/81/be8197dbe5f61c3c5ade3732457725af/0131041847v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/0d/34/0d34c0b5b16676a55682e081ca59da32/0130890395v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/cc/bacc37befe18c7062ab18bdae3ea75c7/0131064254v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f2/fb/f2fb476fbd80a9145a022a4d162002df/0131122156v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/c5/42/c542a36bfc0e9beb119924d176f19e06/0131065166v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/d4/1d/d41d81ec84a42b4fd5d732d36d0021ce/0130877962v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9c/79/9c798ab2b4c18ba0a2c24f2491798d36/0130550888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/e7/b6e755d9e704319c0bb59dc1ac2d67e8/0130537290v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ca/8c/ca8cda9df29d8b2cf6f7b09abd8b7dda/0131065542v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/71/fa71d141fca285824eb23f3aba1333f2/0131012876v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e1/39/e13927f73987c9fb63d6f7145a597e6a/0130656559v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/87/b6/87b60368567da3c6b65107c55f5f69ec/0130689118v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b4/55/b455edd54c7e92e0f5bf2d059e2cc5ca/0130990400v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9b/96/9b96763092ce22624400387c5f264287/0130960582v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/82/71/8271e36a4b6aa180fa903edd1de396f1/0130907348v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1e/27/1e27744bed9341deb4f1d27d541e04e3/0131125212v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/96/e4/96e4b9434e4bb7b4e06cccc26e8a6497/0131080817v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ec/6b/ec6bb7201f5a2e41cd4942d59b23b999/0131074433v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/0a/350a177ef33b960e8f24c9be3717c653/0131061473v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ae/92/ae92a78425f17c6358d01ffd9b1c90ed/0131050297v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fc/5e/fc5e77b8434779834850aab40a903347/0131047752v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/43/c2439a5f7ecd10d2d7f02a4a5f38e97d/0131046056v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/64/21/64219ce08bf52/logo.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/62/6f/626f9753a3e5a/a-category-images-970x300-logo.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/68/62/68621fc4f1d39/logo.png)

:quality(80)/p7i.vogel.de/wcms/de/48/de48603453b0bd091cef84dbbefe37c1/0126851659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/0a/f9/0af9ef52ce077b935efc629bd4e357a6/0128162746v1.jpeg)