2D-MOSFET: Steht die Miniaturisierung von Transistoren vor dem Durchbruch?

2D-Werkstoffe haben ein hohes Potenzial zur Miniaturisierung von Transistoren. Im Beitrag diskutieren wir den Stand der Technik und die Herausforderungen bei der Entwicklung von 2D-Transistoren, deren Integration in eine 300-mm-Fertigung und die Optimierung ihrer Leistungsfähigkeit.

Anbieter zum Thema

2D-Materialien bilden eine Werkstofffamilie, die eine Atomlage „groß“ ist. Durch sie könnten neue, miniaturisierte Halbleiter-Anwendungen möglich werden, wie Speicher-Wahlschalter oder Back-end kompatible Transistoren. Durch die Integration in den leitenden Kanal von MOSFETs lassen sich 2D-Werkstoffe auch zur Realisierung extrem verkleinerter Hochleistungstransistoren verwenden.

2D-Materialien könnten zahlreiche Applikationen ermöglichen

In den letzten Jahren haben 2D-Werkstoffe wie Graphen und Dichalkogenide (MX2) von Übergangsmetallen beträchtliche Aufmerksamkeit erregt. Das außergewöhnliche Interesse an diesen Werkstoffen kann man ihren besonderen Eigenschaften zuschreiben. 2D-Materialien haben im Vergleich zu traditionellen dreidimensionalen Kristallstrukturen sehr interessante Formfaktoren.

Durch ihre zweidimensionale Ausdehnung (eine Atomlage), ihre elektronische Struktur, mechanische Flexibilität und spezifische Defekt-Ausbildung sowie ihre elektronische und optische Empfindlichkeit verhalten sie sich grundlegend anders als ihre Pendents bei den Volumenwerkstoffen.

Das bisher bekannteste 2D-Material ist Graphen, ein Monolayer aus Kohlenstoff-Atomen, die in einem hexagonalen, wabenförmigen Gitter angeordnet sind. Graphen ist ein flexibles, transparentes und extrem festes Material. Außerdem ist Graphen ein sehr guter thermischer und elektrischer Leiter.

Inzwischen erstreckt sich die Erforschung von 2D-Werkstoffen jedoch weit über das Graphen hinaus. So hat die MX2-Materialklasse sehr vielseitige Eigenschaften, die diejenigen von Graphen ergänzen. Beispielsweise haben MX2-Werkstoffe eine große Bandlücke – im Gegensatz zu Graphen. Das Interesse an 2D-Materialien reicht heute über ihre Halbleitereigenschaften hinaus und umfasst auch die Untersuchung von Isolatoren und von Metallen.

Einsatzmöglichkeiten für diese Werkstoffe zeigen sich in vielen Anwendungsfeldern, einschließlich (Bio)sensing, Energiespeicherung, Photovoltaik, Optoelektronik und Transistorskalierung. So ist Graphen auch ein idealer Werkstoff für die Optoelektronik. Es zeigt sowohl Absorption als auch Refraktion. Damit ist es gut geeignet zur Lichtmodulation/Detektion und als Schaltelement. Neuere Forschungen demonstrieren das Einsatzpotenzial einer Graphen-basierten integrierten Photonik für die nächste Generation von Datentechnik- und Telecom-Applikationen.

Sind 2D-Materialien das neue Silizium?

Einige dieser 2D-Werkstoffe könnten sogar das 'gute alte Silizium' in MOSFETs ersetzen. Bei Silizium treten bei der Verringerung der Gate-Länge im leitenden Kanal sogenannte Short-Channel-Effekte auf, die die Leistungsfähigkeit des Transistors herabsetzen. Beim Ersatz des Siliziums durch 2D-Werkstoffe tritt dieser Effekt nicht auf. Da der leitende Kanal nun auf der atomaren Ebene präzise strukturiert ist, kann er auch sehr dünn ausgelegt werden, im Extremfall bis zu einzelnen Atomen.

Außerdem zeigen einige 2D-Materialien niedrige Dielektrizitätskonstanten, die mit denen von Siliziumoxid vergleichbar sind. Damit lassen sich übereinander angeordnete Lagen mit unterschiedlichen Funktionen (z.B. leitender Kanal, Dielektrikum) realisieren. Darüber hinaus kann die Gate-Länge bis auf einige Nanometer verringert werden. Auf diese Weise könnten 2D-Materialien die Möglichkeit eröffnen, die Komponentengröße extrem zu verringern. Ziel sind Strukturbreiten von 3 nm und darunter.

Allerdings werden die ersten Implementierungen von 2D-Materialien in elektronischen Schaltungen wahrscheinlich nicht als extrem verkleinerte Komponenten, sondern in Form von Low-Power-Schaltungen auf den Markt kommen, die geringere Anforderungen an die Leistung stellen (wie geringere Einschaltströme).

Beispiele hierfür sind Transistoren und Schaltungen, die sich im BEOL (back-end-of-line) der Chips implementieren lassen. Hier können sie Routing-Probleme reduzieren und Platz im FEOL (front-end-of-line) einsparen. Für den Bau von Back-end-kompatiblen Transistoren werden derzeit mehrere Werkstoffe, einschließlich dem halbleitenden Indium-Gallium-Zinkoxid (IGZO), und zahlreiche andere 2D-Materialien untersucht. Ein spezifischer Vorteil von 2D-Werkstoffen ist deren Eignung zum Aufbau von komplementären MOS-Bausteinen, wie n-MOSFETs und p-MOSFETs.

Damit lassen sich auch kompakte Back-end Logikschaltungen wie Repeater entwickeln. Eine allgemeine Anforderung an diese Back-end Transistoren und Schaltungen ist durch das Temperatur-Budget gegeben: Es sollte kompatibel mit der „Back-end-of-line“-Verarbeitung sein. 2D-Materialien lassen sich auch zum Aufbau anderer Schaltungen heranziehen, etwa von Onchip-Power-Management-Systemen, Signal-Puffern und skalierbaren Speicherwahlschaltern.

Für alle Schaltungen sind die Anforderungen in Bezug auf den Einschaltstrom Ion relativ niedrig. Im Gegensatz zu stark skalierten Komponenten dürfte eine Lage des 2D-Materials ausreichen, um derartige Komponenten herzustellen.

300-mm Plattform für Komponenten auf der Basis von 2D-Werkstoffen

Für extrem skalierte Komponenten und auch für weniger anspruchsvolle Schaltungen untersucht IMEC die Werkstoff- und Prozess-Grenzen der 2D-Materialien. Der Fokus liegt auf Werkstoffen (einschließlich 2D-Hableitern, 2D-(Halb)Metallen und 2D-Dielektrika) sowie der Prozess-Integration und Komponenten.

Ziel ist ein Fertigungsprozess, der generelle Anforderungen aller Applikationen berücksichtigt, beispielsweise das zulässige Temperatur-Budget und die chemische Stabilität der 2D-Werkstoffe. Der Prozess zielt auf 300-mm-Wafer, damit sich alle Vorzüge hochvolumiger Fertigungsverfahren nutzen lassen. Die große Herausforderung besteht darin, die einkristllinen Flakes der 2D-Werkstoffe während des 300-mm-Fertigungsprozesses zu erhalten.

FETs mit 2D-Werkstoffen für Hochleistungsbausteine: Double-Gate WS2 FET-Architektur

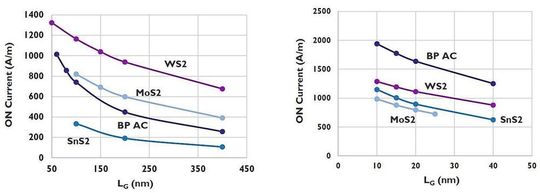

Die Entwicklung von extrem verkleinerten Hochleistungsbausteinen beginnt mit der Auswahl des aussichtsreichsten 2D-Materials und der Baustein-Architektur. Die Wissenschaftler in Löwen haben dazu einen Benchmark unterschiedlicher 2D-Materialien und 2D FET-Architekturen im Vergleich zu Silizium-FinFETs durchgeführt. Aus diesen Studien leitete das Team ab, dass Wolfram-Disulfid (WS2) in einer Nanosheet-Stack-Konfiguration das höchste Potenzial (den größten Durchlassstrom) unter den für die 300-mm-Technologie kompatiblen Werkstoffen bietet (Bild 1).

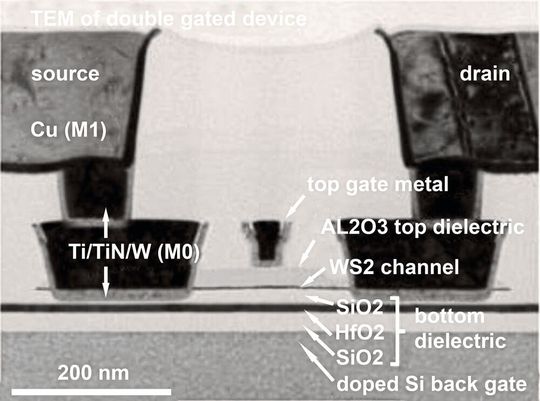

Eine weitere Schlussfolgerung war, dass eine Double-Gate FET-Architektur besser als ein Single-Gate FET ist, insbesondere dann, wenn die Struktur der Komponente bei Kontakten und Abstandhaltern nicht ideal ist (Bild 2).

Das Aufwachsen auf 300-mm-Wafer und Layer-Transfer ist weltweit das erste Mal gelungen: Ein wichtiger Prozessschritt bei der Bausteinfertigung ist das Aufwachsen von WS2 auf 300-mm-Wafern. Den Wissenschaftlern in Löwen gelang dies mithilfe eines modifizierten Beschichtungsverfahrens (MOCVD, metallorganische chemischen Gasphasenabscheidung).

Dieser Ansatz führt dazu, dass die Dicke der Monolayer präzise über den gesamten 300-mm-Wafer gesteuert werden kann. Die MOCVD-Abscheidung erfolgt bei hohen Temperaturen. Um Bausteine zu fertigen, die mit den BEOL-(back-end-of-line) Anforderungen kompatibel sind, ist daher die anschließende Übertragung des Kanal-Materials vom Substrat auf den Bauelemente-Wafer entscheidend.

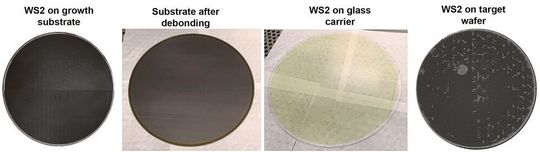

Ein spezieller Transferprozess ermöglicht die Übertragung des WS2-Monolayers – der nur 0,7 nm dick ist – auf den Wafer. Der Transferprozess basiert auf temporären Bonding- und Debonding-Techniken. Er beeinflusst die elektrischen Eigenschaften des 2D-Materials (Bild 3) nicht.

Das Verfahren wurde sogar auf Zielsubstraten eingesetzt, die eine Oberflächenstruktur aufweisen. Zukünftige Entwicklungen haben weitere Verbesserung des Transferprozesses zum Ziel, um Defekte wie Partikel, Markierungen auf der Oberfläche und Absplitterungen an den Kanten zu beheben.

Herausforderungen bei der Strukturierung des Transistors

Bei der Strukturierung der Bausteine bestehen größere Probleme beim Gate-Dielektrikum, den metallischen Kontakten, bei Defekten im Kanal und bei der Speicherung.

Die Abscheidung dielektrischer Werkstoffe auf der 2D-Oberfläche ist wegen des Fehlens von van-der-Waals-Bindungen auf der Oberfläche schwierig.

In Löwen untersucht man derzeit zwei Wege für das Aufwachsen des Dielektrikums: (1) direkte Atomlagenabscheidung (atomic layer deposition, ALD) bei reduzierter Temperatur, und (2) eine verstärkte ALD-Keimbildung durch Verwendung eines sehr dünnen oxidierten Schicht (wie oxidiertes Silizium) als Keimbildungsschicht.

Bei der letztgenannten Technik zeigen vorläufige Messungen an einer Dual-Gate-Konfiguration einen guten Kapazitätswert bei einem verkleinerten Dielektrikum, sowohl auf der Vorder- als auch auf der Rückseite des 2D-Materials.

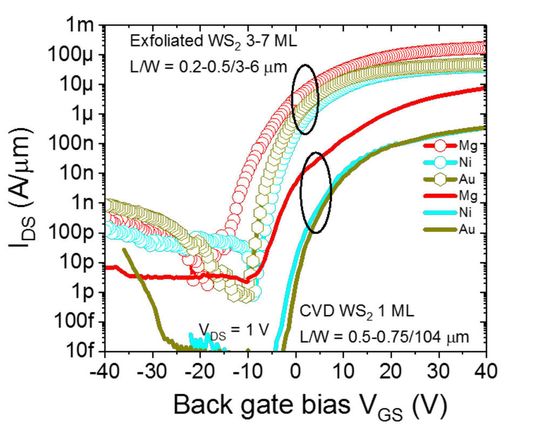

Die Wissenschaftler untersuchten ebenfalls zahlreiche Werkstoffe zur Kontaktierung des WS2-Nanosheets. Dabei stellte sich heraus, dass der größte Durchlassstrom bei der Verwendung eines Magnesium-Kontakts erzielt wurde (Bild 4).

Defekte spielen eine kritische Rolle für das chemische Verhalten der 2D-Werkstoffen und beeinflussen damit die Leistung der Bausteine erheblich. Deshalb ist es wichtig, die Grundlagen der Defektausbildung und deren Einfluss auf die Baustein-Leistungsfähigkeit zu verstehen. Einer der häufigsten Defekte im Kanal-Material sind Schwefel-Leerstellen.

Die Forscher untersuchen derzeit, wie sich unterschiedliche Plasma-Behandlungen einsetzen lassen, um diese Defekte zu passivieren. Daneben sollten auch die Stabilität und Reaktivität der Materialien beachtet werden. 2D-Materialien wie WS2 sind dafür bekannt, dass sie schnell altern und Degradationseffekte zeigen. Eine erfolgversprechende Maßnahme dagegen ist die die Lagerung der Samples in einer inerten Umgebung.

Baustein-Leistungsfähigkeit: Benchmarking und Ausblick

Durch ein Benchmarking haben die Wissenschaftler die Obergrenzen der Baustein-Leistungsfähigkeit abgeschätzt und untersucht, welches Vorgehen geeignet ist, um diese Werte zu realisieren.

Als Benchmark nutzte das Team Dual-Gate-Bausteine, die aus kleinen, auf natürliche Weise expandierten, WS2-Flakes bestehen. Bei diesen im Labormaßstab hergestellten Bausteinen wurden für die Ladungsträgermobilität Werte >100 cm2/Vs gemessen. Das liegt dicht am theoretisch vorausgesagten Wert für die Ladungsträgermobilität für WS2. Die Forscher gehen davon aus, dass derartige Werte auch mit künstlich hergestellten Werkstoffen erreichbar sind. Diese liegen gegenwärtig bei nur einigen cm2/Vs. Die Wissenschaftler arbeiten an der Optimierung der Prozesse.

Fazit: Den Forschern ist es gelungen, das 2D-Material auf ein Ziel-Substrat wie einen 300-mm-Wafer abzuscheiden und zu transferieren, wobei es einen klaren Prozess gibt. Das Gate-Dielektrikum lässt sich verkleinern und die intrinsische Ladungsträgermobilität im Kanal verbessern.

Trotzdem müssen noch einige Probleme bei der Prozessintegration gelöst werden, die weitere Untersuchungen und ein besseres Grundlagenverständnis bedingen. Dazu gehören die schlechte Adhäsion der 2D-Werkstoffen auf dem Wafer und die Steuerung der Schwellspannung.

Die Lösung dieser Herausforderungen wird viele der Applikationen ermöglichen, die für die 2D-Materialien prognostiziert werden – extrem verkleinerte Hochleistungsbausteine und gleichzeitig Applikationen mit geringerer Stromaufnahme.

Die hier beschriebenen Arbeiten sind das Ergebnis der Zusammenarbeit zwischen dem IMEC-Forschungsteam für Bauelemente und dem IMEC-Team zur Entwicklung von Werkstoffen für Nano-Applikationen.

:quality(80)/images.vogel.de/vogelonline/bdb/1660200/1660260/original.jpg)

MOSHEMT: Neuartige Transistortechnik erreicht Grenzfrequenzen von 640 GHz

* Iuliana Radu leitet die Forschungen „Beyond CMOS and Quantum Computing“ am IMEC in Löwen / Belgien.

(ID:46292207)

:quality(80)/p7i.vogel.de/wcms/f5/5e/f55e737a7d227f2d048c579cab8e6985/0130834955v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/33/b4/33b4ab2c6baf7bd98f6f31747f105ab7/0130823277v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/96/97/96978cf39fdc205e816e3218f39499e5/0130663068v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/37/59/37594ae9b98dc4acb8eeab90c835c984/0131089404v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/39/2b/392b7f42b33965cee9d46984d8e1c021/0131069829v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/14/e8/14e887156fd8fb66138bfc7972c4cd3f/0131074909v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/2e/78/2e789ef76c84f5fcdf02b5697a22f9ab/0131062677v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d9/92/d9920f978cf2b03bb4f2b4e6cfbface3/0131055455v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d2/1c/d21cea8a73c1dc8b94322e896fb7cc2b/0131036508v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/be/81/be8197dbe5f61c3c5ade3732457725af/0131041847v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/0d/34/0d34c0b5b16676a55682e081ca59da32/0130890395v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/cc/bacc37befe18c7062ab18bdae3ea75c7/0131064254v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f2/fb/f2fb476fbd80a9145a022a4d162002df/0131122156v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/c5/42/c542a36bfc0e9beb119924d176f19e06/0131065166v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/d4/1d/d41d81ec84a42b4fd5d732d36d0021ce/0130877962v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9c/79/9c798ab2b4c18ba0a2c24f2491798d36/0130550888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/e7/b6e755d9e704319c0bb59dc1ac2d67e8/0130537290v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ca/8c/ca8cda9df29d8b2cf6f7b09abd8b7dda/0131065542v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/71/fa71d141fca285824eb23f3aba1333f2/0131012876v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e1/39/e13927f73987c9fb63d6f7145a597e6a/0130656559v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/87/b6/87b60368567da3c6b65107c55f5f69ec/0130689118v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b4/55/b455edd54c7e92e0f5bf2d059e2cc5ca/0130990400v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9b/96/9b96763092ce22624400387c5f264287/0130960582v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/82/71/8271e36a4b6aa180fa903edd1de396f1/0130907348v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1e/27/1e27744bed9341deb4f1d27d541e04e3/0131125212v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/96/e4/96e4b9434e4bb7b4e06cccc26e8a6497/0131080817v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ec/6b/ec6bb7201f5a2e41cd4942d59b23b999/0131074433v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/0a/350a177ef33b960e8f24c9be3717c653/0131061473v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ae/92/ae92a78425f17c6358d01ffd9b1c90ed/0131050297v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fc/5e/fc5e77b8434779834850aab40a903347/0131047752v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/43/c2439a5f7ecd10d2d7f02a4a5f38e97d/0131046056v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/9600/9682/65.jpg)

![Vergleich von Van-der-Waals- und Zipper-2D-Materialien: Struktur eines typischen vdW-Materials wie Bi₂O₂Se (alternativ: Molybdändisulfid oder Graphen) mit einem vdW-Spalt [Visualisierung (a)] und Struktur eines Zipper-Materials wie Bi₂SeO₂, das sich durch das Fehlen eines solchen Spalts in der Kristallstruktur und durch halb besetzte Oberflächen auszeichnet, postulieren Forscher der Peking-Universität [Visualisierung (b)]. (Bild: ACS Nano 2025, 19, 10, 9788-9800) Vergleich von Van-der-Waals- und Zipper-2D-Materialien: Struktur eines typischen vdW-Materials wie Bi₂O₂Se (alternativ: Molybdändisulfid oder Graphen) mit einem vdW-Spalt [Visualisierung (a)] und Struktur eines Zipper-Materials wie Bi₂SeO₂, das sich durch das Fehlen eines solchen Spalts in der Kristallstruktur und durch halb besetzte Oberflächen auszeichnet, postulieren Forscher der Peking-Universität [Visualisierung (b)]. (Bild: ACS Nano 2025, 19, 10, 9788-9800)](https://cdn1.vogel.de/00u4Ru7t3zOGgwVOUfjVTxfJfsc=/392x392/smart/filters:format(jpg):quality(80)/p7i.vogel.de/wcms/18/85/18856f727fff1ee9a0b57955a0f0b2b4/0125135007v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/87/b6/87b60368567da3c6b65107c55f5f69ec/0130689118v2.jpeg)