Analogtechnik Wie man die Tücken einer vermeintlich einfachen IC-Schnittstelle bekämpft

Schnittstellen gelten häufig als simpel und man schenkt ihnen wenig Beachtung. Das rächt sich meistens in der Endphase eines Projektes. In diesem Artikel lesen Sie die Geschichte darüber, wie eine nicht funktionierende Schnittstelle aus einem fröhlichen Entwickler-Gesicht ein trauriges machen kann.

Anbieter zum Thema

Gegenstand dieses Artikels ist ein häufig anzutreffender SPI-Fehler, dem man bei komplexen Systemen nur sehr schwer beikommt. Es wird erörtert, inwiefern Störsignale Systemprobleme hervorrufen können, und es wird auf ICs mit verminderter Störsignalanfälligkeit hingewiesen. Weiterhin werden die Vor- und Nachteile einer I2C-Systemimplementation sowie die grundlegende Funktionsweise der GPIO-Schnittstelle eines Mikroprozessors erläutert.

Gebräuchliche IC-Schnittstellen sind u.a. SPI, I2C und GPIO. Notwendige Voraussetzung für ein erfolgreiches Design ist eine funktionierende Schnittstelle zwischen den Peripherie-ICs und dem Mikrocontroller oder der CPU. Doch weil diese Schnittstellen landläufig als simpel oder gar primitiv gelten, schenkt man ihnen oft zu wenig Beachtung.

Die Zeit und Arbeit, die man dadurch in der Frühphase eines Projekts einspart, kann einen Entwicklungsingenieur glücklich machen... zumindest für den Augenblick. Diese Situation erinnert an den fröhlich dreinblickenden „Smiley“, der einem heutzutage auf Schritt und Tritt begegnet [1] und der hier als Metapher dient.

Vergessen Sie niemals Murphys Gesetz

Das „traurige“ Gesicht befällt den Entwicklungsingenieur in der Regel erst in der Spätphase des Projekts, wenn ihm Murphys Gesetz [2] – nachdem „alles, was schief gehen kann, auch schief gehen wird und zwar dann, wenn man es am wenigsten gebrauchen kann“ – betrifft. Dieser Artikel berichtet eine Episode, wie sie gar nicht so selten vorkommt. Es ist die Geschichte darüber, wie eine nicht funktionierende Schnittstelle aus einem fröhlichen Gesicht ein trauriges machen kann.

Funktionsweise des SPI-Busses

Der von Motorola entwickelte Serial Peripheral Interface Bus, oder SPI (ausgesprochen wie das englische Wort für Spion, „spy“) ist ein synchroner, serieller Vollduplex-Datenbus [3]. Die daran angeschlossenen Geräte kommunizieren im Master/Slave-Modus, wobei der Master den Daten-Frame initiiert.

Am Bus können mehrere Slaves hängen, die über Chip-Select-Leitungen adressiert werden. Gelegentlich wird SPI auch „serieller Dreidraht-Bus“ genannt (wenn nur Daten vom Master zum Slave und nicht in umgekehrter Richtung übertragen werden) oder „serieller Vierdraht-Bus“ [4]. Zur Vermeidung von Erdschleifen lässt sich eine SPI-Schnittstelle (Datenübertragung ausschließlich vom Master zum Slave) auf einfache Weise galvanisch trennen. Die galvanische Trennung kann durch Optokoppler, Kondensatoren oder Übertrager erfolgen.

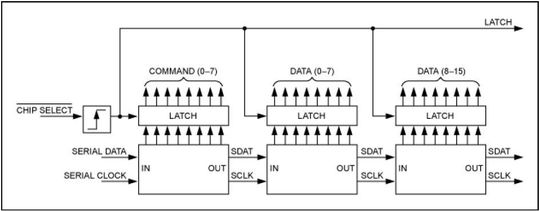

Der erste Fehler, den einige Entwickler machen, ist anzunehmen, ein SPI-Bus sei intelligent. Dem ist nicht so. Bild 1 zeigt, wie ein SPI-Slave funktioniert; der Datenempfänger ist nichts anderes als ein simples Schieberegister mit einem seriellen Eingang und einem parallelen Ausgang.

Der SPI-Bus ist „dumm“

Man kann nicht deutlich genug darauf hinweisen, dass ein SPI-Bus „dumm“ ist und nicht einmal eine einfache Fehlerprüfung durchführt. Es handelt sich im Wesentlichen um eine Kette aus Registern, in die Daten seriell eingeschrieben werden. Wenn die Chip-Select-Leitung gesetzt wird, wird das Register ausgelesen und ein paralleles Datenwort an den Chip übergeben. Die SPI-Bits an sich haben keine Bedeutung im Sinne eines Protokolls. Eine Nachricht muss nicht einmal aus einer bestimmten Anzahl von Bits bestehen; es werden immer so viele Bits übertragen, wie der jeweilige Slave benötigt.

Die Situation wird aus der Sicht des Entwicklers noch dadurch verkompliziert, dass mehrere Slave-Geräte unterschiedlicher Art und von unterschiedlichen Herstellern in einer Daisy-Chain-Konfiguration betrieben werden können. Natürlich müssen alle diese Geräte die gleiche Taktfrequenz und die gleichen Datenbeziehungen (einen der vier zur Auswahl stehenden „Modes" [3]) verwenden.

Stellen Sie sich jetzt drei Slave-Chips in einer Daisy-Chain-Konfiguration vor. Chip 1 „sieht“ zunächst eine Reihe von Befehlen „vorbeiziehen“, die für Chip 3 bestimmt sind, danach eine Reihe von Befehlen, die für Chip 2 bestimmt sind. Die Chip-Select-Leitung eines Chips wird erst dann gesetzt, wenn der für diesen Chip bestimmte Befehl in das Register eingeschrieben wurde. Dann, und nur dann, hat ein Befehl für einen der Chips – nämlich für den per Chip-Select adressierten – eine Bedeutung.

Komplexe Systeme mit stark ausgelasteten SPI-Bussen

Bei komplexen Systemen mit stark ausgelasteten SPI-Bussen kann es vorkommen, dass infolge eines Prozessor-Interrupts unvollständige SPI-Befehle gesendet werden; dies hat fatale Folgen. Man stelle sich vor, dass die ersten paar Bits eines Befehls in die ersten Zellen des SPI-Schieberegisters geschrieben werden und dann, bevor die Bits sich an der richtigen Registerposition befinden, die Chip-Select-Leitung gesetzt wird.

Der (unsinnige) Inhalt des Schieberegisters wird dann als paralleles Datenwort an den Chip übergeben. Um zu vermeiden, dass unvollständige SPI-Befehle gesendet werden, ist es unbedingt erforderlich, Prozessor-Interrupts während der Ausgabe von SPI-Befehlen zu maskieren.

Wir wollen die ordnungsgemäße Arbeitsweise einer SPI-Schnittstelle am Beispiel eines 12-Bit-D/A-Wandlers MAX5312 von Maxim Integrated illustrieren.

Wie aus den Tabellen 1 und 2 ersichtlich ist, wird das höchstwertige Bit (MSB, Most Significant Bit) als erstes und das niedrigstwertige Bit (LSB, Least Significant Bit) als letztes in das Schieberegister eingeschrieben. Die ersten vier Bits sind Befehlsbits, die übrigen Bits sind Datenbits. Wie Bild 2 zeigt, wird der 4-Bit-Befehl als erstes gesendet. Mit 4 Bit lassen sich insgesamt 16 Befehle codieren, wovon jedoch nur sechs „gelistet“ sind und verwendet werden sollen. Es wird davor gewarnt, nicht gelistete Befehle zu verwenden.

Auf nicht gelistete Befehle kann ein Slave-Chip reagieren oder auch nicht. Auf jeden Fall kann man nicht sicher sein, dass etwas Gutes dabei herauskommt. Ganz im Gegenteil – wahrscheinlich kommt etwas Verhängnisvolles dabei heraus. Deshalb sollte man die Verwendung nicht gelisteter Befehle vermeiden [5]. Der MAX5312 besitzt außerdem Schmitt-Trigger-Eingänge um die Störsignalanfälligkeit zu minimieren.

(ID:42439178)

:quality(80)/p7i.vogel.de/wcms/f5/5e/f55e737a7d227f2d048c579cab8e6985/0130834955v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/33/b4/33b4ab2c6baf7bd98f6f31747f105ab7/0130823277v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/96/97/96978cf39fdc205e816e3218f39499e5/0130663068v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/37/59/37594ae9b98dc4acb8eeab90c835c984/0131089404v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/39/2b/392b7f42b33965cee9d46984d8e1c021/0131069829v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/14/e8/14e887156fd8fb66138bfc7972c4cd3f/0131074909v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/2e/78/2e789ef76c84f5fcdf02b5697a22f9ab/0131062677v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d9/92/d9920f978cf2b03bb4f2b4e6cfbface3/0131055455v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d2/1c/d21cea8a73c1dc8b94322e896fb7cc2b/0131036508v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/be/81/be8197dbe5f61c3c5ade3732457725af/0131041847v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/0d/34/0d34c0b5b16676a55682e081ca59da32/0130890395v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/cc/bacc37befe18c7062ab18bdae3ea75c7/0131064254v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f2/fb/f2fb476fbd80a9145a022a4d162002df/0131122156v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/c5/42/c542a36bfc0e9beb119924d176f19e06/0131065166v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/d4/1d/d41d81ec84a42b4fd5d732d36d0021ce/0130877962v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9c/79/9c798ab2b4c18ba0a2c24f2491798d36/0130550888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/e7/b6e755d9e704319c0bb59dc1ac2d67e8/0130537290v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ca/8c/ca8cda9df29d8b2cf6f7b09abd8b7dda/0131065542v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/71/fa71d141fca285824eb23f3aba1333f2/0131012876v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e1/39/e13927f73987c9fb63d6f7145a597e6a/0130656559v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/87/b6/87b60368567da3c6b65107c55f5f69ec/0130689118v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b4/55/b455edd54c7e92e0f5bf2d059e2cc5ca/0130990400v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9b/96/9b96763092ce22624400387c5f264287/0130960582v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/82/71/8271e36a4b6aa180fa903edd1de396f1/0130907348v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1e/27/1e27744bed9341deb4f1d27d541e04e3/0131125212v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/96/e4/96e4b9434e4bb7b4e06cccc26e8a6497/0131080817v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ec/6b/ec6bb7201f5a2e41cd4942d59b23b999/0131074433v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/0a/350a177ef33b960e8f24c9be3717c653/0131061473v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ae/92/ae92a78425f17c6358d01ffd9b1c90ed/0131050297v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fc/5e/fc5e77b8434779834850aab40a903347/0131047752v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/43/c2439a5f7ecd10d2d7f02a4a5f38e97d/0131046056v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/5f/15/5f157c2d880f4/ish-logo2020.jpg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/111200/111228/65.jpg)

:quality(80)/images.vogel.de/vogelonline/bdb/661000/661036/original.jpg)

:quality(80)/images.vogel.de/vogelonline/bdb/661000/661037/original.jpg)

:quality(80)/images.vogel.de/vogelonline/bdb/661000/661038/original.jpg)

:quality(80)/p7i.vogel.de/wcms/1d/18/1d1807aec6b9e7153e108d66f5dd2aff/0127093609v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/16/f5/16f53e7661525c7f1c4db7a75de9cec1/0130519539v2.jpeg)