Anbieter zum Thema

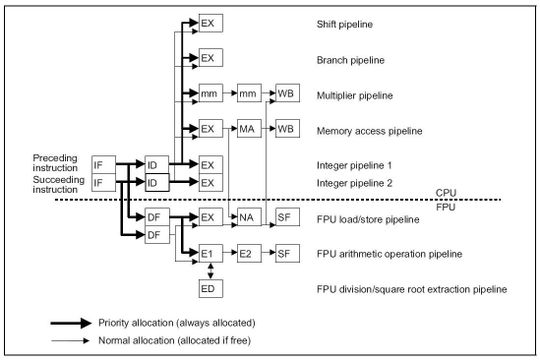

Ebenfalls zu beachten ist, dass die FPU des SH2A-Cores im Unterschied zu anderen Systemarchitekturen keine externe Einheit ist. Bei anderen Core-Architekturen ist die FPU als externe Einheit konfiguriert, an die Tasks übergeben werden und bei der die CPU auch diese Befehlsübergabe kontrollieren muss. Die FPU des SH2A ist Teil der Pipeline des Cores und arbeitet auch dementsprechend. Daher gibt es bei FPU-Operationen keinen Overhead für „Task Handling“. Dies lässt sich im Blockschaltbild der SH7216-Pipeline erkennen (Bild 1).

Die Kombination eines schnellen Rechenkerns und einer integrierten FPU bedeutet, dass Systementwickler bei digitalen Signalverarbeitungsfunktionen eine Standard-MCU anstelle eines weniger benutzerfreundlichen DSP verwenden können. Außerdem besitzt der SH2A eine Befehlslänge von 16 Bit und arbeitet mit einer Datenbusbreite von 32 Bit. Diese Kombination ergibt eine besonders gute Codedichte für einen echten 32-Bit-Baustein.

IRQ-Reaktionszeit

Ein weiteres Merkmal des SH2A-Cores ist seine kurze Interrupt-Latenzzeit. Die Leistung industrieller Anwendungen hängt nicht nur davon ab, wie schnell ein bestimmter Algorithmus sich ausführen lässt, sondern auch davon, wie schnell die MCU auf Befehle oder Eingangssignale reagieren kann. Dies erfordert eine schnelle Interrupt-Reaktionszeit.

In einer typischen Standard-CPU-Architektur besteht die erste Aufgabe vor der Ausführung einer Interrupt-Serviceroutine im Abspeichern des Kontexts für die aktuelle Task. Dabei wird der Inhalt sämtlicher interner Register in den Stack verschoben. Ist die Task anschließend beendet, werden die Registerinhalte aus dem Stack zurückgelesen, sodass die vorherige Task fortgesetzt werden kann.

Beim SH2A sind keine Stackoperationen erforderlich. Er enthält 15 zusätzliche Registerbänke, und anstelle eines Stacks ist einfach ein anderer Registersatz verwendbar. Infolge kann der SH2A innerhalb von nur 30 ns auf einen Interrupt-Befehl reagieren.

MONOS-Flash-Speicher

Der dritte, für die Rechenleistung relevante Aspekt nach der Interrupt-Latenzzeit und der CPU-Taktrate ist die Zugriffszeit des Flash-Speichers. Eine schnelle CPU zu haben ist schön und gut; wenn diese jedoch ständig darauf wartet, bis Daten aus dem Speicher abgerufen sind, dann spielt die Taktrate nur noch eine untergeordnete Rolle. Auf dem Markt gibt es Beispiele für Speicher, die bis zu einem Fünftel der Geschwindigkeit des CPU-Kerns arbeiten. Dabei sind während des Betriebs Wartezyklen erforderlich, oder im schlimmsten Fall muss Code in das RAM kopiert und von dort ausgeführt werden. Bei der SuperH-Familie ist dies kein Problem.

(ID:331803)

:quality(80)/p7i.vogel.de/wcms/37/ec/37ece4c276f37114e8f40696ff5dcd66/0130537789v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/46/7c/467c0afffbfd10c3553c2888a4a6289f/0130479810v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/12/3d/123d9eb2c2e4ce13296371a2ad3718a4/0130412664v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/e7/b6e755d9e704319c0bb59dc1ac2d67e8/0130537290v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/8b/10/8b10d1edceb749de99c1df3ad97be01e/0130564619v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ac/da/acda3bafe46d3bf8e104a2a7bc2ac557/0130535476v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ca/9b/ca9b681785123f9700518a46897f9779/0130428786v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/38/cb/38cbe19e814dd30b94780bc3946547ab/0130446533v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/88/c28805ea7b2261235475146a5b0c61f8/0130313028v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/8d/fa8dedee195f29c33c89d86311c258ee/0130104146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/7a/697a270ed7538378d1fbc0f0b240ed25/0130534691v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/e7/a4/e7a4e048491e60cb30e22a860f5d68bc/0130519425v4.jpeg)

:quality(80)/p7i.vogel.de/wcms/1b/f0/1bf02d41e3eac721823841a4c1228753/0130519149v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1a/53/1a539631c940d184689460600bd2b395/0130410666v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/10/45/1045969e69a1db4aaa73d0f74f55cc02/0129962687v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/e4/bae4e54395e5a53088060531ef99b814/0130359274v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/af/35af7dd326d198475d06fbb69aa600b5/0130175971v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/2e/c02e7bf72bfc434888c37100e2511681/0130127767v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/8c/42/8c4211320be4a5ef78ca36d37b2406f2/0130561321v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e1/0b/e10bc04827e33786548587e32bbae422/0130438700v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/06/3506f2a8d33a696aaef12a30771bd8d8/0130496747v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/ed/e5ed08c670c44565a9130e95a760dddc/0130494578v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/34/6d/346d110316228e54143f67e9f273972b/0130589338v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/7a/c07aaa9f6122aeb6faed4f2a74dcb77f/0130542642v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/3a/72/3a722ed2ad6ac4894c352e6ce87b6560/0130567207v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e9/19/e919aaa1fb20114acd7f56479d9d6c0d/0130599660v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1c/33/1c3399d0f7fb55bda7808310088accaf/0130565746v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/2e/95/2e9597b5dc1873771c7fe9c32ac41e82/0130549010v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/15/56/15564dea31861c376a385658c3b961a3/0130465243v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/61/a8/61a8d8e6ca4c2/glyn-logo-profilbild.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/60/b6/60b601af20368/et-system-logo-rgb.png)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/72000/72046/65.jpg)

:quality(80)/p7i.vogel.de/wcms/9d/77/9d7789cc1ce06fe8f93ce1071653601f/0125010031v4.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)