Fraunhofer IMS: Vertrauenswürdige eingebettete KI mit RISC-V

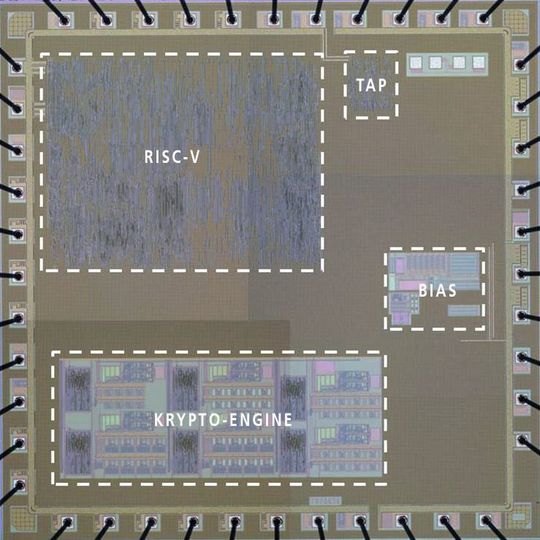

Auf Basis der freien Befehlssatzarchitektur RISC-V entwickelte das Fraunhofer Institut für Mikroelektronische Schaltungen und Systeme einen Prozessor, der eine vertrauenswürdige eingebettete Künstliche Intelligenz möglich macht. Eine eigene Kryptoeinheit sorgt dabei für Sicherheit.

Anbieter zum Thema

Wissenschaftlerinnen und Wissenschaftlern des Fraunhofer Instituts für Mikroelektronische Schaltungen und Systeme (IMS) haben einen leistungsfähigen Mikrocontroller-Kern auf Basis der freien und quelloffenen RISC-V Befehlssatzarchitektur entwickelt und diesen um eine Hardwarebeschleunigung für Anwendungen der Künstlichen Intelligenz (KI) erweitert. „Zusammen mit unserem AIfES-Framework für embedded KI haben wir damit ein System für den Einsatz von künstlicher Intelligenz auf sensor- beziehungsweise aktornahen eingebetteten Systemen ermöglicht,“ erklärt Alexander Stanitzki, der zuständige Gruppenleiter für Mixed-Signal ICs am Fraunhofer IMS.

Das AIfES-(AI for Embedded Systems-)Framework für diesen Prozessor wurde dabei mit einem Hardware/Software-Co-Design-Ansatz passend zum RISC-V-Kern entwickelt. Letzterer wurde dann für die Prototypenerstellung und Leistungsabschätzung auf einem FPGA als Softcore implementiert. Die Optimierung der Chipfläche und der Energieaufnahme bezüglich der Programmgröße und der Performance erfolgte anschließend in einem ASIC-Workflow, wobei sowohl das FPGA-Softcore als auch der ASIC aus derselben Codebasis erzeugt wurden. Zusätzlich zum AIfES-Framework arbeitet das Fraunhofer IMS an einer Portierung von Tensorflow Lite, einer quelloffenen Bibliothek für tiefes Maschinelles Lernen.

Verschiedene Aktivierungsfunktionen werden unterstützt

Verwendet wird beim Prozessorkern eine Untermenge der RISC-V Standarderweiterung für Vektoroperationen (V). Diese wurde auf wenige notwendige Vektorlängen und Datentypen reduziert, um die bei klassischen Neuronalen Netzwerken häufig vorkommenden Vektor- und Matrixmultiplikationen effektiv zu unterstützen. Für verschiedene Aktivierungsfunktionen wie Sigmoid und ReLu (Rectifier Linear Unit) kommen beschleunigte Befehle zum Einsatz, die über ein Coprozessor-Interface zuschaltbar sind, wie es ähnlich im PicoRV32 Verwendung findet.

Zuverlässige Verschlüsselung der Daten

Zum Schutz der KI-Algorithmen und Lerndaten vor einem Diebstahl geistigen Eigentums können die Chips mit einer hardwareseitigen Firmware-Verschlüsselung ausgestattet werden. Die Prozessoren schützen hierbei ihren Speicherinhalt mittels einer eingebauten Kryptoeinheit gegen Zugriffe von außen. Die sicheren Schlüsselspeicher basieren dabei auf sogenannten „Physical Unclonable Functions“ (PUF). Bei diesen werden die statistischen Fertigungsschwankungen spezieller Strukturen im Chip ausgewertet und für die Erzeugung kryptographischer Schlüssel verwendet. Diese können als eine Art Silicon-ID dienen, also als eine bei der Herstellung automatisch entstehende eindeutige Kennzeichnung des Prozessors. Darüber hinaus sind die integrierten PUFs parametrisierbar und sind daher auch in Challenge-Response-Verfahren einsetzbar.

Für die Kommunikation bieten die Chips eine Hardware-Beschleunigung für die populärsten Verschlüsselungsverfahren. Dazu implementierten die Wissenschaftler die XCrypto Befehlssatzerweiterung. Diese speziell auf software-basierte kryptographische Verfahren ausgelegte und nicht standardisierte Erweiterung besitzt den Vorteil einer klaren Trennung zwischen dem sicherheitsrelevanten Architekturteil mit eigenem Registersatz und gegebenenfalls eigenem Speicherinterface und dem Standard-Datenpfad.

Der modulare Aufbau des Prozessorkerns ermöglicht zudem eine geringe Energieaufnahme. Damit ist er in integrierten Sensor-ICs einsetzbar und kann dort einerseits Aufgaben wie Anomalieerkennung, Regressionsanalysen oder Klassifizierungen übernehmen, aber auch als Ersatz für klassische Regler dienen.

Softcores sind bereits verfügbar

Das Fraunhofer IMS erweitert mit dieser Entwicklung sein Angebot für vertrauenswürdige Hardware (Trusted Electronics) auf den Bereich der eingebetteten Künstlichen Intelligenz und setzt dabei auf offene Standards wie RISC-V. Für die Evaluierung kann das IMS Softcores für diverse FPGA-Plattformen sowie optimierte Software-Bibliotheken zur Verfügung stellen. Chips sind ab dem Frühjahr 2020 verfügbar und die Integration in kundenspezifische ASIC-Entwicklungen ist ab sofort möglich. Dies beinhaltet die Option, den RISC-V-Kern um eigene Module zu erweitern.

:quality(80)/images.vogel.de/vogelonline/bdb/1414700/1414702/original.jpg)

Wie funktioniert RISC-V? Grundlagen der offenen Befehlssatzarchitektur

:quality(80)/images.vogel.de/vogelonline/bdb/1575100/1575188/original.jpg)

Maschinelles Lernen direkt auf dem eingebetteten System

:quality(80)/images.vogel.de/vogelonline/bdb/1441300/1441329/original.jpg)

RISC-V-Kerne für sichere und intelligente Anwendungen

(ID:46185912)

:quality(80)/p7i.vogel.de/wcms/9f/13/9f13686bb894142875a93de7f6c3aabe/0131278942v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e1/9c/e19ca48e7ee7b6604240bdb1a02a3a7d/0131251245v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/8c/f0/8cf0a380137d81e18ab1683a061b7531/0131171547v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/40/00/4000cee04363c2ad502a5cfadded2e0e/0131287222v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/4b/c1/4bc195078a1cc19f3f42f3fdea3cc8c5/0131260433v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/42/65/426590889d9cc3c850ba2ed6184b28d8/0131183751v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/17/71/1771c0b139e32eced60c0f60abd045dc/0131202175v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ab/6e/ab6ee4358adb3ef565a3af4e923dae6b/0131202314v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a0/b7/a0b74e201c3d9a12af0a204e1e578aad/0131136338v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d2/1c/d21cea8a73c1dc8b94322e896fb7cc2b/0131036508v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/be/81/be8197dbe5f61c3c5ade3732457725af/0131041847v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/5b/f2/5bf2fc2e46775b70614326a4003940ea/0131238162v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/58/ed/58ede6960020a2ded5f6771bd9b8e49d/0131277913v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/77/06/77065703c81be2dd11397359059b74ca/0131276872v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/2e/78/2e789ef76c84f5fcdf02b5697a22f9ab/0131062677v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d4/1d/d41d81ec84a42b4fd5d732d36d0021ce/0130877962v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9c/79/9c798ab2b4c18ba0a2c24f2491798d36/0130550888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/e7/b6e755d9e704319c0bb59dc1ac2d67e8/0130537290v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/aa/79/aa79a807ba1ce61e6656226679e05f9c/0131288690v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/34/1f/341f0c9b899c7509a01c9a13383af6cf/0131148001v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ca/8c/ca8cda9df29d8b2cf6f7b09abd8b7dda/0131065542v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/c2/35c2b1da065361aefeea668c786531c9/0131280558v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/05/83/0583267ea76f0beb94c4acef52d485e1/0130855074v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b5/54/b5548923d20a751319550a3eb159af21/0131159519v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/87/b6/87b60368567da3c6b65107c55f5f69ec/0130689118v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/7d/5b/7d5bd7b3575dd8745fac17cf8619a7c2/0131253052v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/94/82/948296f1541e8d3b2060978cfeae90e8/0131311058v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/42/fa424fa7fe94e1ba17869e270e2b2422/0131203375v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/19/75/1975839f578e6bed7a0db82789cd96a4/0131312221v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/66/f6/66f673630a98a/logo-mc-rgb-300x300.png)

:fill(fff,0)/p7i.vogel.de/companies/65/f1/65f186172d9f0/syslogic-logotype-alt-navy-mint.jpeg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/9700/9772/65.jpg)

:quality(80)/images.vogel.de/vogelonline/bdb/1629300/1629307/original.jpg)

:quality(80)/images.vogel.de/vogelonline/bdb/1629300/1629308/original.jpg)

:quality(80)/p7i.vogel.de/wcms/5b/38/5b382b49e01304dce57931fd9b3852c4/0126789537v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/88/c28805ea7b2261235475146a5b0c61f8/0130313028v2.jpeg)