Neues Konsortium mit Intel, AMD und Arm UCIe: Offener Chiplet-Standard für heterogene Integration

Kleine Chips, großes Vorhaben: AMD, Arm, ASE, Google, Intel, Meta (Facebook), Microsoft, Qualcomm, Samsung und TSMC bringen eine offene Spezifikation für die Integration von Chiplets auf die Schiene – Universal Chiplet Interconnect Express (UCIe). Ein standardisiertes, offenes Chiplet-Ökosystem könnte die heterogene Chipintegration enorm beflügeln.

Anbieter zum Thema

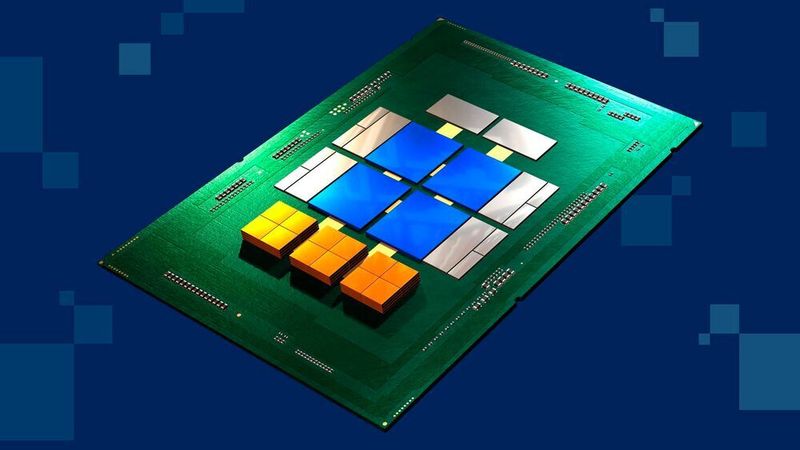

Monolithisch integrierte Chips stoßen immer mehr an ihre Grenzen. Daher gewinnen seit einigen Jahren sogenannte Chiplets bei der Halbleiterherstellung an Bedeutung: Auf ein Substrat integrierte Schaltungen mit einer begrenzten Funktionalität. Anstatt die Gesamtschaltung eines Chips auf einem einzigen Substrat zu integrieren, baut man diesen aus mehreren „Building Blocks“ zusammen: den Chiplets. Der Ansatz geht über bisherige, gebondete Multi-Chip-Module (MCM) hinaus, da die Verbindungen direkt auf Chip-Level erfolgen. Die Idee ist nicht neu, gewinnt mit verfeinerten Verbindungs- und Verpackungstechniken (Interconnect und Packaging) jedoch immens an Schwung.

Theoretischer Vorteil: Chiplet-basierte Systeme ermöglichen die heterogene Integration verschiedener Substratmaterialien und Prozesstechnologien (Si, InP, GaAs, SiGe, GaN usw.), was bei einem monolithischen SoC-Ansatz nicht möglich ist. So lassen sich etwa DRAM-, GPU-, CPU-, DSP- und I/O-Logikmodule zu einem System-on-Package (SoP) vereinen. Auch die Erweiterung mit analogen Funktionen zu einem Mixed-Signal-SoP ist möglich.

Aufbau der Schnittstellen ist nicht trivial

In der Praxis gibt es jedoch einige Hürden zu überwinden. So spielen die winzigen Schnittstellen, die die einzelnen Siliziumplättchen miteinander verbinden, eine besondere Rolle. Ihre Ausführung ist nicht trivial und hat direkte Auswirkungen auf wichtige elektrische Parameter wie Signallaufzeiten, Signalintegrität und Jitter – und damit auf die Leistungsfähigkeit der Gesamtschaltung.

Grundsätzlich lassen sich die Dies sowohl planar kombinieren als auch übereinander anordnen („stacken“). Jede Bauart erfordert spezielle Verbinder, die Interposer. Ein Interposer ist ein (meist) passives Bauteil, aufgrund der hohen Integrationsdichte jedoch nicht einfach zu fertigen. Bislang kocht jeder Anbieter sein eigenes Süppchen, etwa Intel mit Embedded Multi-Die Interconnect Bridge (EMIB) und verschiedene Foveros-Versionen oder TSMC mit TSMC-SoIC und CoWoS (Chip-on-Wafer-on-Substrate).

UCIe: Offener Standard für das Verbinden von Chiplets

Doch proprietäre Herangehensweisen bremsen Innovationen eher aus. Daher haben sich nun mehrere namhafte Chip- und Gehäuseentwickler mit Halbleiterherstellern und Cloud-Service-Anbietern zusammengetan, um einen Standard für Chiplets zu entwickeln: den Universal Chiplet Interconnect Express, kurz UCIe. UCIe soll Endbenutzer in die Lage versetzen, Chiplet-Komponenten einfach mischen und anpassen zu können.

Wohl nicht ganz zufällig und nicht nur phonetisch ist die Anlehnung an den Peripheral Component Interconnect Express (PCIe), den heute sehr verbreiteten Schnittstellenstandard für Erweiterungskarten in Computer-Systemen. Tatsächlich basiert UCIe auf den Industriestandards PCI Express (PCIe) und Compute Express Link (CXL).

Im UCIe-Konsortium arbeiten bislang AMD, Arm, Advanced Semiconductor Engineering (ASE), Google Cloud, Intel, Meta, Microsoft, Qualcomm Incorporated, Samsung und Taiwan Semiconductor Manufacturing Company (TSMC) an dem offenen Industriestandard. Ziel ist es nach eigenen Angaben, „ein globales Ökosystem zur Unterstützung des Chiplet-Designs aufzubauen“. Wie Kurt Lender, IO Technology Solution Team Strategist von UCIe-Initiator Intel, betont, „ist UCIe eine entscheidende Komponente der IDM 2.0-Strategie von Intel. Diese Spezifikation baut auf Intels offenem Advanced Interface Bus (AIB) Standard auf.“ Auffällig ist, dass Branchengröße NVIDIA bislang kein Teil des UCIe-Konsortiums ist.

UCIe 1.0 steht bereits in den Startlöchern

Während die Gruppe noch in diesem Jahr offiziell gegründet werden soll, ist Version 1.0 der UCIe-Spezifikation bereits fertig. Sie beschreibt eine standardisierte Die-to-Die-Verbindung mit physikalischer Schicht, Protokollstapel, Softwaremodell und Konformitätstests. Die physikalische Schicht ist dabei für die elektrische Signalisierung, die Taktung, das Link-Training und die Seitenbandverbindungen zuständig.

Der Die-to-Die-Adapter übernimmt das Verwalten des Verbindungsstatus und das Aushandeln der Parameter für die Chiplets. Er garantiert optional eine zuverlässige Datenübermittlung per zyklischer Redundanzprüfung (CRC) und über einen Wiederholungsmechanismus (Retry) auf Verbindungsebene. Wenn mehrere Protokolle unterstützt werden, definiert er den zugrunde liegenden Arbitrierungsmechanismus.

PCIe und CXL nativ abgebildet

Ein 256-Byte-FLIT (Flow Control Unit) definiert den zugrundeliegenden Übertragungsmechanismus. UCIe bildet PCIe- und CXL-Protokolle nativ ab. Ein Grund dafür ist, dass diese Protokolle in allen Segmenten der Datenverarbeitung auf Kartenebene weit verbreitet sind. Für Datentransfer mit direktem Speicherzugriff, Softwareerkennung und Fehlerbehandlung ist PCIe/CXL.io zuständig. Die Speichernutzung verwaltet CXL.Mem, während Caching-Anforderungen für Anwendungen wie Beschleuniger mit CXL.cache adressiert werden.

UCIe 1.0 definiert zwei Paketarten, eines für den Normalbetrieb, eines für einen Energieeffizienzbetrieb. Darüber hinaus ist ein „Streaming-Protokoll“ definiert: Darüber soll sich ein beliebiges anderes Protokoll abbilden lassen, das später Teil in die Spezifikation aufgenommen werden kann.

(ID:48095065)

:quality(80)/p7i.vogel.de/wcms/f5/5e/f55e737a7d227f2d048c579cab8e6985/0130834955v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/33/b4/33b4ab2c6baf7bd98f6f31747f105ab7/0130823277v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/96/97/96978cf39fdc205e816e3218f39499e5/0130663068v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/37/59/37594ae9b98dc4acb8eeab90c835c984/0131089404v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/39/2b/392b7f42b33965cee9d46984d8e1c021/0131069829v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/14/e8/14e887156fd8fb66138bfc7972c4cd3f/0131074909v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/2e/78/2e789ef76c84f5fcdf02b5697a22f9ab/0131062677v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d9/92/d9920f978cf2b03bb4f2b4e6cfbface3/0131055455v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d2/1c/d21cea8a73c1dc8b94322e896fb7cc2b/0131036508v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/be/81/be8197dbe5f61c3c5ade3732457725af/0131041847v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/0d/34/0d34c0b5b16676a55682e081ca59da32/0130890395v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b5/1e/b51e81eb4981b7ba1cf3adcd38d09802/0131130065v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/cc/bacc37befe18c7062ab18bdae3ea75c7/0131064254v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f2/fb/f2fb476fbd80a9145a022a4d162002df/0131122156v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/d4/1d/d41d81ec84a42b4fd5d732d36d0021ce/0130877962v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9c/79/9c798ab2b4c18ba0a2c24f2491798d36/0130550888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/e7/b6e755d9e704319c0bb59dc1ac2d67e8/0130537290v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ca/8c/ca8cda9df29d8b2cf6f7b09abd8b7dda/0131065542v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/71/fa71d141fca285824eb23f3aba1333f2/0131012876v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e1/39/e13927f73987c9fb63d6f7145a597e6a/0130656559v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/87/b6/87b60368567da3c6b65107c55f5f69ec/0130689118v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b4/55/b455edd54c7e92e0f5bf2d059e2cc5ca/0130990400v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9b/96/9b96763092ce22624400387c5f264287/0130960582v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/82/71/8271e36a4b6aa180fa903edd1de396f1/0130907348v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/49/76/4976fcd614ea458c165eb05744aec2fb/0131120525v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b0/d8/b0d8b5b7eeaed18fe805197c37cbbe14/0131086898v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1e/27/1e27744bed9341deb4f1d27d541e04e3/0131125212v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/15/3515d9038ba5f392dca4f98115fc0a04/0131078602v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ec/6b/ec6bb7201f5a2e41cd4942d59b23b999/0131074433v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fc/5e/fc5e77b8434779834850aab40a903347/0131047752v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/43/c2439a5f7ecd10d2d7f02a4a5f38e97d/0131046056v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/93300/93330/65.jpg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/68800/68851/65.jpg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/72000/72046/65.jpg)

:quality(80)/p7i.vogel.de/wcms/2e/b7/2eb712f6351a2abb0a606c1956cabc89/0124512500v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/1a/57/1a57ad7fd8644902e80238e3d31bdd2b/0126085586v2.jpeg)