Programmierbares Subsystem FPGA-in-a-SiP: Erstes System-in-Package mit Zynq UltraScale+-MPSoC

FPGA-Entwickler aufgepasst: Octavo Systems hat das Zynq UltraScale+-MPSoC von AMD/Xilinx in ein kleines BGA-System-in-Package integriert. Das kompakte Subsystem verspricht eine leichtere und damit schnellere Entwicklung programmierbarer Baugruppen.

Anbieter zum Thema

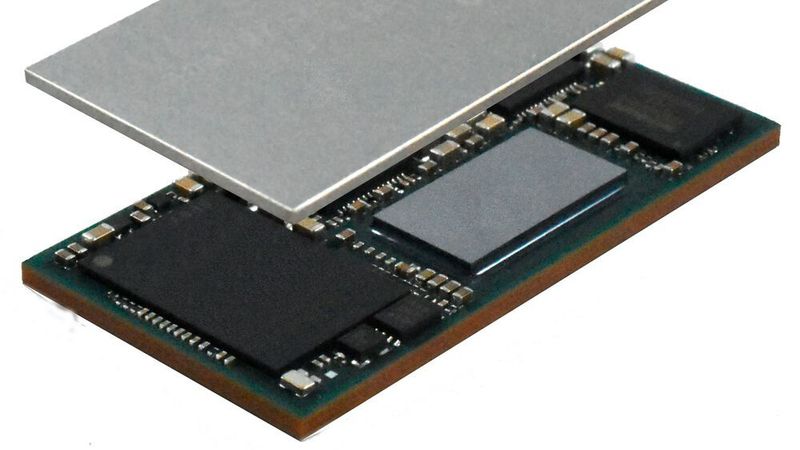

2016 hat der texanische Hersteller Octavo Systems einen AM335x-Controller von Texas Instruments als funktionsfähiges Prozessor-Subsystem in das kompakte System-in-Package (SiP) OSD335x integriert. 2020 folgte das OSD32MP1, ein SiP rund um den STM32MP15x von STMicroelectronics. Nun geht Octavo Systems einen Schritt weiter und baut ein programmierbares SiP auf Basis des Zynq UltraScale+-FPGA-MPSoCs ZU3 von AMD/Xilinx auf. Das komplette System sitzt in einem gut 2 cm x 4 cm kleinen Ball Grid Array (BGA) mit 600 Kontaktkügelchen. ELEKTRONIKPRAXIS sprach mit Greg Sheridan, Vice President Strategy and Marketing, und Eric Welsh, CTO von Octavo Systems über Details des interessanten Produkts.

Funktional entspricht ein SiP von Octavo Systems einem System-on-Module (SoM) – nur eben in einem stark miniaturisierten Formfaktor. Das Unternehmen packt die Komponenten so dicht, dass das gesamte Subsystem – Prozessor/FPGA, RAM, EEPROM, QSPI-Flash, Power Management, Taktgeber, Schnittstellen plus passive Komponenten – in ein BGA-Gehäuse passt. So lässt sich das SiP wie ein herkömmlicher Chip direkt in die eigene Schaltung integrieren.

Sofort loslegen versus langwieriges Schaltungsdesign

Die Vorteile liegen auf der Hand: Anstatt eine komplette Schaltung selbst designen zu müssen, „können Entwickler das abgestimmte, zuverlässig funktionierende Subsystem verwenden“, sagt Sheridan. Statt viele Ressourcen etwa mit dem Anbinden von oft zickigem LPDDR-RAM zu binden, könnte man eben diese nutzen, um die eigentlichen Unique Selling Points (USPs) des eigenen Produkts zu verbessern und sich so besser vom Wettbewerb zu differenzieren.

Denn während bereits das Schaltungsdesign rund um einen Mikrocontroller (MCU) kein triviales Unterfangen ist, potenziert der Einsatz eines Zynq UltraScale+-FPGA-MPSoCs ZU3 die Komplexität beim Eindesignen in eine eigene Schaltung. Schließlich bildet das MPSoC schon für sich ein umfangreiches Subsystem, das neben dem Logikzellen-Array mehrere Arm-Prozessoren (vier Cortex-A53- und zwei Cortex-R5-Kerne), eine Arm-Mali-400-GPU, Security-Subsystem, General-I/O und mehrere Hochgeschwindigkeitsschnittstellen auf einem Silizium-Die vereint.

ZU3-FPGA-MPSoC direkt als Siliziumchip verarbeitet

Diesen Teil der Entwicklungsarbeit, eben das Schaltungsdesign, nimmt Octavo Systems den Anwendern seiner SiPs ab. Das OSDZU3 ist aus insgesamt über 150 Bauteilen zusammengefügt. Und findet doch in einem BGA-Gehäuse mit 20,5 mm x 40 mm Grundfläche Platz findet. Damit das möglich ist, bezieht Octavo Systems die Silizium-Chips direkt von AMD/Xilinx und kontaktiert sie direkt „mit IC-Integrationstechniken“ auf die Miniaturplatine (bei den TI-/ST-basierten Produkten von Octavo Systems werden die Chips klassisch gebondet). So fällt das gesamte Gehäuse des ZU3-Bausteins weg.

Der Größenvorteil etwa gegenüber einem SoM wird im Vergleich der beiden Konzepte offensichtlich: Die Octavo Systems-Lösung ist nach eigenen Angaben rund 60 Prozent kleiner als ein funktional vergleichbares Systemdesign mit diskreten Komponenten – was im direkten Vergleich durchaus glaubwürdig erscheint. „Trotzdem können Anwender auf alle Funktionen des AMD/Xilinx-MPSoCs zugreifen – inklusive sämtlicher Schnittstellen und Betriebsmodi“, unterstreicht Erik Welsh.

Ein 5-V-Anschluss statt 13 Spannungskontakte

Ein Beispiel für die hohe Integrationskunst von Octavo Systems zeigt sich bei der Spannungsversorgung. Der ZU3 hat 13 unterschiedliche Spannungsanschlüsse, die Entwickler normalerweise beim Design eigener Boards ansteuern müssen. Octavo Systems fängt diese Komplexität mit seinem eigenen Power-Management ab: „Unser OSDZU3-SiP hat nur einen 5-V-Eingang“, sagt Sheridan. Stolz verweist er darauf, dass Anwender trotzdem alle Power-Modi „und die volle Performance“ des AMD/Xilinx-Bausteins nutzen können. Welsh versichert: „Der Verzicht auf die Entwicklung komplizierter Stromversorgungssysteme oder LPDDR-Anbindung hat einigen unserer Kunden mehr als neun Monate Entwicklungszeit erspart.“

Zudem habe man „beim Ball-Grid-Layout des Packages darauf geachtet, dass das Routing auf der Trägerplatine so einfach wie möglich ausfallen kann“, erklärt Sheridan. So sei der Abstand zwischen den 600 Ball-Kontakten (Ball Pitch) mit 1 mm bewusst relativ groß gehalten, damit zwischen ihnen Leiterbahnen von den weiter innenliegenden Kontakten herausgeführt werden können.

PCB-Routing mit Standard-Tools und-Regeln

Zudem sind die Signal-I/Os in zwei Kreisen um die innen liegenden Spannungs- und Masseanschlüsse herum angeordnet. „Dadurch lassen sich alle I/Os über eine Platine mit nur zwei Signalebenen ausführen. Dieser 2-Layer-Escape spart immens Kosten in der Produktion gegenüber mehrschichtigen Leiterplatten“, verdeutlich Sheridan. Da mit gewöhnlichen Leiterbahnmaßen gearbeitet werden könne, lasse sich das Routing der Trägerplatine mit einfachen Standard-Tools und -Regeln durchführen. Komplexe und teure Spezialanwendungen seien nicht nötig.

Als Proof-of-Concept haben die Octavo-Systems-Ingenieure die Funktionalität einer UltraZed PCIe-Karte von Avnet auf eine eigene Referenzplattform übertragen. Die Avnet-Grundkarte benötigt 6 Layer. Darauf sitzt, verbunden über einen vielpoligen Steckverbinder, ein ebenfalls sechslagiges SoM mit dem ZU3 – insgesamt also zwölf Layer. „Bei identischer Funktionalität kommt unsere OSDZU3-REF-Plattform mit nur vier Layern aus“, betont Welsh. Praktisch sämtliche Komponenten des SoMs sitzen bei der Octavo-Systems-Lösung im SiP.

Platine mit vier statt zwölf Layern reicht

Wie die Avnet-Karte führt das Octavo-Systems-Board mehrere häufig benutzte Schnittstellen nach außen, darunter USB-C, USB-Host, Display-Port, SATA-Host, FMC-LPC, LVDS Display und Touch und 1 Gigabit-Ethernet. Darüber hinaus ist wie beim Vorbild ein Steckverbinder für Erweiterungskarten vorhanden. Die vorinstallierte PetaLinux-Distribution enthält zudem Demos für einen schnellen Einstieg.

Entscheidend für die Integration des OSDZU3 ist, dass Entwickler gewohnte Tools und den Workflow für die FPGA-Programmierung und -Verifikation der ZU3-Bausteine auch für das SiP einsetzen können. „Für Tools wie Vivado Design Suite, Vitis und der Xilinx Power Estimator ist unsere Schaltung transparent“, sagt Sheridan.

Octavo Systems arbeitet mit Avnet als globalem Vertriebspartner bei der Einführung und Übernahme des neuen OSDZU3 System-in-Package als Franchise-Produkt zusammen. Die Texaner stellen derzeit technische Muster im Rahmen seines Beta-Programms zur Verfügung. Nach Angaben des Unternehmens soll die Referenzplattform im dritten Quartal 2022 für den allgemeinen Markt verfügbar sein, das OSDZU3 soll bis Ende des Jahres 2022 in Produktion sein.

(ID:48132349)

:quality(80)/p7i.vogel.de/wcms/f5/5e/f55e737a7d227f2d048c579cab8e6985/0130834955v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/33/b4/33b4ab2c6baf7bd98f6f31747f105ab7/0130823277v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/96/97/96978cf39fdc205e816e3218f39499e5/0130663068v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/37/59/37594ae9b98dc4acb8eeab90c835c984/0131089404v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/39/2b/392b7f42b33965cee9d46984d8e1c021/0131069829v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/14/e8/14e887156fd8fb66138bfc7972c4cd3f/0131074909v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/2e/78/2e789ef76c84f5fcdf02b5697a22f9ab/0131062677v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d9/92/d9920f978cf2b03bb4f2b4e6cfbface3/0131055455v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d2/1c/d21cea8a73c1dc8b94322e896fb7cc2b/0131036508v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/be/81/be8197dbe5f61c3c5ade3732457725af/0131041847v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/0d/34/0d34c0b5b16676a55682e081ca59da32/0130890395v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b5/1e/b51e81eb4981b7ba1cf3adcd38d09802/0131130065v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/cc/bacc37befe18c7062ab18bdae3ea75c7/0131064254v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f2/fb/f2fb476fbd80a9145a022a4d162002df/0131122156v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/d4/1d/d41d81ec84a42b4fd5d732d36d0021ce/0130877962v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9c/79/9c798ab2b4c18ba0a2c24f2491798d36/0130550888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/e7/b6e755d9e704319c0bb59dc1ac2d67e8/0130537290v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ca/8c/ca8cda9df29d8b2cf6f7b09abd8b7dda/0131065542v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/71/fa71d141fca285824eb23f3aba1333f2/0131012876v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e1/39/e13927f73987c9fb63d6f7145a597e6a/0130656559v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/87/b6/87b60368567da3c6b65107c55f5f69ec/0130689118v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b4/55/b455edd54c7e92e0f5bf2d059e2cc5ca/0130990400v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9b/96/9b96763092ce22624400387c5f264287/0130960582v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/82/71/8271e36a4b6aa180fa903edd1de396f1/0130907348v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/49/76/4976fcd614ea458c165eb05744aec2fb/0131120525v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b0/d8/b0d8b5b7eeaed18fe805197c37cbbe14/0131086898v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1e/27/1e27744bed9341deb4f1d27d541e04e3/0131125212v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/15/3515d9038ba5f392dca4f98115fc0a04/0131078602v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ec/6b/ec6bb7201f5a2e41cd4942d59b23b999/0131074433v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fc/5e/fc5e77b8434779834850aab40a903347/0131047752v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/43/c2439a5f7ecd10d2d7f02a4a5f38e97d/0131046056v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/67/d1/67d1a4da69c1f/b--rklin-logo-digital--002-.jpeg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/72000/72046/65.jpg)

:quality(80)/p7i.vogel.de/wcms/1a/53/1a539631c940d184689460600bd2b395/0130410666v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9f/08/9f08b9d1c0a5df23a9021ca459c38f57/0125206135v2.jpeg)