Leiterplatten-Entwicklung Optimiertes PCB-Tool OrCAD in der neuen Version 16.6-2015

Vor 30 Jahren wurden Leiterkarten derart komplex, dass manuelles Zeichnen oder Kleben der Schaltungen zu aufwändig war. Erste Software-Tools für das PCB-Design entstanden. Mit dabei: OrCAD.

Anbieter zum Thema

Bei FlowCAD und Cadence wurde 2015, aus Anlass der Jubiläen von OrCAD und dem Moore’schen Gesetz, die Zunahme der Design-Regeln für Leiterplatten untersucht. Auch hier konnte ein interessanter Zusammenhang festgestellt werden.

Die Anzahl von Design-Regeln, die in einem PCB Design vergeben werden, nimmt auch rasant zu und macht damit elektronische Schaltungen stetig komplexer. Es hat den Anschein, das auch für die Zahl der Design-Regeln das „elektronische Naturgesetz“ von Gordon Moore gilt. Passend zum 30. Geburtstag bringt Cadence Ende Juni ein neues Release (Version 16.6-2015) auf den Markt und bietet als wesentlichen Punkt die Möglichkeit, dass Anwender noch mehr und komplexere Design-Regeln übersichtlich eingeben und verwalten können.

Vor sechs bis acht Jahren waren Schaltungen mit 1 GHz Taktfrequenz noch die Seltenheit und konnten mit den Befehlen und Funktionen der Allegro-PCB-Plattform entwickelt werden. Allegro ist die höchste Ausbaustufe der skalierbaren PCB-Lösung von Cadence.

Heute sind Schaltungen von 1 GHz weit verbreitet; mit dem neuen Release fließen die erforderlichen Allegro-Eigenschaften in die OrCAD-Produkte und stehen damit dem Entwickler zur Verfügung.

So hat jetzt jede PCB-Design-Lizenz einen Signal Explorer, um die Topologien von elektrischen Signalen auf Signalintegrität zu untersuchen. Die integrierte SI-Simulation kann sowohl zum Entwickeln von Design-Regeln als zur SI-Prüfung mit realen Leitungslängen aus dem physikalischen PCB-Layout verwendet werden.

Virtuelle T-Punkte und Net-Scheduling

Bei heute verbreiteten High-Speed Anwendungen, etwa für DDR2-Speicher, ist es häufig erforderlich, einzelne Teilabschnitte von Netzen mit unterschiedlichen Regeln zu versehen. Über virtuelle T-Punkte lassen sich zusätzliche Verzweigungen (Sternpunkte) oder Teilabschnitte in einem elektrischen Netz definieren. Virtuell heißen sie T-Punkte, da sie nur zur Regeldefinition in ein Netz eingefügt aber im Layout nicht platziert werden.

:quality(80)/images.vogel.de/vogelonline/bdb/836000/836024/original.jpg)

Leiterplattenentwurf

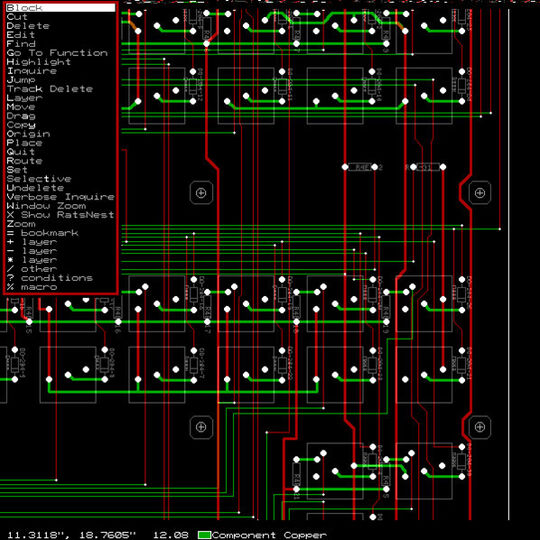

Komplexes Board-Design mit cleverem Constraint Manager

Im Layout wird online mit einem DRC geprüft, ob alle Regeln innerhalb der vorgegebenen Toleranzen eingehalten wurden. Den einzelnen Teilstücken der Leitung können unterschiedliche Design-Regeln wie eine minimale oder maximale Leitungslänge, unterschiedliche Impedanzen oder die Anzahl von Durchkontaktierungen zugeordnet werden.

Damit lassen sich die Regeln abbilden, die für High-Speed-Signale eingehalten werden müssen. Bei Regelverstößen bekommt der Anwender sofort eine optische Fehlermeldung, von der er direkt zur Regeldefinition im Constraint Manager springen kann.

Artikelfiles und Artikellinks

(ID:43392450)

:quality(80)/p7i.vogel.de/wcms/f5/5e/f55e737a7d227f2d048c579cab8e6985/0130834955v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/33/b4/33b4ab2c6baf7bd98f6f31747f105ab7/0130823277v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/96/97/96978cf39fdc205e816e3218f39499e5/0130663068v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/22/fa22ead6e6fe569ec03e08eba146bedc/0131141465v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/29/a0/29a0d3ad968ba9d262056d4f93073b9d/0131130383v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a1/2c/a12cd5489205b14b8ffda38315bd4d25/0131126505v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a0/b7/a0b74e201c3d9a12af0a204e1e578aad/0131136338v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/2e/78/2e789ef76c84f5fcdf02b5697a22f9ab/0131062677v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d9/92/d9920f978cf2b03bb4f2b4e6cfbface3/0131055455v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d2/1c/d21cea8a73c1dc8b94322e896fb7cc2b/0131036508v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/be/81/be8197dbe5f61c3c5ade3732457725af/0131041847v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/b5/1e/b51e81eb4981b7ba1cf3adcd38d09802/0131130065v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/cc/bacc37befe18c7062ab18bdae3ea75c7/0131064254v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d4/1d/d41d81ec84a42b4fd5d732d36d0021ce/0130877962v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9c/79/9c798ab2b4c18ba0a2c24f2491798d36/0130550888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/e7/b6e755d9e704319c0bb59dc1ac2d67e8/0130537290v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/34/1f/341f0c9b899c7509a01c9a13383af6cf/0131148001v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ca/8c/ca8cda9df29d8b2cf6f7b09abd8b7dda/0131065542v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/71/fa71d141fca285824eb23f3aba1333f2/0131012876v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b5/54/b5548923d20a751319550a3eb159af21/0131159519v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/87/b6/87b60368567da3c6b65107c55f5f69ec/0130689118v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b4/55/b455edd54c7e92e0f5bf2d059e2cc5ca/0130990400v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9b/96/9b96763092ce22624400387c5f264287/0130960582v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/49/76/4976fcd614ea458c165eb05744aec2fb/0131120525v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b0/d8/b0d8b5b7eeaed18fe805197c37cbbe14/0131086898v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/75/10/75102cf1bcc950d376da7fc4e9722ebe/0131066528v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/15/3515d9038ba5f392dca4f98115fc0a04/0131078602v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/41/e9/41e9f1f70339827da1f392314fb4aea0/0131191431v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a9/63/a9632752f52d4871b93a4f4413be884b/0131183549v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/5f/88/5f8847c90d2e4/50-mm.jpg)

:quality(80)/p7i.vogel.de/wcms/af/78/af78d1a793e1dc1cb774ecacafa12365/0126572790v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9c/21/9c21e09a281f8cafe81528fc9060e43e/0125420315v2.jpeg)