Interaktive Fehlersuche auf der Leiterplatte Mit Boundary Scan und Hpe_JTAG unter das BGA und in den IC schauen

JTAG/Boundary Scan gilt als genialstes Testverfahren, das in der Schaltung testet und den Fehlerort aufspürt – auch unter BGAs. Mit dem JTAG-Werkzeug Hpe_JTAG lassen sich ohnen großen Aufwand Prototypen mit einer grafischen Benutzeroberfläche interaktiv auf Fehler untersuchen. Und obwohl das Werkzeug für die Inbetriebnahme und Test von Baugruppen geschrieben wurde, ist es darauf bei Weitem nicht beschränkt.

Anbieter zum Thema

Jeder Entwickler, der schon einmal eine Leiterplatte mit BGAs in Betrieb genommen hat, kennt das Problem: die ersten Prototypen oder die erste Kleinserie kommt aus der Fertigung, eventuell teilweise von Hand bestückt. Man kontrolliert optisch noch einmal auf Fehlbestückung und Kurzschlüsse, atmet tief durch, schließt die Spannungsversorgung an und ist beruhigt, wenn kein Rauch aufsteigt und keines der Bauteile heiß wird. Im Idealfall lädt man nun sein Test-Design. Alles verhält sich, wie geplant.

Mal ehrlich: Wie oft haben Sie diesen Idealfall schon erlebt? In der Regel beginnt nun die Fehlersuche, die bei BGAs nicht ganz einfach ist, wenn Sie keinen Röntgenblick oder -inspektionssystem besitzen.

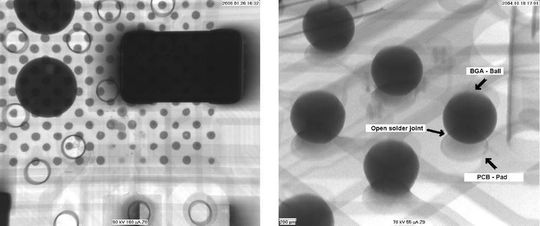

Bei den feinen Strukturen, die heute auf den Leiterplatten vorzufinden sind, kann teilweise nicht mehr garantiert werden, dass Lötstopplack zwischen den einzelnen Pads verbleibt. Die Folge ist, dass Solderballs im Reflow-Ofen verschmelzen können (Bild 1). Insbesondere bei großen BGAs kann es auch vorkommen, dass sich die Anschlüsse im Reflow-Ofen zusammenziehen und dann keinen Kontakt zur Leiterplatte bekommen.

JTAG-Tool von Hardwareentwicklern für Entwickler

Hpe®_JTAG wurde von Gleichmann Electronics Research für die Fehlersuche bei Eigenprodukten entwickelt. Dabei wurde Wert auf Filterfunktionen, das Importieren von Pin-Files aus der FPGA-Synthese und Möglichkeiten der Automatisierung über ein Scripting Interface gelegt. Das Werkzeug unterstützt alle obligatorischen JTAG-Instruktionen, wie auch INTEST, falls es vom Bauteil unterstützt wird.

Im Gegensatz zu teueren Highend JTAG-Werkzeugen kann Hpe®_JTAG für einen Bruchteil der Kosten, ohne großen Aufwand genutzt werden: Einfach eines der unterstützten JTAG-Kabel einstecken, mit dem Target-Board verbinden und los geht‘s.

Ein grundlegender Test wird gleich bei der Initialisierung der JTAG-Kette durchgeführt. Es werden die IDs der Bauteile in der Kette ausgelesen und gegebenenfalls mit erwarteten IDs verglichen. Falls nicht schon vorhanden, müssen BSDL-Files importiert werden.

(ID:275814)

:quality(80)/p7i.vogel.de/wcms/e9/ce/e9ce137e87eccac328ec5504c586c477/0129711019v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/68/46/684697b6eb687384e0d8c6803450401a/0130056395v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/0f/c0/0fc0d93c99a5d9066e58c39f41fb1b10/0130046764v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/60/fa6016fc48ac8609a451038ca38b0eca/0130241261v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/57/97/5797ffe4c6e19cf02aa75a7f742598b3/0130160607v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1d/d8/1dd8627e2323721d4ee5436f9401911e/0130147601v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fb/d3/fbd33264fcdf128866667be0a0a6b657/0130137877v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a5/5e/a55ec741a9c17cb890b2cb5bcb919477/0130162776v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/8d/fa8dedee195f29c33c89d86311c258ee/0130104146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cc/13/cc1378375499a26b5ddbb309d2155acb/0130085649v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/24/58/2458f1cae3100e375fbb8124f02c54af/0130111244v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/6d/f0/6df06a1488ceb6357c287fee993fad65/0130161592v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/65/f4/65f404dc6d19d4f1628ad7e49f6a22cf/0130136276v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/fc/fafc300481de3fd4d7f34400327d0d01/0130127049v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/10/45/1045969e69a1db4aaa73d0f74f55cc02/0129962687v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c7/f6/c7f61d0437c7f8fca3c6ff947ba2ad62/0129322490v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/66/0c/660c31afa35398bac9be42f2be73fdc4/0129073529v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/af/35af7dd326d198475d06fbb69aa600b5/0130175971v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/2e/c02e7bf72bfc434888c37100e2511681/0130127767v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/95/a1/95a197490145b7afcfd4dc176a1b5ef9/0130096114v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ef/a0/efa0d8af7bcf1d64636b877a04b853d9/0130136738v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bf/82/bf82f81061b759c454e15ec4c2e7560b/0130110139v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/74/96/74964a7715c738a9e8b17681445ceed3/0130103633v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/0d/18/0d183ecb569b03285578762658d2def6/0130061201v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f1/58/f158a1c680219c67cff9c099186ab50d/siemens-20ubtech-20hmnd-1920x1079v1.png)

:quality(80)/p7i.vogel.de/wcms/6a/93/6a93991941467231d8798c8577882dfd/0130071573v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/19/31/193191c71275b1f480fff0e5827be766/0130211045v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d1/d1/d1d103805ed7ac0df7feda4c46522b8c/0130164847v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/68/7e/687ebf75f8024edeec7ebd6d3582327f/0130240314v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bb/2a/bb2ac8404ae7b3f08a5c01d1ca0615a7/0130182922v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/68800/68851/65.jpg)

:quality(80)/p7i.vogel.de/wcms/66/0c/660c31afa35398bac9be42f2be73fdc4/0129073529v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ff/e4/ffe44f0dcf0fc0323926b1bc0a60d94f/0129386849v2.jpeg)