Anbieter zum Thema

Universell wie ein Schweizer Offiziersmesser

Obwohl Hpe®_JTAG für die Inbetriebnahme und Test von Leiterplatten geschrieben wurde, ist es nicht auf diesen Bereich beschränkt. Über das Scripting Interface gestattet das Tool JTAG-Zugriffe auf unterschiedlichen Abstraktionsebenen: High-Level-Zugriffe (SAMPLE, EXTEST, INTEST), wie sie auch aus der Benutzeroberfläche heraus aufgerufen werden können, aber auch Low-Level-Zugriffe, wie das Schreiben und Lesen beliebiger JTAG-Register, sind möglich.

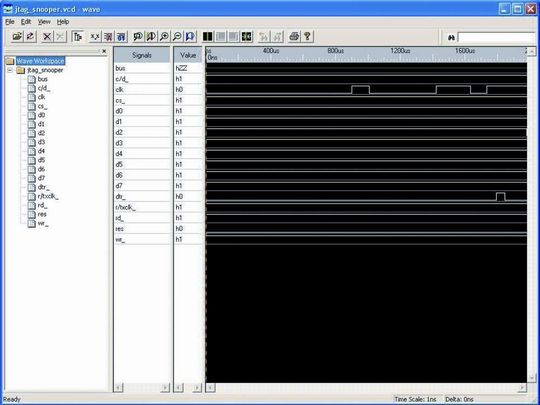

Beispielsweise können Testpattern über JTAG in einen Speicher (z.B. On-Chip RAM) geschrieben werden. Die Testpattern-Sequenz kann über JTAG gestartet, die Response der zu testenden Logik on-Chip zwischengespeichert und später offline über JTAG ausgelesen werden. Ein entsprechendes Script könnte Stimuli und Response in einem geeigneten Format speichern. Z.B. unterstützen die meisten Waveform Viewer den ASCII-basierenden Industriestandard Value Change Dump (VCD)“. Auf diese Weise kann mithilfe des Scripting Interfaces und der eigenen Fantasie ein programmierbarer Testpattern-Generator und ein Trace-Tool gebaut werden Bild 4).

Das bestätigt auch Ralf Derscheid bei der NEC Electronics Europe GmbH verantwortlich für ASIC-Lösungen: „Hpe®_JTAG hat mich zwar stets vor Unstimmigkeiten zwischen BSDL-Files und meinen Scripten gewarnt, mich aber in meiner Kreativität nie behindert. Für mich ist das Tool so universell wie ein „Schweizer Offiziersmesser“, weil selbst fehlende Funktionen mit Python jederzeit nachzurüsten sind. Grenzen setzt somit nur die (eigene) Fantasie.“

*Andreas Schwarztrauber ist Marketing Manager FPGA Systeme bei Gleichmann Electronics Research in Hagenberg, Oberösterreich.

(ID:275814)

:quality(80)/p7i.vogel.de/wcms/f5/5e/f55e737a7d227f2d048c579cab8e6985/0130834955v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/33/b4/33b4ab2c6baf7bd98f6f31747f105ab7/0130823277v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/96/97/96978cf39fdc205e816e3218f39499e5/0130663068v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/22/fa22ead6e6fe569ec03e08eba146bedc/0131141465v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/29/a0/29a0d3ad968ba9d262056d4f93073b9d/0131130383v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a1/2c/a12cd5489205b14b8ffda38315bd4d25/0131126505v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a0/b7/a0b74e201c3d9a12af0a204e1e578aad/0131136338v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/2e/78/2e789ef76c84f5fcdf02b5697a22f9ab/0131062677v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d9/92/d9920f978cf2b03bb4f2b4e6cfbface3/0131055455v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d2/1c/d21cea8a73c1dc8b94322e896fb7cc2b/0131036508v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/be/81/be8197dbe5f61c3c5ade3732457725af/0131041847v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/b5/1e/b51e81eb4981b7ba1cf3adcd38d09802/0131130065v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/cc/bacc37befe18c7062ab18bdae3ea75c7/0131064254v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d4/1d/d41d81ec84a42b4fd5d732d36d0021ce/0130877962v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9c/79/9c798ab2b4c18ba0a2c24f2491798d36/0130550888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/e7/b6e755d9e704319c0bb59dc1ac2d67e8/0130537290v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/34/1f/341f0c9b899c7509a01c9a13383af6cf/0131148001v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ca/8c/ca8cda9df29d8b2cf6f7b09abd8b7dda/0131065542v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/71/fa71d141fca285824eb23f3aba1333f2/0131012876v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b5/54/b5548923d20a751319550a3eb159af21/0131159519v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/87/b6/87b60368567da3c6b65107c55f5f69ec/0130689118v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b4/55/b455edd54c7e92e0f5bf2d059e2cc5ca/0130990400v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9b/96/9b96763092ce22624400387c5f264287/0130960582v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/49/76/4976fcd614ea458c165eb05744aec2fb/0131120525v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b0/d8/b0d8b5b7eeaed18fe805197c37cbbe14/0131086898v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/75/10/75102cf1bcc950d376da7fc4e9722ebe/0131066528v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/15/3515d9038ba5f392dca4f98115fc0a04/0131078602v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/24/3c/243ce3bf4a121e91c6a3217d81c29f36/0131192604v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/41/e9/41e9f1f70339827da1f392314fb4aea0/0131191431v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a9/63/a9632752f52d4871b93a4f4413be884b/0131183549v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/68800/68851/65.jpg)

:quality(80)/p7i.vogel.de/wcms/66/0c/660c31afa35398bac9be42f2be73fdc4/0129073529v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ff/e4/ffe44f0dcf0fc0323926b1bc0a60d94f/0129386849v2.jpeg)