Anbieter zum Thema

Irrtum 6: Ein Lagenaufbau wird eigentlich nur vom Leiterplattenhersteller benötigt.

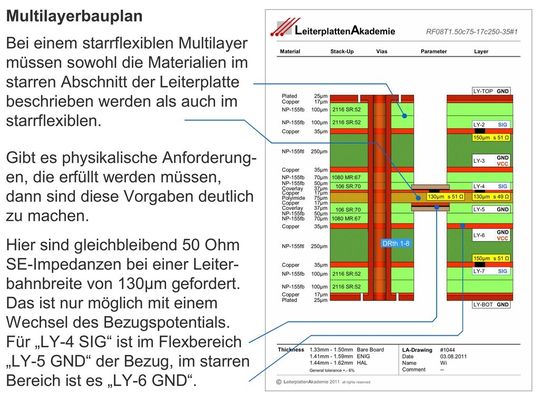

Nein. Der Bauplan für eine Leiterplatte, egal, ob ein- oder doppelseitig oder Multilayer, und unabhängig, ob starr oder flex oder starrflex, muss bereits vor Abschluss der Arbeiten am Schaltplan vorliegen. Im Schaltplan werden zunehmend constraints für das Routing festgelegt. Vorberechnete Impedanzwerte verlangen eine präzise Leiterbahnbreite und vorab zugeordnete Referenzplanes. Signalräume mit Bezug zu bekannten Rückstromwegen sind eine verbindliche Vorgabe für die Layoutkonstruktion am CAD-System.

Die Option, Powerplanes mit kapazitiven Eigenschaften in Leiterplatten einbauen zu können oder embedded components (Bauteilfunktionen auf den Innenlagen) in Polymertechnik mittels Carbondruck (z.B.: Induktivitäten, Widerstandswerte) zu fertigen, erhebt die Leiterplatte in den Status einer passiven elektrischen Komponente. Im Schaltplan müssen diese Funktionen Berücksichtigung finden. Für das CAD-Layout enthält der Bauplan der Leiterplatte somit entscheidende Anweisungen mit Blick auf die notwendigen Routingparameter sowie die Anlage von Signal- und Powerplanes.

Der Bauplan muss immer auch an den Baugruppenfertiger weitergereicht werden. Gerade bei Prototypen und Kleinserien hat die Materialspezifikation transparent zu sein. Die Kupferdicken, die Anzahl der Masseflächen und Lagen sowie der Lagenabstand beeinflussen die gezielte Auswahl des geeigneten Reflowprofiles. Diverse Kleber bei starrflexiblen Leiterplatten, Pluggingsubstrate, Coverlay und Lötstopmasken müssen bekannt sein, damit eine sichere Entscheidung für die richtige Strategie für die Produktion der Baugruppen getroffen werden kann (Bild 2).

Irrtum 7: Bei SMD-Layouts müssen die Vias mit Lötstoplack immer zugedruckt sein.

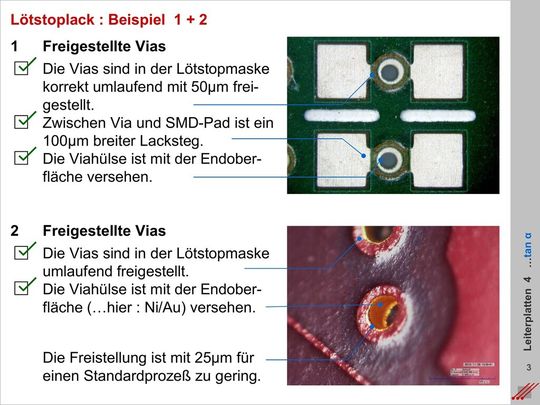

Im Gegenteil, die Vias respektive Durchkontaktierungen müssen immer offen sein. Üblicherweise werden heute fotosensitive Lötstoplacke verarbeitet, die als dünne Schicht auf die Oberfläche der Leiterplatte aufgetragen werden. Die Vias werden dadurch zwar überdeckt, der Lack bekommt später beim Trocknen aber auf Grund thermischer Spannungen Mikrorisse.

Für die heutigen chemisch prozessierten Endoberflächen dient der Lötstoplack als Resist, das heißt, der Lack wird vor der Endoberfläche auf die Leiterplatte aufgebracht. Ist die Hülse der Vias ganz oder weitestgehend mit Lötstoplack bedeckt, dann ist während des Prozessierens der chemischen Oberfläche keine ausreichende Durchflutung der Viahülsen mit den chemischen Reagenzien möglich. Folglich kommt es nicht zu einer Beschichtung der Innenwand der Hülse mit der vorgesehenen metallischen Endoberfläche.

Es kann sogar zu diversen Rückständen chemischer Substrate aus der Oberflächenfertigung und der Baugruppenproduktion kommen. Diese Rückstände sammeln sich in den Hülsen und können in Verbindung mit Kondensatbildung mittelfristig zur Korrosion führen. Nur bei offenen, lackfreien Vias ist die Voraussetzung geschaffen, eine Endoberfläche in die Hülsen einzubringen und nach dem Bestücken für eine rückstandsfreie Reinigung der Baugruppe zu sorgen (Bild 3).

Die Voraussetzungen dazu müssen durch das CAD-Layout geschaffen werden. Nur ein korrekt angelegter Padstack in Verbindung mit einem abgestimmten Routingraster kann diese Aufgabe lösen.

(ID:34212560)

:quality(80)/p7i.vogel.de/wcms/46/7c/467c0afffbfd10c3553c2888a4a6289f/0130479810v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/12/3d/123d9eb2c2e4ce13296371a2ad3718a4/0130412664v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d8/78/d878b7bfc23826e6ddfce42443836d28/0130384280v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/13/20/13208d1c2797edd67d9ff216b403726b/0130471595v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/38/cb/38cbe19e814dd30b94780bc3946547ab/0130446533v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a3/3e/a33e6d8a927d539ec6c3a0537f48f0f1/0130440028v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6b/61/6b61373f1c3f06f7f9343e6b0f0e9cc8/0130225062v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/15/93/1593dd152e6d58c5fc5da0d331777c54/0130357398v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/88/c28805ea7b2261235475146a5b0c61f8/0130313028v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/8d/fa8dedee195f29c33c89d86311c258ee/0130104146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cc/13/cc1378375499a26b5ddbb309d2155acb/0130085649v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6d/91/6d91abfa1b16ffcf470c7147facd7aa8/0130387695v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/85/b0/85b0b32128f6d1968e975043f1e0b67b/0130342166v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/1a/53/1a539631c940d184689460600bd2b395/0130410666v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/10/45/1045969e69a1db4aaa73d0f74f55cc02/0129962687v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c7/f6/c7f61d0437c7f8fca3c6ff947ba2ad62/0129322490v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/e4/bae4e54395e5a53088060531ef99b814/0130359274v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/af/35af7dd326d198475d06fbb69aa600b5/0130175971v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/2e/c02e7bf72bfc434888c37100e2511681/0130127767v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/7c/04/7c04916c305164fb10bc6cb05b51d934/0130431065v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/64/e5/64e5e333492f182ab7df5ab4c2b54c1e/0130463252v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/0a/95/0a95db4508128c4e11d5d268bf2c0a77/0130440053v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b3/65/b365dd5433c8b6d36c56c92b72f5b368/0130401081v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/85/c0/85c0cdd8fd326013aed52ca96777c998/0130426877v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f0/78/f07826d6c4e995980f1ada3377416aac/0130403626v4.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/c8/b6c8f7732da417bda3d298412f4c0ed8/0130453104v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/47/ce/47ce64bad7990f276f68cbb24505f6dd/0130472850v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/15/56/15564dea31861c376a385658c3b961a3/0130465243v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/98/ad/98ad595a6372aae8dbeac71681d23f41/0130450258v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bf/2a/bf2aad428ab1a80e6738fdbdc2efeb7e/0130453420v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/62/3a/623ac694d217a/ept-connectors-rgb-quadrat.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/62/16/621651a93b1ef/logo-we-rgb-pos.png)

:quality(80)/p7i.vogel.de/wcms/80/7b/807bc9dc4d65da8b9d67314d544b9e13/0128113873v4.jpeg)

:quality(80)/p7i.vogel.de/wcms/43/fe/43fef5f4f1ecffcc91680a16c26401cd/0127019959v2.jpeg)