Anbieter zum Thema

Irrtum 4: Für die Spezifikation eines Multilayers genügt die Angabe der Lagen.

Das kann lebensgefährlich werden. Die geometrischen Abstände zwischen elektrischen Lagen bestimmen die späteren physikalischen Eigenschaften der Baugruppe. Stromtragfähigkeit, Spannungsfestigkeit und Signalintegrität sind über die Geometrie der Leiterplatte definiert. Damit ist ein kompletter, fachlich korrekter, dokumentierter und nachvollziehbarer Multilayeraufbau ein unverzichtbarer Bestandteil einer jeden Leiterplattenproduktion.

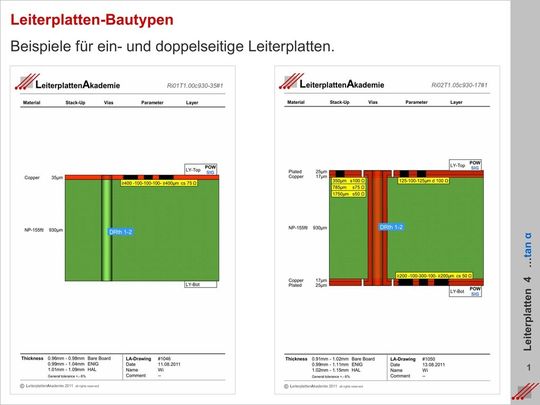

Ein aussagefähiger Lagenaufbau muss Teil der Fertigungsunterlagen sein und absolut verbindlichen Charakter haben. Bereits das einfache Vertauschen der Reihenfolge von Innenlagenlaminaten kann katastrophale Auswirkungen haben, ein Fehler, der von der üblichen elektronischen Prüfung noch nicht einmal detektiert werden kann. Aus heutiger Sicht muss sogar bereits der Aufbau von ein- oder doppelseitigen Leiterplatten dokumentiert sein (Bild 1).

Grundsätzlich müssen der Lagenaufbau respektive die Leiterplattenspezifikation schon vor Beendigung der Arbeit am Schaltplan vorliegen. Aspekte wie die Laufzeit von Signalen, die Kapazität von Stromversorgungssystemen, die Kosten für die Leiterplatte oder die Entwärmung der Baugruppe lassen sich sonst nicht verifizieren. Das bedeutet in der Praxis, dass unzureichende Informationen über die zu erwartenden wirtschaftlichen und technischen Eigenschaften des künftigen elektronischen Gerätes vorliegen. Eine geregelte Abstimmung zwischen Konstrukteur, CAD-Designer und Leiterplattenhersteller kann dann nicht stattfinden. Im Prinzip ist damit die Baugruppe außer Kontrolle.

Irrtum 5: Durch das Entfernen von Non Functional Pads auf den Innenlagen eines Multilayers kann mehr Platz für das Fan-Out hochintegrierter Bauteile geschaffen werden.

Leider nein. Für HDI- und MFT-Leiterplatten orientieren sich die maßgeblichen Routingabstände nicht mehr vornehmlich an den Leiterbahnen, sondern am Abstand der Tangente einer Bohrung zur Leiterbahn. Die Betrachtung „Leiterbahn zu Leiterbahn“ wird damit um die entscheidende und weitläufig gültige Betrachtung „Leiterbahn zu Bohrung“ erweitert. Ganz allgemein rückt damit die Betrachtung der Leiterbildstruktur in Relation zur Leiterplattenmechanik in den Vordergrund.

Als Folge dieser Verschiebung wird die zentrale Strategie nicht mehr (nur) darin bestehen, am CAD-System Werte für den elektrische Sicherheitsabstand (electrical distance) von Vektorstrukturen als constraints (Vorgaben) zu formulieren.

An deren Stelle tritt als mathematische Basis die generelle aber individualisierte Betrachtung von Toleranzräumen. Für die Berechnung dieser Toleranzräume ist das diskrete Vorhandensein eines Pads oder einer Leiterbahn ohne Bedeutung. Die Berechnungen orientieren sich an den realen Parametern für die Fertigung von Leiterplatten. Ausgehend von den Einflüssen der Basismaterialien, des individuellen Leiterbildes, der erforderlichen Prozessschritte und der Einsatzanforderungen an die Baugruppe werden die constraints für das Routing des CAD-Layouts über die dynamische Berechnung der real möglichen und sinnvollen Mindestabstände ermittelt.

Speziell für Non Functional Pads ( NFP) belegt die Berechung der Toleranzräume, welche Wirkung das Entfernen der Pads auf das CAD-Layout hat. Ist das Pad im Padstack des CAD-Systems bereits auf den minimalen Durchmesser gesetzt, dann ergibt sich für das Routing keinerlei Vorteil. Wird der durch das entfernte Pad freigewordene Raum für das Routing von Leiterbahnen genutzt, dann steigt die Ausschussrate während der Leiterplattenproduktion sofort deutlich an und führt oft sogar zum Totalausfall des produzierten Loses.

(ID:34212560)

:quality(80)/p7i.vogel.de/wcms/46/7c/467c0afffbfd10c3553c2888a4a6289f/0130479810v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/12/3d/123d9eb2c2e4ce13296371a2ad3718a4/0130412664v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d8/78/d878b7bfc23826e6ddfce42443836d28/0130384280v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/13/20/13208d1c2797edd67d9ff216b403726b/0130471595v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/38/cb/38cbe19e814dd30b94780bc3946547ab/0130446533v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a3/3e/a33e6d8a927d539ec6c3a0537f48f0f1/0130440028v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6b/61/6b61373f1c3f06f7f9343e6b0f0e9cc8/0130225062v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/15/93/1593dd152e6d58c5fc5da0d331777c54/0130357398v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/88/c28805ea7b2261235475146a5b0c61f8/0130313028v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/8d/fa8dedee195f29c33c89d86311c258ee/0130104146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cc/13/cc1378375499a26b5ddbb309d2155acb/0130085649v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6d/91/6d91abfa1b16ffcf470c7147facd7aa8/0130387695v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/85/b0/85b0b32128f6d1968e975043f1e0b67b/0130342166v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/1a/53/1a539631c940d184689460600bd2b395/0130410666v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/10/45/1045969e69a1db4aaa73d0f74f55cc02/0129962687v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c7/f6/c7f61d0437c7f8fca3c6ff947ba2ad62/0129322490v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/e4/bae4e54395e5a53088060531ef99b814/0130359274v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/af/35af7dd326d198475d06fbb69aa600b5/0130175971v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/2e/c02e7bf72bfc434888c37100e2511681/0130127767v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/7c/04/7c04916c305164fb10bc6cb05b51d934/0130431065v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/64/e5/64e5e333492f182ab7df5ab4c2b54c1e/0130463252v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/0a/95/0a95db4508128c4e11d5d268bf2c0a77/0130440053v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b3/65/b365dd5433c8b6d36c56c92b72f5b368/0130401081v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/85/c0/85c0cdd8fd326013aed52ca96777c998/0130426877v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f0/78/f07826d6c4e995980f1ada3377416aac/0130403626v4.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/c8/b6c8f7732da417bda3d298412f4c0ed8/0130453104v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/47/ce/47ce64bad7990f276f68cbb24505f6dd/0130472850v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/15/56/15564dea31861c376a385658c3b961a3/0130465243v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/98/ad/98ad595a6372aae8dbeac71681d23f41/0130450258v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bf/2a/bf2aad428ab1a80e6738fdbdc2efeb7e/0130453420v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/62/3a/623ac694d217a/ept-connectors-rgb-quadrat.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/62/16/621651a93b1ef/logo-we-rgb-pos.png)

:quality(80)/p7i.vogel.de/wcms/80/7b/807bc9dc4d65da8b9d67314d544b9e13/0128113873v4.jpeg)

:quality(80)/p7i.vogel.de/wcms/43/fe/43fef5f4f1ecffcc91680a16c26401cd/0127019959v2.jpeg)