GaN-Leistungshalbleiter CMOS-kompatible 200-mm-Plattform in GaN

Bei den Leistungshalbleitern kommen die ersten GaN-Transistoren auf den Markt. Wie SiC ist auch GaN ist ein teures Material, es lässt sich aber gut in dünnen Schichten auf preisgünstigem Silizium aufwachsen.

Anbieter zum Thema

Das Gebiet der Leistungselektronik wird derzeit mehr oder weniger von Silizium-basierten Bausteinen dominiert. Doch die Industrie hat inzwischen die Grenzen dessen erreicht, was mit Silizium in Bezug auf die Effizienz und Betriebsfrequenz machbar ist. Weitere Verbesserungen der Silizium-basierten Schaltungen bedingen recht komplexe 3D-Architekturen.

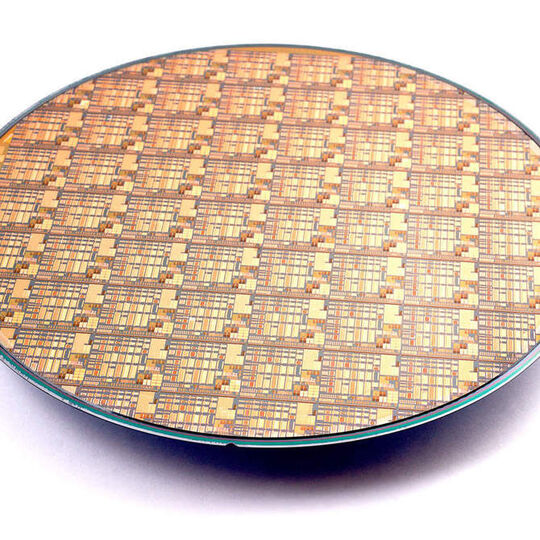

Deshalb suchen Forschungsinstitute und die Industrie intensiv alternative Materialien mit besseren Eigenschaften, wie Siliziumkarbid (SiC) oder Galliumnitrid (GaN). SiC ist allerdings nur in Form von teuren Wafern mit kleinem Durchmesser erhältlich. Auch GaN ist ein teures Material, es lässt sich jedoch gut in dünnen Schichten auf preisgünstigen Siliziumsubstraten aufwachsen. Zusätzlicher Vorteil ist, dass sich diese Wafer in bestehenden, hochproduktiven CMOS-Fabs verarbeiten lassen.

200-mm-Wafer sind optimal – wenn man sie herstellen kann

Die aktuellen Herausforderungen bestehen in der Herstellung geeigneter großflächiger Substrate, der Entwicklung eines CMOS-kompatiblen Fertigungsflusses und im Entwurf von Bausteinen mit überlegenen Eigenschaften. Doch der Ausblick ist positiv, und der wachsende Bedarf an solchen Bausteinen markiert eine viel versprechende Investment-Kategorie.

Derzeit geschieht der Großteil der GaN-Entwicklung und Fertigung noch auf 150-mm- oder sogar 100-mm-Wafern. Doch der Gesichtspunkt der Kosteneffizienz zwingt dazu, auch größere Waferdurchmesser ins Auge zu fassen. An erster Stelle stehen dabei 200-mm-Wafer (8 Zoll). Eine Fertigungsplattform auf der Basis von 200-mm-Wafern ist weitaus fortschrittlicher als das bestehende 150-mm- oder 200-mm-Equipment. Die Technik der 200-mm-Wafer ist derzeit so gut unterstützt, dass sogar innovative Entwicklungen auf 300-mm-Basis in vielen Fällen für die Fertigung auf 200-mm-Waferlinien zurückgestuft werden. Die Fertigung auf 200-mm-Wafern bietet höhere Produktivität und bessere Prozesskontrolle, und somit höhere Ausbeuten als mit kleineren Waferdurchmessern.

IMEC ist eines der Forschungszentren, das von Anfang an in die Entwicklung der GaN-Technologie eingebunden war. IMEC gilt als eines der führenden europäischen R&D-Zentren der Mikroelektronik und hat aktiv an der Entwicklung der heute existierenden CMOS-Technologie partizipiert. Das Institut verfügt über entsprechende Reinräume und modernste Tools für die unterschiedlichen Waferformate. Deshalb ist die Migration von GaN von kleineren Wafern auf die 200-mm-Technoloigie für IMEC ein natürlicher Entwicklungsschritt, für den die Expertise und die Tools verfügbar sind.

Parallel zu IMECs Arbeit an Bausteinen auf 150-mm-Wafern werden auch die notwendigen Epitaxie-Prozesse auf 200-mm-Wafern weiter vorangetrieben, einschließlich der Perfektionierung der Puffer- und Funktionsschichten. Die eigentlichen Herausforderungen bestehen in der Erzeugung hoch qualitativer uniformer Layer und im Ausgleich der mechanischen Spannungen, die während des epitaxialen Aufwachsens entstehen, sowie in der Beherrschung der Waferdurchbiegung. Das Ergebnis muss ein Wafer sein, der extrem uniforme Funktionsschichten aufweist, der innerhalb der Spezifikationen der erlaubten Waferkrümmung liegt, und der die Verarbeitung in bestehenden Silizium-Fabs zulässt.

Die auftretenden mechanischen Spannungen entstehen infolge der großen Gitter-Fehlanpassung zwischen den III-N-Schichten (GaN und Al-GaN) und dem Siliziumsubstrat. Dies macht es erforderlich, sorgfältig gewählte Pufferschichten zwischen dem Substrat und der Funktionsschicht einzufügen. Damit lässt sich die Waferdurchbiegung auf weniger als ±50 µm reduzieren.

(ID:39138360)

:quality(80)/p7i.vogel.de/wcms/e9/ce/e9ce137e87eccac328ec5504c586c477/0129711019v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/68/46/684697b6eb687384e0d8c6803450401a/0130056395v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/0f/c0/0fc0d93c99a5d9066e58c39f41fb1b10/0130046764v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/60/fa6016fc48ac8609a451038ca38b0eca/0130241261v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/57/97/5797ffe4c6e19cf02aa75a7f742598b3/0130160607v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1d/d8/1dd8627e2323721d4ee5436f9401911e/0130147601v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fb/d3/fbd33264fcdf128866667be0a0a6b657/0130137877v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a5/5e/a55ec741a9c17cb890b2cb5bcb919477/0130162776v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/8d/fa8dedee195f29c33c89d86311c258ee/0130104146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cc/13/cc1378375499a26b5ddbb309d2155acb/0130085649v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/24/58/2458f1cae3100e375fbb8124f02c54af/0130111244v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/6d/f0/6df06a1488ceb6357c287fee993fad65/0130161592v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/65/f4/65f404dc6d19d4f1628ad7e49f6a22cf/0130136276v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/fc/fafc300481de3fd4d7f34400327d0d01/0130127049v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/10/45/1045969e69a1db4aaa73d0f74f55cc02/0129962687v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c7/f6/c7f61d0437c7f8fca3c6ff947ba2ad62/0129322490v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/66/0c/660c31afa35398bac9be42f2be73fdc4/0129073529v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/af/35af7dd326d198475d06fbb69aa600b5/0130175971v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/2e/c02e7bf72bfc434888c37100e2511681/0130127767v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/95/a1/95a197490145b7afcfd4dc176a1b5ef9/0130096114v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ef/a0/efa0d8af7bcf1d64636b877a04b853d9/0130136738v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bf/82/bf82f81061b759c454e15ec4c2e7560b/0130110139v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/74/96/74964a7715c738a9e8b17681445ceed3/0130103633v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/0d/18/0d183ecb569b03285578762658d2def6/0130061201v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f1/58/f158a1c680219c67cff9c099186ab50d/siemens-20ubtech-20hmnd-1920x1079v1.png)

:quality(80)/p7i.vogel.de/wcms/6a/93/6a93991941467231d8798c8577882dfd/0130071573v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/19/31/193191c71275b1f480fff0e5827be766/0130211045v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d1/d1/d1d103805ed7ac0df7feda4c46522b8c/0130164847v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/68/7e/687ebf75f8024edeec7ebd6d3582327f/0130240314v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bb/2a/bb2ac8404ae7b3f08a5c01d1ca0615a7/0130182922v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/76800/76895/65.jpg)

:fill(fff,0)/p7i.vogel.de/companies/66/1f/661fa8e004810/heitec-logo-2024-1200px-ae.png)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/9600/9682/65.jpg)

:quality(80)/p7i.vogel.de/vogelonline/bdb/574600/574658/original.jpg)

:quality(80)/p7i.vogel.de/vogelonline/bdb/574600/574659/original.jpg)

:quality(80)/p7i.vogel.de/vogelonline/bdb/574600/574660/original.jpg)

:quality(80)/p7i.vogel.de/wcms/74/39/7439be185c8059beae56072c2aecad4b/0127169891v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/53/0d/530d61c4b20c6fa2d5d03fc69a72f110/0125300370v2.jpeg)