HDI-Leiterplatten - Teil 1 Wann der Umstieg auf HDI- und Mikrovia-Technik sinnvoll ist

Die HDI/SBU-Technologie hat sich in den letzten Jahren von der Sondertechnologie zum „Mainstream“ gewandelt. Obwohl dieses Technologie für die meisten Fälle eine bessere Lösung bietet, kann der Umstieg neue Probleme verursachen. Experten empfehlen folgende Aspekte bei der Entscheidung für die HDI- und Mikrovia-Technik zu berücksichtigen.

Anbieter zum Thema

Immer höhere Bestückungs- und Verdrahtungsdichten, neue und immer kompaktere Bauteile-Gehäuse sowie EMV-, High-Speed- und System-Integrity-Anforderungen bringen Leiterplattenlayouts in klassischer Technologie immer öfter an die Grenzen des Machbaren. Und die HDI/SBU-Technologie bietet in den meisten Fälle klar bessere Lösungen.

Was ist eigentlich HDI/SBU?

Von HDI (High Density Interconnect = Hochdichte Verbindungen) spricht man, wenn die feinsten Leiterbahnstrukturen von 150 µm und feiner vorliegen und/oder Durchkontaktierungen (Vias) mit einem Durchmesser von <0,2 mm verwendet werden.

SBU (Sequential Build Up) steht für sequenziellen (aufeinander folgenden) Lagenaufbau von innen nach außen.

Dies bedingt bei Multilayer-Schaltungen mindestens zwei Pressvorgänge. Blind Vias (Sacklöcher) sind auf einer Innenlage endende Ankontaktierungen, die bei HDI-Technologie zumeist als Mikrovias vorwiegend in den beiden jeweiligen Außenlagen eingesetzt werden.

Als Buried Vias (vergrabene Durchkontaktierungen) bezeichnet man in den Kernlagen liegende und außen nicht sichtbare Ankontaktierungen. Diese gab und gibt es auch schon bei „klassischen“ Technologien. In der HDI-Technologie werden sie zumeist eingesetzt, um Ankontaktierungen unter Bauelementen mit hoher Anschlussdichte (z.B. BGAs) setzen zu können.

Als Mikrovia bezeichnet man heute allgemein An- oder Durchkontaktierungen mit einem Bohrlochdurchmesser kleiner als 0,20 mm. Diese können gebohrt, gelasert oder per Plasma geätzt sein.

Bei einem SBU-Multilayer teilt sich die Schaltung in einen Doppel- oder Multilayer-Kern und eine oder mehrere äußere Mikrovia-Lagen auf. Kommen Buried Vias über mehr als zwei Lagen oder mehrere äußere Mikrovia-Lagen vor, sind im Produktionsprozess mindestens zwei Pressvorgänge nötig. Je nach den gewünschten Eigenschaften und nach der Lage und Art der Kontaktierungen sind mehrere Varianten des Aufbaus für eine bestimmte Lagenzahl möglich. Auch gibt es eine Vielzahl an Materialien und Materialstärken für Prepreg- und Innenlagen. Hier ist eine Beratung durch den Leiterplattenhersteller dringend erforderlich. Diese sollte schon in der Planungsphase und noch vor dem Beginn des CAD-Layouts stattfinden.

Die Entscheidenden Kostenfaktoren beim SBU-Aufbau einer Leiterplatte sind:

- die Anzahl der Pressungen,

- die Anzahl der Bohrprogramme (Blind und Buried Vias) sowie

- die Anzahl der Durchkontaktierungsprozesse.

Je nach den gewünschten Eigenschaften und nach der Lage und Art der Kontaktierungen sind mehrere Varianten des Aufbaus für eine bestimmte Lagenzahl möglich. Auch gibt es eine Vielzahl an Materialien und Materialstärken für Prepreg- und Innenlagen. Hier ist eine Beratung durch den Leiterplattenhersteller dringend erforderlich. Diese sollte schon in der Planungsphase und noch vor dem Beginn des CAD-Layouts stattfinden

Warum HDI-/SBU-Strukturen?

Der häufigste Grund für den Umstieg auf eine HDI-Technologie ist die deutlich höhere Verdrahtungsdichte. Der Platz, der durch die feineren Leiterbahnenstrukturen gewonnen wird lässt sich dabei mehrfach nutzen. Zum einen kann die Packungsdichte erhöht werden, da mehr Platz für Bauteile und deren Landeflächen zur Verfügung steht, zum anderen sinkt der Flächenbedarf insgesamt, was sich in einer reduzierten Platinengröße oder auch in einer kleineren Zahl an benötigten Verdrahtungsebenen (Layer) äußern kann.

Hohe Verdrahtungsdichte schafft Platz

Und oft genug geht es auch „nur“ darum, bei gegebenen Randbedingungen wie Platinengröße, Layerzahl und Verbindungsdichte („Netze pro Flächeneinheit“) überhaupt eine entflechtbare Lösung zu finden. Großzügigere Platzverhältnisse erlauben es auch eher, zeit- und kostengünstig Autorouter einzusetzen. Eine größere Anzahl von Layern in „konventioneller Technologie führt nicht immer zu einem positiven Ergebnis. Schließlich wird auch ein Teil der neu gewonnenen Fläche bereits wieder durch die für die Anbindungen der Ebenen benötigten Durchkontaktierungen verbraucht. Zudem sind oft der maximalen Dicke einer Leiterplatte Grenzen gesetzt.

Ein weiterer Grund für den Einsatz von HDI-Technologien ist die Notwendigkeit eines feineren Systemrasters zur Anbindung von hochkomplexen Bauteilen. Oft sind FPGAs oder auch „Standard“-Bauteile nur noch im BGA- oder TSOP-Gehäuse mit Anschlussrastern von 1000 µm und weniger verfügbar. Diese sind in „konventioneller“ Technik kaum mehr anschließ- und entflechtbar, speziell wenn auch noch Leitungen zwischen den Anschlüssen hindurch geführt werden sollen.

Mikrovias haben bessere EMV-Eigenschaften als klassische Durchkontaktierungen

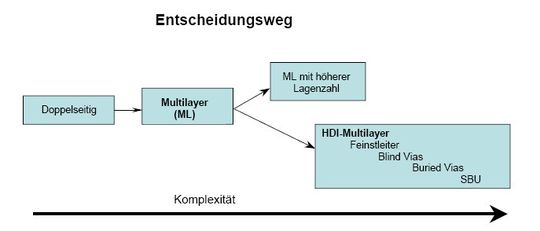

Auch Technologievorgaben können zwingend zum Wechsel in eine HDI-Technologie führen. Dies gilt insbesondere für Leiterplatten mit erhöhten EMV-Anforderungen, aber auch für höhere Frequenzen ab ca. 500 MHz. Hier sind fast immer impedanzkontrollierte Leitungen erforderlich, die zu feineren Leiterbahnstrukturen zwingen, da der Lagenabstand und die Dielektrikumsmaterialien nicht weit genug variierbar sind, um die gewünschten Impedanzwerte zu erzielen. Darüber hinaus haben die in der HDI-Technologie verwendeten Mikrovias grundlegend bessere elektrische Eigenschaften als die klassischen Durchkontaktierungen. Allgemein ausgedrückt: Schnelle Busse wie PCI-Express oder auch DDR2/3-Speicheranbindung lassen sich nur in HDI-Technologie realisieren. In den meisten Fällen erfolgt der Umstieg auf HDI schrittweise in Abhängigkeit von der Anforderung an die Leiterplatte (primär: Verdrahtungsdichte).

Worauf ist zu achten?

Zunächst einmal muss das Layout „fertigbar“ sein. Dies setzt die Kenntnis der HDI-Design Rules des jeweiligen Leiterplattenfertigers genauso voraus wie die sorgfältige Integration dieser Design Rules in die eigenen Bauteile-bibliotheken. Dabei kann nicht einfach linear skaliert werden, es gelten nach wie vor die grundlegenden Regeln, z.B. für Isolationsabstände und Lötstoppfreistellungen.

Dabei gilt grundsätzlich: in Hinblick auf Ausbeute (yield) und Fertigungskosten ist nicht alles sinnvoll, was technisch machbar ist. Speziell für Leiterbahnbreiten und Abstände gilt nach wie vor: „So gering wie nötig – so groß wie möglich!“

Die Fertigbarkeit feinster Strukturen ist ein wichtiger Schwerpunkt für die Machbarkeit der Schaltung. Dabei spielen auch Ätz- und Kupferaufbaueffekte in den Außenlagen wichtige Rollen. Hier sollte von HDI-„Neulingen“ das Know-how des Leiterplattenproduzenten bereits in der Phase der Lagenauswahl und -zuordnung zu Rate gezogen werden. Geringe Cu-Dicken auf den Innenlagen wirken sich ebenfalls positiv auf die Realisier-barkeit feinster Strukturen aus.

Gerne vernachlässigt wird auch die Thematik der Restringabmessungen und Isolationsabstände auf den Innenlagen. Diese können nicht wie Leiterbahnbreite oder Bohrdurchmesser linear verkleinert werden, sondern sind von Fertigungs- und Reproduktionstoleranzen bzw. von den elektrophysikalischen Gegebenheiten abhängig.

Aspect Ratio der An-/Durchkontaktierungen beachten

Altbekannt, doch oft und gerne missachtet wird das Aspect Ratio der An-/Durchkontaktierungen. Speziell bei „echten“ Sacklöchern in den Außenlagen eines sequenziellen Aufbaus wird vielfach übersehen, dass der minimale Durchmesser der Mikrovias bei gegebenem Aspect Ratio durch die (Außen-)Lagendicke vorgegeben ist. Diese ist aber vielfach aufgrund von Impedanz- und Aufbau-vorgaben nicht beliebig verkleinerbar.

Hier sollten bereits im Vorfeld verschiedene Kontaktierungs- und Aufbauvarianten mit dem Fertiger diskutiert werden. Richtig kompliziert wird die HDI-Thematik dann beim Aufbau von höherlagigen, impedanzkontrollierten Leiterplatten. Auch hier sind Knowhow und Praxis gefragt: Nicht alles, was sich in einem „schlauen“ CAD-System wunderschön ansieht ist so auch in der Praxis real produzierbar. Und jedes Layout lässt sich schließlich noch nach den verschiedensten Gesichtspunkten optimieren.

Hier finden Sie alle Teile der Beitragsreihe HDI-Leiterplatten.

*Christian Ranzinger ist Leiter Technologie und Prokurist beim Leiterplattenhersteller Contag GmbH in Berlin.

(ID:204903)

:quality(80)/p7i.vogel.de/wcms/e9/ce/e9ce137e87eccac328ec5504c586c477/0129711019v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/68/46/684697b6eb687384e0d8c6803450401a/0130056395v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/0f/c0/0fc0d93c99a5d9066e58c39f41fb1b10/0130046764v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1d/d8/1dd8627e2323721d4ee5436f9401911e/0130147601v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/8e/d4/8ed4a2aa0bf362584aa1284f0adb2fdf/0130156040v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/65/f4/65f404dc6d19d4f1628ad7e49f6a22cf/0130136276v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fb/d3/fbd33264fcdf128866667be0a0a6b657/0130137877v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a5/5e/a55ec741a9c17cb890b2cb5bcb919477/0130162776v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/8d/fa8dedee195f29c33c89d86311c258ee/0130104146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cc/13/cc1378375499a26b5ddbb309d2155acb/0130085649v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/24/58/2458f1cae3100e375fbb8124f02c54af/0130111244v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/fc/fafc300481de3fd4d7f34400327d0d01/0130127049v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d2/cd/d2cd33084ab732ff8a600bc55ade1f47/0130096831v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/10/45/1045969e69a1db4aaa73d0f74f55cc02/0129962687v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c7/f6/c7f61d0437c7f8fca3c6ff947ba2ad62/0129322490v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/66/0c/660c31afa35398bac9be42f2be73fdc4/0129073529v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/af/35af7dd326d198475d06fbb69aa600b5/0130175971v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/2e/c02e7bf72bfc434888c37100e2511681/0130127767v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/95/a1/95a197490145b7afcfd4dc176a1b5ef9/0130096114v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bf/82/bf82f81061b759c454e15ec4c2e7560b/0130110139v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/74/96/74964a7715c738a9e8b17681445ceed3/0130103633v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/0d/18/0d183ecb569b03285578762658d2def6/0130061201v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/72/19/7219e53d462877119eaf0bd98783a46d/0129953146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6a/93/6a93991941467231d8798c8577882dfd/0130071573v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d3/76/d3760874d137b2f4bae5954b46dd5900/0130101582v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/42/de/42de87134adee379a83e5d633ba48c95/0130176499v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/90/0c/900ca1b73852ed45bd7e42a6119192dd/0130174841v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/5e/ed/5eed37b21283f8f364a37d025d53fa48/0130167146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bb/2a/bb2ac8404ae7b3f08a5c01d1ca0615a7/0130182922v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ef/9d/ef9dc7f8402f3f4ff42268e573921bc4/0130129635v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/62/16/621651a93b1ef/logo-we-rgb-pos.png)

:fill(fff,0)/p7i.vogel.de/companies/60/f6/60f6829670d63/beta-layout-logo.jpeg)

:quality(80)/p7i.vogel.de/wcms/2c/40/2c40cea54250c0cc97dbc8d8448798a5/0129385029v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/66/c1/66c14543fd48c69fe35aeca2e513966a/0125007023v5.jpeg)