Mixed Signal Gate Arrays PSoC jetzt mit ARM Cortex-M3

Im Dezember 2009 hat Cypress eine damalige Neuheit vorgestellt: Programmable System on Chip 3 mit 30 MIPS Rechenleitung. Die Entwicklung ging weiter: PSoC 5 ist mittlerweile mit einem ARM Cortex-M3 Core ausgestattet. Welche Vorteile bieten die konfigurierbaren SoCs, die als eigenständige Chiplösung oder als Embedded-System zum Einsatz kommen?

Anbieter zum Thema

Seit Juli 2010 bemustert Cypress nun den Turbo-PSoC 5 mit einem ARM-Cortex-M3-Prozessorkern. Mit seiner 32-Bit-Architektur und 100 DMIPS stellt er die derzeitige Oberklasse konfigurierbarer Analog-/Digital-System-on-Chip-Lösungen dar und ermöglicht so auch neue rechenintensive Applikationen mit höherer Genauigkeit. Der Programmspeicher wurde auf bis zu 256 KByte Flash erweitert, um umfangreichere Programme, Konfigurationen und gegebenfalls eigene Echtzeit-Betriebssysteme zu unterstützen – ein eigenständiges System-on-Chip oder Embedded-System also.

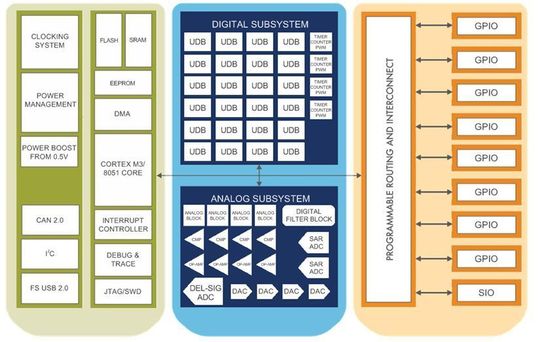

War der PSoC 1 noch mit einem 8-Bit-Prozessorkern mit ca. 4 MIPS ausgestattet, so leisten die neuen Generationen aus dem Jahre 2009 bis zu 30 MIPS und jetzt 2010 bis zu 100 DMIPS. Die neuen SoCs bieten nicht nur einen leistungsfähigen 8-Bit-/8051-Single-Cyle-Core (PSoC 3 mit bis zu 67 MHz / 30 MIPS) und jetzt einen 32-Bit-ARM-Cortex-M3 (PSoC 5 mit max. 80 MHz / 100 DMIPS), sondern zusätzlich noch leistungsfähigere analoge Blöcke mit höherer Genauigkeit und Auflösung; digitale Logikblöcke zur Realisierung von Glue-Logik oder Zustandsmaschinen im Stile eines FPGAs/PLDs; bis zu 62 GPIOs; mehr Speicherresourcen; ein flexibles, einstellbares Taktsystem mit Teilern/Verdopplern und vieles mehr. Tabelle 1 zeigt eine Gegenüberstellung der Leistungsmerkmale zwischen PSoC 3/5.

PSoC stellt damit eines der flexibelsten Subsysteme mit digitalen und vor allem analogen Funktionen auf dem heutigen Controllermarkt dar. Zusätzlich arbeiten alle Funktionen über den Spannungsbereich von 0,5 bis 5,5 V, inklusive Low-Power-Optionen. Für sich spricht die Kompatibilität: Viele PSoC-3-Typen sind zu PSoC 5 pinkompatibel, womit sich viele Designs durch Mausklick in den gewünschten PSoC-Typ migrieren lassen (Bild 1). Unterschiedliche Klassen von Geräten und Funktionen lassen sich so kostenoptimiert anbieten. Daher sind auch die Gehäuseformen innerhalb von PSoC 3 und 5 weitgehend gleich: 100-Pin-TQFP, 68-Pin-QFN, 48-Pin-SSOP (zusätzlich: 48-Pin-QFN bei PSoC 3)

Was leistet der Cortex-M3 Core im PSoC 5?

ARM-basierende Prozessoren und Controller sind derzeit sehr beleibt und lassen die MIPS-Architekturen in den Hintergrund treten. PSoC 5 bedient sich des ARM Cortex-M3 / v7 (enhanced) in Harvard-Architektur, in der Daten und Befehle getrennt voneinander gehalten und unabhängig voneinander bedient werden. Der Thumb2-Befehlssatz unterstützt neben den 16-Bit-Befehlen auch solche mit 32 Bit – dadurch wird deutlich weniger Programmspeicher benötigt als bei allen herkömmlichen Prozessorlösungen.

(ID:358799)

:quality(80)/p7i.vogel.de/wcms/46/7c/467c0afffbfd10c3553c2888a4a6289f/0130479810v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/12/3d/123d9eb2c2e4ce13296371a2ad3718a4/0130412664v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d8/78/d878b7bfc23826e6ddfce42443836d28/0130384280v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/13/20/13208d1c2797edd67d9ff216b403726b/0130471595v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/38/cb/38cbe19e814dd30b94780bc3946547ab/0130446533v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a3/3e/a33e6d8a927d539ec6c3a0537f48f0f1/0130440028v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6b/61/6b61373f1c3f06f7f9343e6b0f0e9cc8/0130225062v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/15/93/1593dd152e6d58c5fc5da0d331777c54/0130357398v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/88/c28805ea7b2261235475146a5b0c61f8/0130313028v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/8d/fa8dedee195f29c33c89d86311c258ee/0130104146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cc/13/cc1378375499a26b5ddbb309d2155acb/0130085649v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6d/91/6d91abfa1b16ffcf470c7147facd7aa8/0130387695v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/85/b0/85b0b32128f6d1968e975043f1e0b67b/0130342166v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/1a/53/1a539631c940d184689460600bd2b395/0130410666v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/10/45/1045969e69a1db4aaa73d0f74f55cc02/0129962687v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c7/f6/c7f61d0437c7f8fca3c6ff947ba2ad62/0129322490v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/e4/bae4e54395e5a53088060531ef99b814/0130359274v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/af/35af7dd326d198475d06fbb69aa600b5/0130175971v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/2e/c02e7bf72bfc434888c37100e2511681/0130127767v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/7c/04/7c04916c305164fb10bc6cb05b51d934/0130431065v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/64/e5/64e5e333492f182ab7df5ab4c2b54c1e/0130463252v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/0a/95/0a95db4508128c4e11d5d268bf2c0a77/0130440053v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b3/65/b365dd5433c8b6d36c56c92b72f5b368/0130401081v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/85/c0/85c0cdd8fd326013aed52ca96777c998/0130426877v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f0/78/f07826d6c4e995980f1ada3377416aac/0130403626v4.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/c8/b6c8f7732da417bda3d298412f4c0ed8/0130453104v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/47/ce/47ce64bad7990f276f68cbb24505f6dd/0130472850v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/15/56/15564dea31861c376a385658c3b961a3/0130465243v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/98/ad/98ad595a6372aae8dbeac71681d23f41/0130450258v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bf/2a/bf2aad428ab1a80e6738fdbdc2efeb7e/0130453420v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/61/a8/61a8d8e6ca4c2/glyn-logo-profilbild.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/5f/15/5f157c2d880f4/ish-logo2020.jpg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/68800/68851/65.jpg)

:quality(80)/p7i.vogel.de/wcms/88/0b/880b1539aba182d2b26dc2b5a3f0541e/0125283151v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/0a/f9/0af9ef52ce077b935efc629bd4e357a6/0128162746v1.jpeg)