Anbieter zum Thema

Ein Anwendungsbeispiel zur Demonstration der Vorteile

Designs, die den SMPTE-424-Standard unterstützen müssen, sind ein gutes Beispiel für den Einsatz programmierbarer Takt-ICs mit mehreren Ausgängen. Dieser Standard (auch 3G-SDI genannt) weist sehr strenge Augen-Jitter-Spezifikationen für die 3-GBit/s-SerDes-Funktion (Serializer/Deserializer) auf, um die gewünschte Bitfehlerrate (BER; Bit Error Rate) zu erzielen. Die wesentlichen Merkmale von SMPTE 424 bzw. 3G-SDI sind:

- Timing-Jitter-Spezifikation 2.0 UI max., Spitze-Spitze, von 10 Hz bis 100 kHz

- Anpassungs-Jitter-Spezifikation 0.3 UI max., Spitze-Spitze, von 100 kHz bis 297 MHz; empfohlen: 0.2 UI

Ein Einheitsintervall (UI; Unit Interval) ist die Zeit zwischen zwei aufeinanderfolgenden Signalübergängen und dem Kehrwert der Taktfrequenz.

Die technischen Anforderungen erhöhen sich weiter, da bei der Videosignalübertragung sowohl NTSC- als auch PAL-HDTV-Standards zu unterstützen sind. Damit müssen gleichzeitig 148,5-MHz- und 148,5/(1,001)-MHz-Referenztakte zur Verfügung stehen. Der Trend, Video auch über Video-Over-IP zu übertragen bedeutet, dass das Design auch 10G Ethernet PHYs (10 Gigabit Ethernet Physical Layer) unterstützen muss. Damit ist zusätzlicher Referenztakt von 156,25 MHz erforderlich.

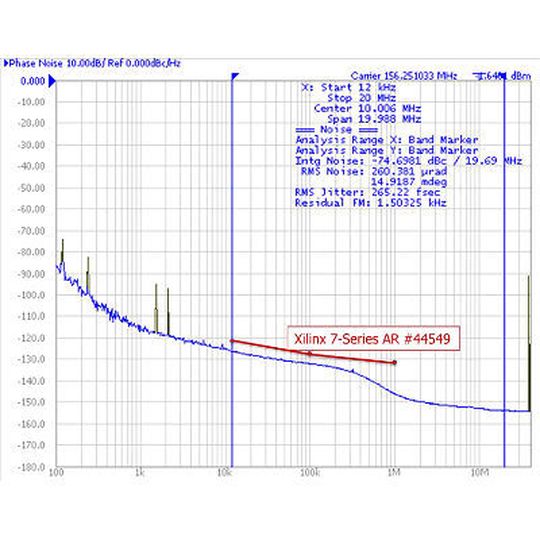

Durch ihre integrierten hochleistungsfähigen GTX/GTH/GTP-Transceiver werden die FPGAs der Xilinx-7-Serie oft für diese SMPTE-konformen Designs ausgewählt. Um die Augen-Jitter-Spezifikation nach SMPTE 424 zu erfüllen, spezifiziert Xilinx ein sehr enges dBc/Hz-Phasenrauschen für den Referenztakt, der diese SerDes-Funktionen steuert. Werden die gleichen Xilinx 7 Series GTX/GTH/GTP-Transceiver auch für 10-GBit/s-SerDes verwendet, spielen die strengen Anforderungen an das dBc/Hz-Phasenrauschen ebenfalls eine Rolle. Diese nicht-ganzzahligen Taktfrequenzen (148,5; 148,351648; 156,25 MHz) stellen zusammen mit den strengen Phasenrauschanforderungen für jeden Takt eine große Herausforderung dar, wenn eine integrierte Taktlösung bereitgestellt werden soll.

Zum Glück gibt es einen Baustein, der alle diese Takte synthetisieren kann: die Highend-PLLs der Universal Frequency Translator (UFT) Serie von IDT. Sie können als Synthesizer eingesetzt werden und benötigen als Eingangsreferenz nur einen einfachen, parallel-resonanten Quarz mit Grundfunktion. Die UFT-Serie unterstützt eine oder zwei verschiedene (über Anschlüsse wählbare) Konfigurationen pro PLL. Diese können vorab in den nicht-flüchtigen OTP-Speicher geladen werden, um einen automatischen Betrieb direkt nach dem Einschalten zu gewährleisten. Alternativ lässt sich über eine serielle I2C-Schnittstelle die gewünschte Frequenzübersetzungskonfiguration einstellen.

Im SMPTE-424-Design kann IDTs 8T49N241 als Synthesizer mit vier Ausgängen eingesetzt werden. Dies spart Platz auf der Leiterplatte und sorgt für ein weniger komplexes Design. Die Takt-ICs dieser Serie erfüllen die für Xilinx' 7-Serie erforderlichen Referenztaktbedingungen in dieser komplizierten Anwendung.

Bild 2 zeigt ein Phasenrauschdiagramm für einen 156,25-MHz-Ausgangstakt, der über einen UFT-Takt-IC von IDT erzeugt wird. Das Phasenrauschen liegt weit unter der Phasenrauschmaske, die in Xilinx' Anwendungshinweis (Action Note) AR# 44549 festgelegt ist.

(ID:43952868)

:quality(80)/p7i.vogel.de/wcms/f5/5e/f55e737a7d227f2d048c579cab8e6985/0130834955v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/33/b4/33b4ab2c6baf7bd98f6f31747f105ab7/0130823277v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/96/97/96978cf39fdc205e816e3218f39499e5/0130663068v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/14/e8/14e887156fd8fb66138bfc7972c4cd3f/0131074909v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/51/08/5108a9dea8ae93ecddbcf8beaf0540f8/0131047719v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/4d/ba4d85f7677531f446b5258a0cd242bf/0131025523v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/2e/78/2e789ef76c84f5fcdf02b5697a22f9ab/0131062677v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d9/92/d9920f978cf2b03bb4f2b4e6cfbface3/0131055455v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d2/1c/d21cea8a73c1dc8b94322e896fb7cc2b/0131036508v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/be/81/be8197dbe5f61c3c5ade3732457725af/0131041847v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/0d/34/0d34c0b5b16676a55682e081ca59da32/0130890395v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c5/42/c542a36bfc0e9beb119924d176f19e06/0131065166v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/71/b7/71b7507ed6f501a79b26477f34c8b28c/0130974158v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d4/1d/d41d81ec84a42b4fd5d732d36d0021ce/0130877962v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9c/79/9c798ab2b4c18ba0a2c24f2491798d36/0130550888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/e7/b6e755d9e704319c0bb59dc1ac2d67e8/0130537290v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ca/8c/ca8cda9df29d8b2cf6f7b09abd8b7dda/0131065542v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/71/fa71d141fca285824eb23f3aba1333f2/0131012876v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e1/39/e13927f73987c9fb63d6f7145a597e6a/0130656559v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/87/b6/87b60368567da3c6b65107c55f5f69ec/0130689118v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b4/55/b455edd54c7e92e0f5bf2d059e2cc5ca/0130990400v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9b/96/9b96763092ce22624400387c5f264287/0130960582v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/82/71/8271e36a4b6aa180fa903edd1de396f1/0130907348v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f6/e7/f6e70a7430db9783176d5e3bf25f5707/0131063190v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/ec/6b/ec6bb7201f5a2e41cd4942d59b23b999/0131074433v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/0a/350a177ef33b960e8f24c9be3717c653/0131061473v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ae/92/ae92a78425f17c6358d01ffd9b1c90ed/0131050297v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fc/5e/fc5e77b8434779834850aab40a903347/0131047752v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/43/c2439a5f7ecd10d2d7f02a4a5f38e97d/0131046056v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/60/b6/60b601af20368/et-system-logo-rgb.png)

:fill(fff,0)/p7i.vogel.de/companies/66/1f/661fa8e004810/heitec-logo-2024-1200px-ae.png)

:fill(fff,0)/p7i.vogel.de/companies/60/37/6037a859ec501/dmb-rgb-quadrat-online.jpg)

:quality(80)/p7i.vogel.de/wcms/88/0b/880b1539aba182d2b26dc2b5a3f0541e/0125283151v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/42/cb/42cbcb66dffa2ef6548d5fb2edee4b4a/0130519441v3.jpeg)