PCI-Express-Switching Leistungs- und Designanforderungen für PCIe

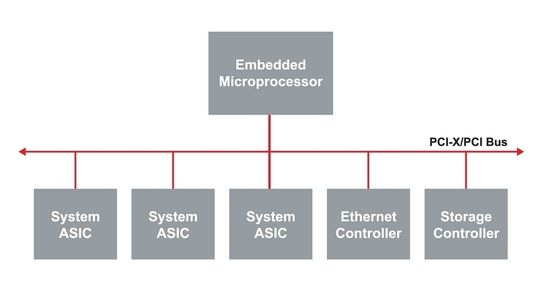

Parallelbus-Interconnect-Architekturen wurden aufgrund der Leistungsanforderungen und Einschränkungen beim physikalischen Aufbau zum Auslaufmodell. Der serielle Busstandard PCI Express (PCIe) entwickelte sich durch die traditionelle Dominanz herkömmlicher PCI-X- und PCI-Buskonzepte zum Defacto-Standard für die Verbindung zwischen Chips und Subsystemen.

Anbieter zum Thema

Embedded-Systeme, die längere Produktlebens- und Entwicklungszyklen als die Pionier-Anwendungen Server, Arbeitsstationen und Speichersysteme haben, schwenken nun auch auf PCIe um. PCIe bietet mehr Bandbreite, eine höhere Signalqualität und ein einfacheres System-Layout. In Bezug auf die Architektur sind dabei aber einige neue Punkte zu beachten, da die Umstellung von PCI-X und PCI auf PCIe mit einer Änderung der Interconnect-Topologie verbunden ist. Und diese Topologie benutzt mit dem PCIe-Switch auch eine neue Systemkomponente.

Parallele Protokolle wie PCI-X und PCI erfordern mit herkömmlichen Systemdesign- und Layout-Techniken einen erheblichen technischen Aufwand, um die hohen, für eine effiziente Nutzung der CPU- und Peripherie-Ressourcen erforderlichen Datenraten aufrechtzuerhalten. Diese Protokolle sind bei der Suche nach einem Kompromiss zwischen höherer Geschwindigkeit und kürzerer Leiterbahnlänge an ihren Grenzen angelangt. Die Forderung nach noch mehr Geschwindigkeit und Leistung, geringeren Systemkosten und schnellerer Markteinführung erzwingen eine Umstellung auf die serielle Interconnect-Technologie PCIe.

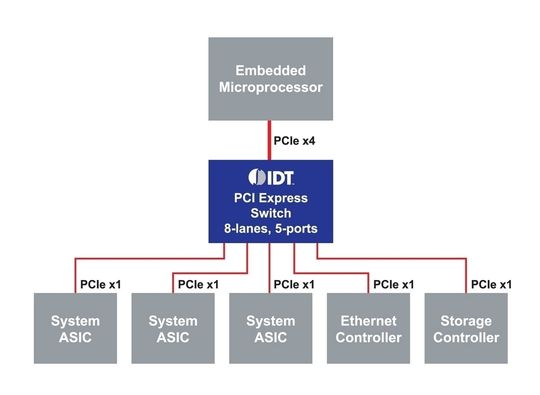

PCIe kann die wichtigsten Leistungs-, Strombedarfs-, Layout- und Kostenprobleme lösen: Takt- und Dateninformationen werden seriell in einen einzigen Datenstrom verpackt und hohe Übertragungsraten lassen sich ohne die Probleme eines herkömmlichen Daten-Skews erzielen. Weil serielle Punkt-zu-Punkt-Verbindungen mit höheren Datenraten arbeiten können, kann eine einzige serielle Datenstrecke die Daten übertragen, für die man früher eine große Anzahl von Datenleitungen samt zugehörigen Takt- und Steuersignalen benötigte. Folglich sind weniger Pins erforderlich und Board-Layouts werden einfacher (Bild 1).

PCIe-Switches für mehr I/Os und Eessourcen-Effizienz

Obwohl moderne Prozessoren, Systemsteuerungs-Chipsets und ASICs bereits mit PCIe ausgestaltet sind, stehen diese Ressourcen nur in begrenztem Umfang zur Verfügung. Außerdem passen sie selten zu den Systemanforderungen für einen Anschluss an Hochleistungs-I/Os und System-ASICs in Embedded-Anwendungen. Nutzt man ausschließlich die begrenzten CPU-Ressourcen, so werden die Prozessor-Ressourcen zu wenig ausgenutzt. Dies führt zu Einschränkungen bei der Systemflexibilität, beim Funktionsumfang und bei der Vermarktbarkeit des Systems. Mit dem Einsatz von PCIe-Switches lassen sich die begrenzten PCIe-Ressourcen im Bereich der Datenverarbeitung auf mehrere I/O-Endpunkte verteilen, was eine effiziente Nutzung der verfügbaren Bandbreite ermöglicht.

Die Einführung der Switches ist aber auch mit einigen neuen Problemen verbunden: Der Umstieg von einer in logischer Hinsicht flachen, busgestützten PCI-X-/PCI-Technologie zu einer hierarchischen PCIe-Topologie (Bild 2) und der daraus folgende Einsatz eines PCIe-Switches wirft Fragen auf: Wie wirkt/wirken sich die zusätzliche(n) Komponente(n) auf die Leistung aus, entstehen dabei Platzprobleme auf der Leiterplatte, und führt dies zu höheren Systemkosten? Diese Effekte lassen sich vermeiden oder auf ein Minimum reduzieren, wenn man auf drei Aspekte beachtet: Produktkonfiguration (in der Architekturphase), Switch-Leistung und Stromverbrauch.

Auswahl eines PCIe-Switches – Produktkonfiguration

Durch einen PCIe-Switch im Interconnect-Netzwerk wird die vormals flache busgestützte Struktur auf eine hierarchische Topologie umgestellt (Bild 3). Der PCIe-Switch ersetzt einen Teil oder die gesamte Connectivity, die zuvor vom Bus bereitgestellt wurde. Dabei sind drei Kriterien zu beachten, wenn das Produkt optimal ins Design passen soll: Die fundamentalste Überlegung betrifft die Anzahl von Knoten im vormaligen Bus, die durch den Switch ersetzt werden müssen. Jeder dieser Knoten entspricht einem Port im Switch oder einem Switch-Komplex, wenn mehrere PCIe-Switches erforderlich sind.

Nach Bestimmung der Port-Dichte für den Switch passt man in einem zweiten Schritt die Zahl der PCIe-Kanäle den Bandbreiten-Anforderungen eines jeden Ports an. Die gängigsten Schnittstellen-Anforderungen für Embedded-Anwendungen reichen von einfacher bis zu achtfacher Schnittstellenbreite. Jeder PCIe-Kanal steht für 2,5 Giga-Transfers pro Sekunde, sodass ein Portschnittstellendurchsatz von 2,5 bis 20 GBit/s möglich ist. Die erforderliche Portbreite hängt von den Connectivity-Anforderungen ab (ein Peripherieelement benötigt z.B. einen ×4-Port) oder von der Art des Datenverkehrs (auf der Steuerungsebene meist ×1-Ports, auf Datenebene ×4- oder ×8-Breite).

Die letzte Überlegung bei der Auswahl eines PCIe-Switches sollte sein, wie die Anzahl der Ports und Kanäle in die Familie verfügbarer Produkte passt. Die Marketing-Anforderungen werden sich im Laufe der Produktlebensdauer oder über einen Designzyklus zwangsläufig verändern, sodass zusätzliche Funktionen (weitere Switch-Ports oder -kanäle) oder Kostensenkungen (weniger Ports oder Kanäle) erforderlich sind. Bietet ein Halbleiterhersteller eine Familie von Lösungen mit einer breiten Auswahl kompatibler Bausteine für unterschiedliche Kanalzahlen und Port-Konfigurationen an, so kann der Entwickler sein System mit einem minimalen Aufwand an Hardware, Firmware und Software-Redesign skalieren.

Auswahl eines PCIe-Switches – Leistung

In Bezug auf die Leistung erwarten Systemarchitekten und Entwickler, dass sich PCIe-Switches „wie eine Leitung, nur schneller“ verhalten. Der neu eingefügte Switch im Interconnect-Netzwerk muss also so transparent wie möglich sein, und die Durchsatzleistung des Systems muss im Vergleich zur erwarteten Systemleistung ohne den Switch möglichst unverändert bleiben. Zwei wichtige Parameter eines PCIe-Switches gewährleisten bei Embedded-Anwendungen eine optimierte Durchsatzleistung: eine große Anzahl von Flow Control Credits (FCC) sowie die Unterstützung eines möglichst großen Maximum-Payload-Size-Wertes (MPS).

FCCs regeln im PCI-Protokoll die Rate der Traffic-Bewegungen zwischen den Systemelementen. Spezifische Transaktionen zwischen den PCIe-Link-Partnern werden über die Anzahl der verfügbaren FCCs geregelt. Systemelemente, die mit einer kleinen Anzahl von FCCs ausgestattet sind, verursachen Engpässe im System. Wenn ein Schnittstellenpartner viele Transaktionen mit einem anderen Partner durchführen muss, der seinerseits zur Annahme aller erforderlichen Transaktionen zu wenige FCCs besitzt, wird ersterer durch letzteren ausgebremst.

PCI-Switches mit einer großen FCC-Anzahl setzen wertvolle Systemressourcen frei und vermeiden Engpässe, indem sie als Pufferspeicher zwischen Rechnerressourcen und I/Os dienen. I/O-Komponenten sind vor allem in Embedded-Anwendungen oft nur mit wenigen FCCs ausgestattet, sodass die direkt als Schnittstellenpartner angeschlossenen Datenverarbeitungsressourcen ineffizient genutzt werden. Wenn man einen PCIe-Switch mit einer großen Anzahl an FCCs einfügt, kann der in der Hierarchie übergeordnete Mikroprozessor alle Transaktionen mit dem Switch durchführen und dann an anderen Aufgaben weiterarbeiten, während der Switch als Pufferspeicher fungiert. So lassen sich Transaktionen bei der niedrigeren, durch das I/O-Peripherieelement vorgegebenen Geschwindigkeit ausführen, ohne dass dazu eine Interaktion mit dem übergeordneten Prozessor erforderlich ist.

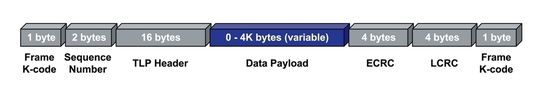

FCC-Ressourcen bestimmen die Geschwindigkeit, in der eine Datentransaktionen zwischen Schnittstellenpartnern ausgeführt wird. Der MPS-Wert hingegen definiert die Menge an Nutzdaten, die pro Transaktion übertragen werden. In PCIe werden die Daten in Transaction-Layer-Paketen (TLP) übertragen.

Ein solches Paket besteht aus einer festen Anordnung mit Header, Footer und Overhead-Bytes sowie der Paket-Nutzdaten, die von 0 bis 4 KByte lang sein können (Bild 4). Wenn ein PCIe-Interconnect Netzwerk große MPS-Werte unterstützt, so verbessert sich die Systemleistung, weil sich damit der Umfang der Overhead-Datenverarbeitung pro übertragenem Datenbyte verringert und die Auslastung des PCIe-Links steigt.

Auswahl eines PCIe-Switches – Stromverbrauch

PCIe-Switches zwingen den Systementwickler, sorgfältig auf Stromverbrauchsvorgaben und eine Flächenplanung auf der Leiterplatte zu achten. Die Erfüllung dieser Vorgaben allerdings nur einer der Vorteile stromsparender PCIe-Switch-Lösungen. PCIe-Switches, die für einen Strom sparenden Betrieb Best-in-Class-Entwicklungspraktiken einhalten, bieten zusätzliche Vorteile bei der Systementwicklung und auf der Kostenseite. Strom sparende Switches senken die Betriebskosten, weil sie keine Kühlkörper benötigen und damit auch keine Luft-Durchströmung über den Bauteilen im System. Außerdem belegen Strom sparende Switches Dank kleinerer Gehäuse, größerer Flexibilität bei der Bauteilplatzierung und dank höherer Integrationsdichte weniger Platz auf der Leiterplatte.

IDT bietet Systementwicklern eine Auswahl an PCIe-Switchinglösungen, von kleinen Bauteilen (PCIe-Switch mit drei Kanälen und drei Ports) bis zu großen Komponenten mit 64 Kanälen und 16 Ports. Mit insgesamt 30 PCI-Switchinglösungen deckt das Angebot eine Reihe von Kanal- und Port-Konfigurationen ab und ermöglicht damit eine Anpassung an das Zielprodukt. IDT demonstriert mit seinem Angebot eine wichtige Rolle bei Produktauswahl, Leistung und Stromverbrauch sowie bei der technologischen Umstellung auf die zweite Generation von PCIe-Lösungen. Auch in Zukunft wird das Unternehmen PCIe-Switchinglösungen mit großem Nachdruck weiterentwickeln.

*Matt Jones ist Marketing Manager der Serial Switching Division bei IDT, San Jose, Kalifornien.

(ID:236431)

:quality(80)/p7i.vogel.de/wcms/e9/ce/e9ce137e87eccac328ec5504c586c477/0129711019v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/68/46/684697b6eb687384e0d8c6803450401a/0130056395v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/0f/c0/0fc0d93c99a5d9066e58c39f41fb1b10/0130046764v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1d/d8/1dd8627e2323721d4ee5436f9401911e/0130147601v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/8e/d4/8ed4a2aa0bf362584aa1284f0adb2fdf/0130156040v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/65/f4/65f404dc6d19d4f1628ad7e49f6a22cf/0130136276v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fb/d3/fbd33264fcdf128866667be0a0a6b657/0130137877v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a5/5e/a55ec741a9c17cb890b2cb5bcb919477/0130162776v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/8d/fa8dedee195f29c33c89d86311c258ee/0130104146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cc/13/cc1378375499a26b5ddbb309d2155acb/0130085649v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/24/58/2458f1cae3100e375fbb8124f02c54af/0130111244v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/fc/fafc300481de3fd4d7f34400327d0d01/0130127049v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d2/cd/d2cd33084ab732ff8a600bc55ade1f47/0130096831v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/10/45/1045969e69a1db4aaa73d0f74f55cc02/0129962687v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c7/f6/c7f61d0437c7f8fca3c6ff947ba2ad62/0129322490v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/66/0c/660c31afa35398bac9be42f2be73fdc4/0129073529v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/af/35af7dd326d198475d06fbb69aa600b5/0130175971v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/2e/c02e7bf72bfc434888c37100e2511681/0130127767v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/95/a1/95a197490145b7afcfd4dc176a1b5ef9/0130096114v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bf/82/bf82f81061b759c454e15ec4c2e7560b/0130110139v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/74/96/74964a7715c738a9e8b17681445ceed3/0130103633v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/0d/18/0d183ecb569b03285578762658d2def6/0130061201v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/72/19/7219e53d462877119eaf0bd98783a46d/0129953146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6a/93/6a93991941467231d8798c8577882dfd/0130071573v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d3/76/d3760874d137b2f4bae5954b46dd5900/0130101582v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/42/de/42de87134adee379a83e5d633ba48c95/0130176499v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/90/0c/900ca1b73852ed45bd7e42a6119192dd/0130174841v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/5e/ed/5eed37b21283f8f364a37d025d53fa48/0130167146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bb/2a/bb2ac8404ae7b3f08a5c01d1ca0615a7/0130182922v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ef/9d/ef9dc7f8402f3f4ff42268e573921bc4/0130129635v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/68/7f/687fac7d01bdb/ag-2024-logo-4c.png)

:fill(fff,0)/p7i.vogel.de/companies/66/f6/66f673630a98a/logo-mc-rgb-300x300.png)

:fill(fff,0)/p7i.vogel.de/companies/62/3a/623ac694d217a/ept-connectors-rgb-quadrat.jpeg)

:quality(80)/p7i.vogel.de/wcms/5e/6b/5e6b5884a3188984c14796fdad74d307/0125018815v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/88/0b/880b1539aba182d2b26dc2b5a3f0541e/0125283151v2.jpeg)