Anbieter zum Thema

Darum sollten Oberflächen vor dem CAD-Layout festliegen

Es gibt seit Längerem ernstzunehmende Anzeichen dafür, dass die Oberfläche einer Leiterplatte schon vor der Erstellung des CAD-Layoutes festliegen muss. Ein erster Aspekt ist die allgemeine Tendenz zu High-Speed-Baugruppen. Es gibt erste Hinweise, dass bei sehr schnellen Signaltransfers mit hohen Datenraten >5 GBit/s die Signalqualität leidet, wenn auf dem Weg von der Leiterplatte zum Bauteilanschluss eine Nickelschicht durchlaufen werden muss (wie das bei chemischen Goldoberflächen der Fall ist).

Ein zweiter Aspekt ist die Legierung der Bauteilanschlusskappen insbesondere bei zweipoligen Komponenten. Beim Löten bildet sich aus Lot und Leiterplattenoberfläche eine Legierung, die den Bauteilanschluss benetzen muss. Die Legierung mancher Bauteilanschlusskappen spricht auf die üblichen Lote und Oberflächen nicht an. Es kommt in Folge zu unzuverlässigen und damit riskanten Lötverbindungen. Abhilfe kann eigentlich nur eine Datenbank ermöglichen, mit deren Unterstützung zum Zeitpunkt der Bauteilplatzierung am CAD-System das vorgesehene Lot und die vorgesehene Leiterplattenoberfläche auf Prozessierbarkeit hinsichtlich der Benetzung abgeglichen werden kann. Aber das ist wohl vorerst noch Utopie. Für eine Einschätzung der Oberflächen sollten deren wichtigste Eigenschaften bekannt sein.

Hot-Air-Leveling (HAL)

HAL erlebt in der bleifreien Ausführung mit SnAgCu-Loten eine Renaissance. Die Planarität der Oberfläche ist jedoch mittelmäßig, die Schichtdicke ist unregelmäßig, die Kantenabdeckung der Lötflächen ist nicht immer perfekt und die Lötflächen selbst weisen schon mal lokale Benetzungsfehler auf. Die Schichtdicke liegt sehr variabel zwischen 1 und 20 µm. Der Energieverbrauch des HAL-Prozesses ist hoch. Für die Leiterplatte ist die Temperaturbelastung durch den Fertigungsabschnitt HAL beachtlich und führt zu einer deutlichen Voralterung.

Chemisch Zinn

Die Chemisch-Zinn-Oberfläche ist plan. Die Zinndicke liegt bei 1 bis 1,2 µm (optimal). Als Mindestdicke für die Zinnschicht werden 0.3 µm für eine zuverlässige Lötverbindung gefordert. Mit der Zeit baut sich die Dicke der lötbaren Zinnschicht durch die Bildung einer intermetallischen SnCu-Phase ab. Bereits das Trocknen der Leiterplatte leistet einen massiven Wärmeeintrag, der diesen Vorgang beschleunigt. Bei einer Temperatur von 120 °C wird innerhalb einer Stunde die Dicke der Zinnschicht um zirka 50 nm reduziert. Jeder Reflowlötprozess halbiert die Dicke der verbleibenden Zinnschicht. (Quelle: Atotech/Investigation of the recommended Immersion Tin thickness for lead free soldering). Ausgehend von einer Zinndicke von 1,2 µm bedeutet dies eine verbleibende Zinndicke von 0,6 µm nach dem ersten Reflowlöten und 0,3 µm nach dem zweiten Reflowlöten.

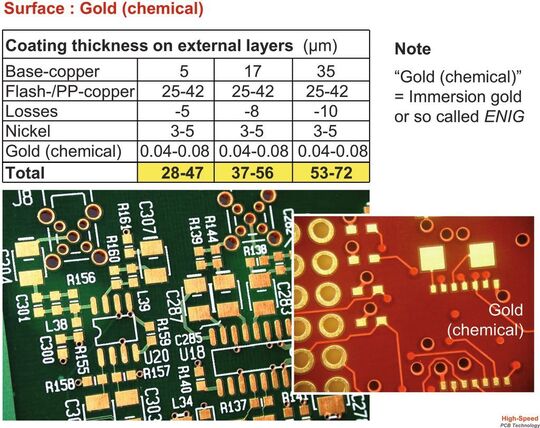

Chemisch Gold

Chemisch Silber

Chemisch Silber wird in Europa noch wenig nachgefragt. Die Oberfläche ist plan. Die Schichtdicke liegt bei 0,1 bis 0,4 µm und ist mit einer dünnen organischen Schutzschicht abgedeckt. Mit Kupfer bildet Chemisch Silber keine intermetallische Phase. Das Beschichtungsverfahren ist in einem einfachen und preisgünstigen Prozess ohne hohe Temperaturbelastung durchführbar. Die Oberfläche ist gut lötbar. Die Lagerzeit von Leiterplatten mit einer Oberfläche aus Chemisch Silber wird auf ein Jahr taxiert. Chemisch Silber reagiert empfindlich auf ein chlorid- und/oder sulfidhaltiges Umfeld. Dazu gehören auch bereits Verpackungsmaterialien, die Chloride und/oder Sulfide enthalten.

Unvorhersehbare Wechselwirkungen

Ohne Chemie geht in der Leiterplattentechnologie nichts. Oberflächen müssen gereinigt, ölige Beläge, Oxide und Fette müssen entfernt werden. Leiterplatten werden mit einer Fülle unterschiedlicher chemischer Substanzen in Kontakt gebracht. Säuren, Laugen, Sulfate, Fluorverbindungen werden begleitet von geringer dosierten chemischen Zusatzstoffen, die helfen sollen, chemische Prozesse zu aktivieren, zu stabilisieren oder zu katalysieren. Welcher Prozess mit welchen Substraten abläuft, ist nicht immer hinreichend bekannt. Für alle Endoberflächen gibt es voneinander abweichende chemische Systeme, die eingesetzt werden können. Die Inhaltsstoffe sind im Detail das Knowhow des jeweiligen Chemielieferanten.

Die Wechselwirkungen zwischen der Chemie der Oberfläche und der Chemie des Lötstoplackes (und dann später auch der Chemie des Via-, Carbon-, Heatsinkpasten- und Abziehlackdruckes) sind nicht immer vorhersehbar. Die Rückstände diverser chemischer Substanzen auf den Leiterplatten können problematisch werden. Niederschläge auf den Lötflächen, Mikrovias, zu enge Lötstopmasken, hohe Kupferschichtdicken, Mikrokavernen im Basismaterial, winzige Hohlräume zwischen den diversen Siebdrucken und der Leiterplattenoberfläche tragen dazu bei, daß auf der Leiterplatte Rückstände nach dem Aufbringen des Lötstoplackes und der Endoberfläche sowie nach dem Fluxen und dem Löten der Baugruppe verbleiben. Mögliche Langzeitschäden für Baugruppe sind bisher weitestgehend unerforscht und im Erlebensfall auch nur äußerst schwer zu analysieren und einer Ursache zuzuordnen.

* * Arnold Wiemers ... ist Mitinhaber der LA-Leiterplattenakademie GmbH, Berlin

(ID:29399150)

:quality(80)/p7i.vogel.de/wcms/46/7c/467c0afffbfd10c3553c2888a4a6289f/0130479810v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/12/3d/123d9eb2c2e4ce13296371a2ad3718a4/0130412664v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d8/78/d878b7bfc23826e6ddfce42443836d28/0130384280v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/13/20/13208d1c2797edd67d9ff216b403726b/0130471595v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/38/cb/38cbe19e814dd30b94780bc3946547ab/0130446533v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a3/3e/a33e6d8a927d539ec6c3a0537f48f0f1/0130440028v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6b/61/6b61373f1c3f06f7f9343e6b0f0e9cc8/0130225062v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/15/93/1593dd152e6d58c5fc5da0d331777c54/0130357398v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/88/c28805ea7b2261235475146a5b0c61f8/0130313028v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/8d/fa8dedee195f29c33c89d86311c258ee/0130104146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cc/13/cc1378375499a26b5ddbb309d2155acb/0130085649v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6d/91/6d91abfa1b16ffcf470c7147facd7aa8/0130387695v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/85/b0/85b0b32128f6d1968e975043f1e0b67b/0130342166v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/1a/53/1a539631c940d184689460600bd2b395/0130410666v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/10/45/1045969e69a1db4aaa73d0f74f55cc02/0129962687v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c7/f6/c7f61d0437c7f8fca3c6ff947ba2ad62/0129322490v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/e4/bae4e54395e5a53088060531ef99b814/0130359274v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/af/35af7dd326d198475d06fbb69aa600b5/0130175971v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/2e/c02e7bf72bfc434888c37100e2511681/0130127767v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/7c/04/7c04916c305164fb10bc6cb05b51d934/0130431065v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/64/e5/64e5e333492f182ab7df5ab4c2b54c1e/0130463252v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/0a/95/0a95db4508128c4e11d5d268bf2c0a77/0130440053v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b3/65/b365dd5433c8b6d36c56c92b72f5b368/0130401081v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/85/c0/85c0cdd8fd326013aed52ca96777c998/0130426877v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f0/78/f07826d6c4e995980f1ada3377416aac/0130403626v4.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/c8/b6c8f7732da417bda3d298412f4c0ed8/0130453104v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/47/ce/47ce64bad7990f276f68cbb24505f6dd/0130472850v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/15/56/15564dea31861c376a385658c3b961a3/0130465243v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/98/ad/98ad595a6372aae8dbeac71681d23f41/0130450258v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bf/2a/bf2aad428ab1a80e6738fdbdc2efeb7e/0130453420v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/62/3a/623ac694d217a/ept-connectors-rgb-quadrat.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/60/f6/60f6829670d63/beta-layout-logo.jpeg)

:quality(80)/p7i.vogel.de/wcms/bc/ec/bcec7c262091ac4d6c3b8378a424d814/0127459210v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/49/91/4991cf24a662496cbf87c788032778f6/0128623861v2.jpeg)