Hochfrequenztechnik Hochfrequenzboard: Theorie versus Prozesstoleranzen (Teil 3)

Im dritten Teil der Reihe liegt der Fokus auf der hochfrequenztechnischen Charakterisierung und prozesstechnischen Realisierung von Leiterzügen und Durchkontaktierungen.

Anbieter zum Thema

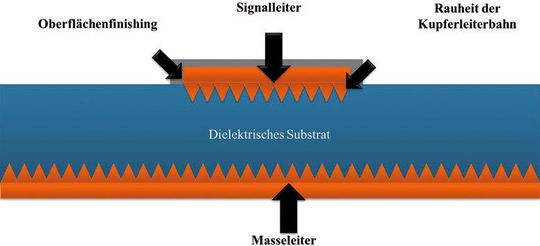

Durch Hochfrequenzeffekte wird die Stromverteilung in den Leitern der Mikrostreifenleitung so beeinflusst, dass der Hauptstromfluss auf der den Substrat zugewandten Seiten auftritt. Prozessschwankungen der Substratdicke und der Signalleiterbreite haben einen großen Einfluss auf die elektrischen Eigenschaften.

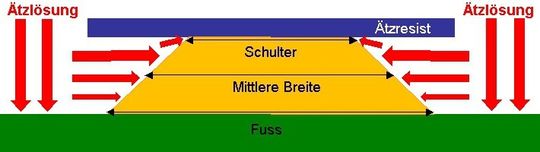

Die Strukturierung des Leiterbildes einer Leiterplatte erfolgt durch fotolithografische Prozesse mit anschließendem Ätzen der im Ätzresist freigelegten Kupferbereiche.Der nasschemische Ätzprozess, je nach Technologie in saurem oder alkalischem Milieu, ist ein isotroper Prozess. Das bedeutet: Der Ätzangriff erfolgt unabhängig von der gewünschten Ätzrichtung und bewirkt eine Unterätzung, die auch als Undercut bezeichnet wird. Diese Unterätzung ist ein absoluter Wert und von der zu ätzenden Kupferdicke und der eingestellten Ätzrate abhängig. Die Verkleinerung der Leiterzüge fällt daher bei schmalen Leiterzügen prozentual höher aus als bei breiten Leiterzügen, was speziell bei kontrollierten Impedanzen zu beachten ist.

Leiterbahntoleranzen und Einschränkung des Toleranzraums

Der optimale Ätzprozess zeichnet sich durch einen hohen Ätzfaktor (Verhältnis Ätztiefe zu Unterätzung, idealerweise Fußbreite = Schulterbreite einer Leiterbahn) sowie ein gleichmäßiges,kleines und zuverlässig reproduzierbares Toleranzfeld (Spanne zwischen minimalen und maximalen Istwerten) der finalen Leiterbahnbreiten aus. Letzteres ist zumindest auf dem einzelnen Fertigungspanel gefordert, besser noch je Fertigungslos.

- Verringerung der zu ätzenden Kupferdicke (bei Außenlagen Pattern-Plating mit dünnem Basiskupfer),

- Gleichmäßige Kupferstärken (optimierte Prozessführung),

- Dynamic Swell (automatisierte, dem Layout angepasste, lokal unterschiedliche Ätzzugaben der Leiterbreiten),

- Anpassung des Layouts (Ausgleichspads),

- Sonderprüfungen und sequentielles Ätzen.

Kritische Leiterzüge sollten deshalb hinsichtlich der Maßhaltigkeit (relative Abweichung vom Layout) so breit wie möglich gelayoutet werden und auf den Innenlagen platziert werden. Mit Hilfe dieser Optimierungsmöglichkeiten können Genauigkeiten der charakteristischen Impedanz von 50 ± 2 Ohm erreicht werden.

:quality(80)/images.vogel.de/vogelonline/bdb/701400/701406/original.jpg)

Hochfrequenztechnik

Hochfrequenzboard: Theorie versus Prozesstoleranzen

(ID:42741868)

:quality(80)/p7i.vogel.de/wcms/e9/ce/e9ce137e87eccac328ec5504c586c477/0129711019v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/68/46/684697b6eb687384e0d8c6803450401a/0130056395v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/0f/c0/0fc0d93c99a5d9066e58c39f41fb1b10/0130046764v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1d/d8/1dd8627e2323721d4ee5436f9401911e/0130147601v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/8e/d4/8ed4a2aa0bf362584aa1284f0adb2fdf/0130156040v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/65/f4/65f404dc6d19d4f1628ad7e49f6a22cf/0130136276v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fb/d3/fbd33264fcdf128866667be0a0a6b657/0130137877v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a5/5e/a55ec741a9c17cb890b2cb5bcb919477/0130162776v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/8d/fa8dedee195f29c33c89d86311c258ee/0130104146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cc/13/cc1378375499a26b5ddbb309d2155acb/0130085649v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/24/58/2458f1cae3100e375fbb8124f02c54af/0130111244v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/fc/fafc300481de3fd4d7f34400327d0d01/0130127049v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d2/cd/d2cd33084ab732ff8a600bc55ade1f47/0130096831v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/10/45/1045969e69a1db4aaa73d0f74f55cc02/0129962687v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c7/f6/c7f61d0437c7f8fca3c6ff947ba2ad62/0129322490v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/66/0c/660c31afa35398bac9be42f2be73fdc4/0129073529v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/af/35af7dd326d198475d06fbb69aa600b5/0130175971v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/2e/c02e7bf72bfc434888c37100e2511681/0130127767v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/95/a1/95a197490145b7afcfd4dc176a1b5ef9/0130096114v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bf/82/bf82f81061b759c454e15ec4c2e7560b/0130110139v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/74/96/74964a7715c738a9e8b17681445ceed3/0130103633v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/0d/18/0d183ecb569b03285578762658d2def6/0130061201v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/72/19/7219e53d462877119eaf0bd98783a46d/0129953146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6a/93/6a93991941467231d8798c8577882dfd/0130071573v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d3/76/d3760874d137b2f4bae5954b46dd5900/0130101582v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/42/de/42de87134adee379a83e5d633ba48c95/0130176499v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/90/0c/900ca1b73852ed45bd7e42a6119192dd/0130174841v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/5e/ed/5eed37b21283f8f364a37d025d53fa48/0130167146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bb/2a/bb2ac8404ae7b3f08a5c01d1ca0615a7/0130182922v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ef/9d/ef9dc7f8402f3f4ff42268e573921bc4/0130129635v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/60/f6/60f6829670d63/beta-layout-logo.jpeg)

:quality(80)/p7i.vogel.de/wcms/2c/40/2c40cea54250c0cc97dbc8d8448798a5/0129385029v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/5f/ec/5fec83dcdc9f1feef1000a5e14004423/0127093638v2.jpeg)