Transistortechnik Geringerer Stromverbrauch und höhere CMOS-Skalierung mit DDC-Technologie von SuVolta

„Deeply Depleted Channel“ ist das Schlagwort, das SuVolta als Entwickler skalierbarer Low-Power-CMOS-Technologien verwendet, wenn es um die stromsparende Transistortechnik des Unternehmens geht. Was steckt dahinter?

Anbieter zum Thema

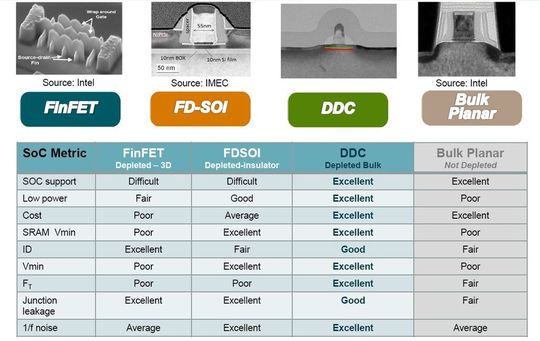

SuVoltas DDC-Technologie ist ein Bestandteil der eigenen Low-Power-CMOS-Plattform PowerShrink und soll die Verlustleistung um 50% senken, ohne dass sich dadurch die Arbeitsgeschwindigkeit verringert. In Verbindung mit Spannungsskalierungstechniken könne DDC die Leistungsaufnahme sogar um 80% oder noch mehr reduzieren, erklärte Jeff Lewis, Senior Vice President Marketing and Business Development bei SuVolta.

Mit der Technologie lassen sich der Stromverbrauch reduzieren, die Betriebsspannung verringern und Prozesse in den Sub-20-nm-Bereich herabskalieren, so Lewis. Dabei wird die Schwellenspannungsstreuung (VT) verringert, was eine weitere Herabskalierung von CMOS-Transistoren ermöglicht.

Das Charakteristische dieser Struktur sei, dass beim Anlegen einer Spannung an das Gate eine tiefe Ladungsträger-Verarmung im Kanal auftritt. Der DDC-Transistor besteht in einer typischen Implementierung aus mehreren Bereichen – einem undotierten oder sehr schwach dotierten Bereich, einem Schwellenspannungs-bestimmenden Offset-Bereich und einem Screening-Bereich. Die Details der Implementierung von SuVoltas DDC-Transistor können je nach Wafer-Produktionsprozess und spezifischen Anforderungen an das Chip-Design variieren.

Höhere Elektronenmobilität für besseren Stromfluss

Der undotierte oder sehr schwach dotierte Bereich entfernt die Dotierstoffe aus dem Kanal und ermöglicht dadurch eine tiefe Verarmung des Kanals. Dies verringert die RDF (Random Dopant Fluctuation, zufällige Dotierstoffstreuung), wodurch es möglich wird, die Versorgungsspannung (VDD) herabzuskalieren; außerdem erhöht sich die Elektronen Mobilität und damit der effektive Strom.

Der Offset-Bereich bestimmt die Höhe der Schwellenspannung, ohne die Elektronenmobilität herabzusetzen. Dieser Bereich verbessert außerdem das Sigma-VT im Vergleich zu herkömmlichen Transistoren. Der Screening-Bereich screent die Ladung und bestimmt die Tiefe der Verarmungszone. Er dient außerdem als Body für dynamische VT-Steuerung, falls dies gewünscht wird.

Der DDC-Transistor ermöglicht es, die Betriebsspannung und damit die Verlustleistung zu verringern. Aufgrund der geringeren VT-Streuung bieten Chips auf der Basis von SuVoltas DDC-Technologie folgende Vorteile:

- 30% geringere Betriebsspannung ohne Performance-Einbußen;

- wesentlich kleinere Leckströme;

- weniger Design-Guard-Banding;

- höhere Fertigungsausbeute.

Schwellenspannung gezielt variieren

Zudem erlauben es DDC-Transistoren, die Schwellenspannung gezielt zu variieren; das ist bei modernen, stromsparenden Produkten ein wichtiger Aspekt. Außer der kleineren VT-Streuung haben DDC-Transistoren noch andere Vorzüge, die zur weiteren Verringerung der Leistungsaufnahme bei höheren Arbeitsgeschwindigkeiten beitragen:

- höhere Kanalmobilität für höheren Treiberstrom;

- geringeres DIBL (Drain Induced Barrier Loading);

- größerer Body-Koeffizient für genauer kontrollierte VT

„Irgendwann kommt der Zeitpunkt, an dem eine weitere Verkleinerung des Chips nicht mehr sinnvoll ist, weil aufgrund der steigenden Lithografiekosten die Kosten pro Transistor nicht mehr weiter sinken und dadurch das Moore'sche Gesetz nicht mehr gilt“, so Lewis, „mit den 28- und 20-nm-Knoten nähern wir uns diesem Zeitpunkt; diese Knoten werden langlebig sein“.

Lesen Sie weiter: DDC kompatibel zu modernen CMOS-Prozessen

Artikelfiles und Artikellinks

(ID:30800500)

:quality(80)/p7i.vogel.de/wcms/37/ec/37ece4c276f37114e8f40696ff5dcd66/0130537789v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/46/7c/467c0afffbfd10c3553c2888a4a6289f/0130479810v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/12/3d/123d9eb2c2e4ce13296371a2ad3718a4/0130412664v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/e7/b6e755d9e704319c0bb59dc1ac2d67e8/0130537290v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/8b/10/8b10d1edceb749de99c1df3ad97be01e/0130564619v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ac/da/acda3bafe46d3bf8e104a2a7bc2ac557/0130535476v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ca/9b/ca9b681785123f9700518a46897f9779/0130428786v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/38/cb/38cbe19e814dd30b94780bc3946547ab/0130446533v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/88/c28805ea7b2261235475146a5b0c61f8/0130313028v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/8d/fa8dedee195f29c33c89d86311c258ee/0130104146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/7a/697a270ed7538378d1fbc0f0b240ed25/0130534691v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/e7/a4/e7a4e048491e60cb30e22a860f5d68bc/0130519425v4.jpeg)

:quality(80)/p7i.vogel.de/wcms/1b/f0/1bf02d41e3eac721823841a4c1228753/0130519149v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1a/53/1a539631c940d184689460600bd2b395/0130410666v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/10/45/1045969e69a1db4aaa73d0f74f55cc02/0129962687v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/e4/bae4e54395e5a53088060531ef99b814/0130359274v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/af/35af7dd326d198475d06fbb69aa600b5/0130175971v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/2e/c02e7bf72bfc434888c37100e2511681/0130127767v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/8c/42/8c4211320be4a5ef78ca36d37b2406f2/0130561321v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e1/0b/e10bc04827e33786548587e32bbae422/0130438700v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/06/3506f2a8d33a696aaef12a30771bd8d8/0130496747v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/ed/e5ed08c670c44565a9130e95a760dddc/0130494578v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/7a/c07aaa9f6122aeb6faed4f2a74dcb77f/0130542642v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/3a/72/3a722ed2ad6ac4894c352e6ce87b6560/0130567207v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e4/d1/e4d122a8ecce14b98c8298c1cc130194/0130561462v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1c/33/1c3399d0f7fb55bda7808310088accaf/0130565746v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/3c/55/3c5505dd3ca3971cddd09c583a4c907d/0130458429v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/2e/95/2e9597b5dc1873771c7fe9c32ac41e82/0130549010v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/15/56/15564dea31861c376a385658c3b961a3/0130465243v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/110300/110321/65.png)

:fill(fff,0)/p7i.vogel.de/companies/69/7c/697cbb83628bc/logo-16-9.png)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/68800/68851/65.jpg)

:quality(80)/p7i.vogel.de/wcms/21/a0/21a0a3a0a3ef05b6cf4d3cdb4f0d04bf/0128508030v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/60/be/60beb5d8108bed67fdee441584fc22ba/0125323087v1.jpeg)