Schaltnetzteile desigen Bewährte Layout-Konzepte für Schaltnetzteile

Ein gutes Layout ist die entscheidende Vorraussetzung für eine optimale Leistungsfähigkeit einer Baugruppe. Anhand des Designs eines Schaltnetzteils werden in diesem Beitrag die wichtigsten Techniken beschrieben.

Anbieter zum Thema

Schaltnetzteile setzen sich in der Regel aus Leistungsbausteinen zum Schalten hoher Spannungen und Ströme sowie Kleinsignal-Bauelementen für analoge Signale geringer Amplitude zusammen. Diese Komponenten sind auf relativ engem Raum konzentriert. Beim Ausarbeiten des Layouts für eine Netzteil-Platine kommt es darauf an, sämtliche Bauelemente so zu platzieren und miteinander zu verbinden, dass die leistungsstarken Ströme keine schädlichen Auswirkungen auf die schwachen Kleinsignale haben. Mangelhaftes Layout führt zu unerwünschten Spannungs- und Stromspitzen, die nicht nur den Gleichspannungen innerhalb des Netzteils überlagert werden, sondern als elektromagnetische Interferenzen (EMI) auch auf benachbarte Systeme einwirken können.

Erster Schritt – Platzierung der Leistungsbausteine

Nach dem Import des Schaltplans für ein Schaltnetzteil in eine Leiterplatten-Editierumgebung fällt die Entscheidung darüber, wie die vielen diskreten Bauelemente auf der Platine anzuordnen und miteinander zu verbinden sind, unter Umständen nicht leicht. Die Mehrzahl der Netzteile wird auf mehrlagigen Leiterplatten mit mindestens vier Kupferlagen implementiert, wobei der Großteil der Platinenfläche von den Leistungsbausteinen, also den Ein- und Ausgangs-Kondensatoren, den MOSFETs, den Stromabtast-Widerständen oder Übertragern, den Gleichrichtern und den Induktivitäten eingenommen wird. Da über diese Bauteile hohe Ströme fließen, sind sie mit breiten Leiterbahnen untereinander zu verbinden und sollten zuerst platziert werden.

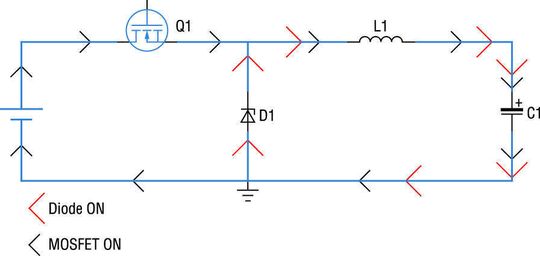

Als erstes sollten die Schleifen mit hohen di/dt-Werten, also mit steil ansteigenden und abfallenden hohen Schaltströmen ermittelt werden, um sie so kompakt wie möglich zu machen. Nur so lässt sich die Streuinduktivität minimieren, die zu unerwünschten Spannungsspitzen führen würde.

Bild 1 macht deutlich, wie sich solche Schleifen herausfinden lassen. Die kleinen schwarzen Pfeile geben die Richtung des zirkulierenden Stroms bei eingeschaltetem MOSFET an, während die großen roten Pfeile die Stromschleife bei leitender Diode markieren. Sämtliche Stromwege, die entweder mit einem schwarzen oder einem roten Pfeil (nicht aber mit beiden) gekennzeichnet sind, weisen steile Stromanstiege bzw. Abfälle auf.

Elektromagnetische Störstrahlung minimieren

Source-Ströme und die entsprechenden Rückströme sollten möglichst unmittelbar über oder nebeneinander fließen, damit die von der Stromschleife umschlossene Fläche möglichst klein ist und entstehende elektromagnetische Felder auf ein Minimum reduziert werden. Die eingangsseitig zugeführte Leistung sollte von den Schaltfunktionen unmittelbar am Eingangs-Kondensator abgenommen werden. Ebenso ist es sinnvoll, die ausgangsseitige Leistung direkt am Ausgangs-Kondensator abzunehmen. Die einzelnen Schaltungsknoten sind entsprechend der Höhe und der Art des sie durchfließenden Stroms zu dimensionieren.

Knoten mit hohen di/dt-Werten, wie zum Beispiel der Schaltknoten (in vielen Topologien ist dies der Punkt, an dem MOSFET, Gleichrichter und Induktivität verbunden sind), sollten einerseits so klein wie möglich und andererseits ausreichend groß für die zu erwartende Stromstärke bemessen sein. Indem man die Größe dieser Knoten minimiert, wird auch die Störstrahlung erzeugende Fläche auf ein Minimum verringert. Niederohmige, nicht mit Störungen behaftete Knoten, wie etwa Masse oder Ausgang sind dagegen so groß wie möglich zu dimensionieren.

Per Formel zur Dicke der Kupferschicht

Leiterbahnen und Kupferflächen, über die die Ströme zwischen verschiedenen Leistungs-Bausteinen fließen, sind hinreichend breit zu wählen. Gleichung 1 gibt die minimale Leiterbahnbreite für einen bestimmten Strom an (gültig für Ströme von 1 bis 20 A):

T = 2/gCu x (–1,31 + 5,813xI + 1,548xI2 – 0,052xI3)

Darin steht T für die Leiterbahnbreite (Einheit: mil; 1 mil = 1/1000 inch = 0,0254 mm), I für die Stromstärke in Ampere und gCu für das Kupfergewicht in Unzen (1 oz = 28,35 g).

Bei Einhaltung dieser Formel ist sichergestellt, dass die Temperaturzunahme der Leiterbahnen unter Vollast nicht größer als 10 K ist. Für einen Strom von 1 A errechnet sich bei einer 1-oz-Kupferkaschierung eine Leiterbahnbreite von 12 mil, d.h. 0,3 mm, während es bei 5 A und ½ oz Kupfer 240 mil (6,1 mm) sind, bei 20 A und ½ oz Kupfer sogar schon 1275 mil (32,4 mm).

Wenn ausreichend Platz ist, besonders aber bei Schaltströmen, sollten die Breiten größer gewählt werden. Anzustreben ist eine Breite von 30 mil/A (0,76 mm/A) bei 28,35 g (1 oz) Kupferbeschichtung bzw. von 60 mil/A (1,52 mm/A) bei 14,18 g (½ oz) Kupfer. Pfade mit hohen Stromstärken sollten mit Kupferflächen verbunden werden. Geht es um Ströme über 10 A, sollten Flächen auf mehreren Lagen benutzt werden, die durch Vias verbunden sind.

(ID:208787)

:quality(80)/p7i.vogel.de/wcms/ce/09/ce09cbfd70dd50b7f8e9e923c4fd8f3d/0129481054v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/59/bf/59bfd2822d711b0ae2cb9383b679f38d/0129302533v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c1/94/c19403fe0194686b2f4911be7e1e9539/0129294209v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ca/81/ca81333a02b8c934dcad5c1745435a3d/0125018126v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/06/ce/06cece1c695ea91c5108cf7f583feea5/0129540778v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/79/33/7933c5529f1bbc132e7935d7c53b6beb/0129501631v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/3f/69/3f69e2ac28f7f9ee735680c5e5d53d94/0129470810v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/7b/57/7b5725dd2e7545ab4904a9b7a3735721/0129309389v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b1/77/b1770e7d7499d7f807a2d5236dc081c8/0129461958v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9d/f7/9df7b15f177b8b3ca0e93cf965a476bc/0129529705v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/67/3f/673f67f2c8dbef2f0f6a5d01ec1f5ec6/0129505643v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1d/e5/1de5e11918cfb261b8b5c4632fc1f7db/0129456364v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/e8/a8/e8a8a953c77af9bbf208cce6454139d4/0129427931v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/61/85/6185c7a5619aba866e3b237690bea839/0129334467v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/c7/f6/c7f61d0437c7f8fca3c6ff947ba2ad62/0129322490v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/66/0c/660c31afa35398bac9be42f2be73fdc4/0129073529v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9c/35/9c35ed04fa562b190cbc496a695a6802/0128823288v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/d7/e6/d7e6fe4124ec2efc726e9c3f2c2a4cfc/0128241940v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/8f/bf/8fbf2cfa5f7238e41e046b12e936212b/0129541806v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/fc/4f/fc4f36089dac773f0b9483eb39a726a1/0129508876v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bc/42/bc42dd0a04818f6195a7f78bcec88be6/0129484567v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/14/63/14635e09eff181f7ab7a0f81ffa0daa3/0129407664v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ff/e4/ffe44f0dcf0fc0323926b1bc0a60d94f/0129386849v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a7/8c/a78c5f851db209abb1540909918fbf4a/0129260768v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/38/1d/381de324bbe6d190a95169372a8ca02b/0129540692v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/87/4e/874eb8316b30d4b79793576f26c7dc62/0129542275v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/62/1c/621cb1390951d6ac4029cd471edf956d/0129543495v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/2c/60/2c60940d2ebd2d45765085bc69488764/0129530286v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a6/a8/a6a880c57faa551baeca28d4178de438/0129419457v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6a/cc/6acc4f803241cfe5b6d60560c0a2b4d9/0126684948v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ef/aa/efaae5a25fb0a4c55c434611033447af/0126532350v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/60/f6/60f6829670d63/beta-layout-logo.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/68/25/6825cd91dbb00/logo-pp-rot-quadratzuschnitt-inv512px.png)

:fill(fff,0)/p7i.vogel.de/companies/68/62/68621fc4f1d39/logo.png)

:quality(80)/p7i.vogel.de/wcms/66/c1/66c14543fd48c69fe35aeca2e513966a/0125007023v5.jpeg)

:quality(80)/p7i.vogel.de/wcms/02/a6/02a682df26d6719ff336c961bd08213f/0125019920v2.jpeg)