System-in-Package-Technologie Ansätze und Realisierungsmöglichkeiten für SiP-Aufbauten

Hetero System Integration oder System-in-Package-(SiP-)Technologien vereint alle Komponenten für Sensorik, elektrische Signal- und Datenverarbeitung, drahtlose Kommunikation und Stromversorgung zu einem Mikrosystem innerhalb eines Gehäuses. Gegenüber der Systemintegration auf Chip-Ebene (System-on-Chip) rechnet sich dieses Verfahren schon für kleinere Stückzahlen jenseits der Massenmärkte.

Anbieter zum Thema

Das Konzept der SiPs geht auf die ersten Hybridschaltungen zurück, gefolgt von Multi-Chip-Modulen (MCM) mit mehreren aktiven und passiven Komponenten. Auf Halbleiterseite führte das Stapeln mehrerer Chips zu Stacked-Die-Packages und damit zu einer höheren Integration in der dritten Dimension. Typische Vertreter sind moderne Speicherbausteine, bei denen mehrere dünne Dice in einem Gehäuse übereinander montiert, die Speicherkapazität vervielfachen.

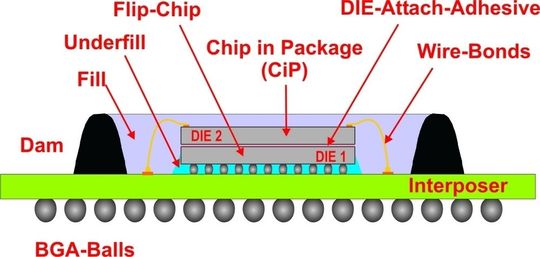

Beim SiP (Bild 1) werden zusätzlich sensorische, aktorische und signalverarbeitende Funktionen zu einem intelligenten Gesamtsystem verknüpft. Durch das Übereinanderstapeln mehrerer SiPs lassen sich vertikal integrierte 2,5D-SiP oder auch so genannte Package-on-Package (POP) realisieren, die zusätzlich die dritte Dimension nutzen.

Die wesentlichen Vorteile von SiPs sind:

- kostengünstige Integration verschiedener Halbleiter- und SMD-Technologien in einem Package;

- Verwendung von Standard-SMD-Bauteilen möglich;

- Erhöhung der Funktionalität und Performance bei gleichzeitiger Verringerung von Baugröße, Gewicht und Stromverbrauch;

- optimale Systemlösungen durch angepasste, miniaturisierte Gehäuselösungen;

- wirtschaftliche Prüfbarkeit, da kleine Moduleinheiten;

- kurze Innovationszyklen, durch kurze Entwicklungsdauer und schnelle Umsetzbarkeit (Time-to-Market)

Der Forderung nach größtmöglicher Miniaturisierung wird man gerecht, indem man mehr Funktionalität auf einem Halbleiter, als System-on-Chip (SOC) integriert. Dies kann bei der Kombination unterschiedlicher Halbleitertechnologien große Anstrengungen, hohe Investitionskosten und lange Vorlaufzeiten erfordern und ist daher nur bei großen Stückzahlen sinnvoll.

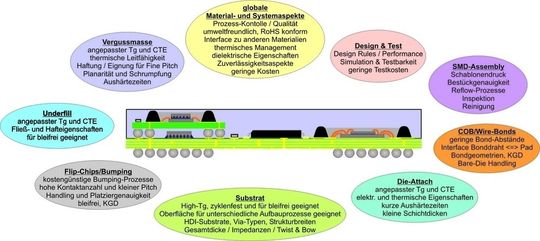

Bei der Integration in einem SiP sind bedingt durch die Vielzahl der eingesetzten Aufbau- und Verbindungstechnologien die unterschiedlichsten, technologische Aspekte zu berücksichtigen. Eine Auswahl der wichtigsten zeigt Bild 2. In SiPs, setzt man mikropassive Bauelemente wie 0402-, 0201- oder auch 01005-SMD-Gehäuse ein. Aktive Bauelemente werden in den kleinsten verfügbaren Gehäusen, wie MSOP-, BGA-, CSP- oder QFN- Gehäusen, aber auch als Nacktchips (Bare-Dice) in Flip-Chip- oder Wire-Bond-Technologie, verwendet.

Der Vorteil vom Bare Die ist der geringe Platzbedarf gegenüber Standard-SMD-Gehäusen. Bei Flip Chips ist der Platzbedarf gleich der Größe des eigentlichen Silizium-Chips zuzüglich einer kleinen Zugabe für den Underfill. Die Höhe ist gleich der Chipdicke plus dem Stand-off des Chips durch die Kontakte (im Bereich von einigen 10 µm). Beim COB entfällt ebenfalls das umliegende SMD-Gehäuse. Hier wird mehr Platz als beim Flip Chip benötigt, da Bondpads auf dem SiP-Interposer und ggf. Freiraum für den Verguss der Chips nötig sind.

Auch die Höhe eines COB-Aufbaus ist etwas größer als beim Flip Chip. Hier muss noch der Drahtloop und der Verguss über dem Chip mitkalkuliert werden. Dieser Größenvorteil kann bei der Realisierung eines SiP von entscheidendem Vorteil sein. Um den Testaufwand klein zu halten und eine hohe Ausbeute bei der SiP-Fertigung zu erzielen, ist dafür zu sorgen, dass „Known Good Dice“ (KGD) verwendet werden.

Nicht zu unterschätzen ist die Beschaffungssituation für die verwendeten Bauteile. Die Integration von passiven Komponenten – Widerständen, Kondensatoren oder Induktivitäten, aber auch aktiven Bauelementen in Form von gedünnten Chips (Embedded Components) im Trägersubstrat ist möglich und bringt weitere Miniaturisierungsmöglichkeiten.

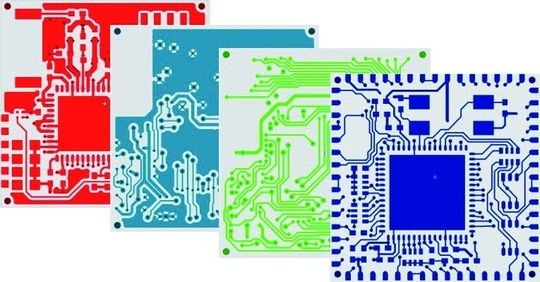

Um alle Anforderungen und Randbedingungen an ein SiP abzudecken, ist Spezialwissen aus unterschiedlichen Bereichen erforderlich. Bei der Layouterstellung müssen häufig Leiterplatten bzw. Interposer in High-Density-Interconnect-Technology (HDI) mit kleinsten Strukturen, vergrabenen und Blind-Vias designed werden (Bild 3). Design-Regeln für Flip Chip und Chip-on-Board sind zu berücksichtigen. Kenntnis über analoges, digitales und RF-Schaltungsdesign ist nötig.

Thermische, mechanische und optische Problemstellungen sind ebenso zu berücksichtigen wie die Medienbeständigkeit und die Zuführung bei Sensoren. Testkonzepte sind zu erarbeiten und neben einer exakten Systemmodellierung und Simulation ist ein fundiertes Wissen über die einzusetzenden Aufbau- und Verbindungstechnologien (AVT) entscheidend für den Erfolg. Dies erfordert schon zu einem frühen Zeitpunkt das Einbeziehen aller Beteiligten – Entwickler, Designer, Hersteller und Lieferanten.

SiP-Aufbau- und Verbindungstechnik

Das Design eines SiP beginnt mit der Umsetzung einer erprobten Schaltung, die auf einer konventionellen Baugruppe bzw. Leiterplatte realisiert ist. Im nächsten Schritt erfolgt die Aufteilung in Funktionsblöcke oder Subsysteme, die in sich geschlossene Funktionseinheiten bilden.

Danach müssen die Bauteile ausgewählt werden. Insbesondere ist die Gehäuseform zu klären bzw. die Festlegung auf Bare-Die-Prozesse durchzuführen. Gleichzeitig muss die Verfügbarkeit der Komponenten sichergestellt werden. Besonders bei kleinen Stückzahlen ist man häufig auf das Sortiment der einschlägigen Distributoren angewiesen und nicht jede, im Datenblatt eines Bauteils spezifizierte Gehäuseform ist kurzfristig und in kleinen Stückzahlen verfügbar.

Die Funktionsblöcke werden einzelnen Bereichen auf dem SiP und einzelnen Ebenen bei einem 2,5D-SiP zugeordnet. Hier muss auch eine Entscheidung getroffen werden, ob das SiP einseitig oder beidseitig bestückt wird bzw. wie viele Ebenen für ein vertikal integriertes 2,5D-SiP benötigt werden.

Verschiedene Arten der Kontaktierung an die Außenwelt

Besonders bei beidseitig oder vertikal integrierten SiP ist die Überlegung, wie das SiP später an die Außenwelt z.B. das System-Board kontaktiert wird, wichtig. Hier bieten sich unterschiedliche Lösungsansätze. Die Kontaktierung kann auf verschiedene Arten erfolgen:

- Über Standard-BGA-Balls. Hier ist insbesondere bei beidseitig bestückten SiPs der Stand-off der BGA-Balls zu berücksichtigen und es können nur solche Bauelemente auf der BGA-Seite montiert werden, die eine geringere Höhe besitzen als die BGA-Balls im montierten Zustand auf dem System-Board.

- Über Lötflächen (Leadless). Diese Kontaktierungsart ist ähnlich, wie bei den inzwischen weit verbreiteten QFN- oder MLF-Bauteilen. Hier scheidet eine doppelseitige Bestückung aus. Bei 2,5D-SiPs kann zusätzlich ein Rahmenelement eingesetzt und somit beidseitig bestückt werden. Das Ergebnis ist ein kompakter und mechanisch stabiler Aufbau.

- Über außen liegende Lötkontakte, so genannte LCC-Packages (Leadless Chip Carrier). Dazu verfügt das SiP, wie in Bild 4 gezeigt, über metallisierte halbkreisförmige und über die gesamte Interposer-Dicke laufende Kontaktflächen. Bei diesem SMT-kompatiblen Prozess wird das SiP auf dem System-Board in ein Lotpastendepot gesetzt und per Reflow-Löten kontaktiert.

- Über Miniatur-Steckverbinder lassen sich je nach Größe des SiP durchaus ähnlich viele Kontakte wie bei den zuvor beschriebenen Möglichkeiten realisieren. Nachteile bei Lösungen mit Steckverbindern, sind die hohe Bauhöhe für Steckverbinder und Gegenstück, sowie ein meist relativ großer Platzbedarf. Der relativ hohe Preis, besonders bei miniaturisierten Steckverbindern, ist ebenfalls nicht zu vernachlässigen. Der Vorteil gegenüber den anderen Lösungen besteht in der Lösbarkeit der Verbindung.

- Für autonom oder autark arbeitende SiPs sind oft keine zusätzlichen Kontaktierungsmöglichkeiten nötig, insbesondere wenn die Informationsübertragung über eine Wireless-Schnittstelle erfolgt.

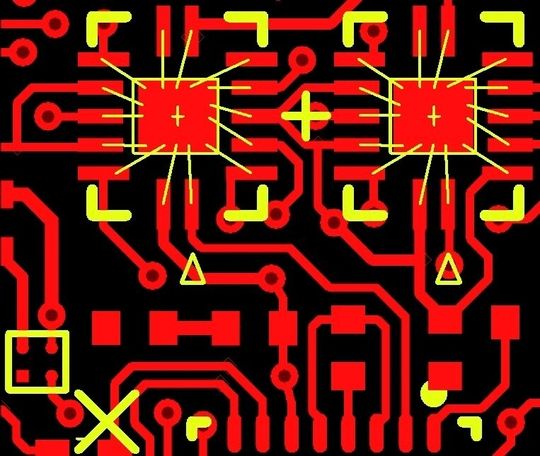

Als Träger für SiPs dienen Interposer bzw. Leiterplatten auf Laminatbasis. Binder Elektronik bevorzugt Standard-FR4 bzw. FR4-High-Tg-Materialien (Tg > 140°C). Als Endoberfläche hat sich chem. Ni/Au bewährt. Diese ist mehrfach lötbar, gegen Umwelteinflüsse resistent und bondbar. Beim Design von Flip Chip oder COB sind umfangreiche Toolkits der verschiedenen CAD-Softwarehersteller verfügbar, die eine weit gehende Automatisierung ermöglichen und damit dem Designer die Arbeit erheblich erleichtern. Trotzdem muss dieser die Entscheidung, was technisch machbar und sinnvoll ist, selbst treffen und die besonderen Randbedingungen für Bare-Die-Prozesse (Bild 5) kennen.

Nach der Layouterstellung und Herstellung des SiP-Trägers erfolgt die Fertigung. Hier werden SMT-kompatible Prozesse bevorzugt, da diese gut automatisierbar sind, somit eine große Ausbeute ermöglichen und geringe Herstellkosten anfallen. Unterschieden werden Single-Pass-Aufbauten, die einen Reflow-Prozess erfordern und Multi-Pass-Prozesse, die mehrere Reflow-Durchläufe benötigen, wie sie bei beidseitig bestückten SiPs und 2,5D-SiPs nötig sind. Hier ist beim Design, der Fertigungsplanung und der Materialauswahl zu berücksichtigen, dass das Material mehrfach gestresst wird. Im ersten Arbeitsschritt wird der SiP-Interposer mit Lotpaste bedruckt und mit den SMD-Komponenten bestückt. Nacktchips können als Flip Chips mit Lötkontakten oder in Klebetechnik sowie in Wire-Bond-Technologie (COB) eingesetzt werden. Die anschließenden Arbeitsschritte komplettieren das SiP, wie das Aufbringen von BGA-Balls auf der Unterseite, Etikettierung oder Beschriften. Das Trennen der SiP-Interposer aus dem Fertigungsnutzen erfolgt meist durch Sägen. Es folgt ein Reinigungsschritt, die Endkontrolle bzw. der Endtest, die Verpackung und schließlich die Auslieferung.

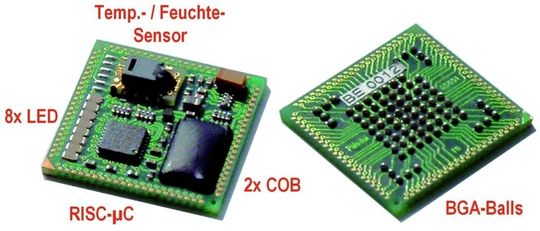

Planare System-in-Packages

Planare SiPs werden bei Binder Elektronik hauptsächlich mit QFN- oder BGA-Gehäuseanschlüssen realisiert. Die Interposer können bis ca. 50 mm x 50 mm groß sein. Um wirtschaftlicher fertigen zu können, sind mehrere Interposer in einem Nutzen angeordnet. Bild 6 zeigt ein Datenlogger-Modul mit den wesentlichen Komponenten: Temperatur-Feuchtesensor, acht LEDs zur Visualisierung und einem Mikrocontroller mit Flash, SRAM und EEPROM zur Datenspeicherung inklusive Peripheriebausteine. Zwei ICs wurden aus Platzgründen als COB ausgeführt, um die Elektronik auf dem 20 mm x 20 mm großen Interposer unterbringen zu können. Die Kontaktierung zur Umgebung erfolgt mittels BGA-Balls auf einem System-Board.

SiP mit Stacked Dice

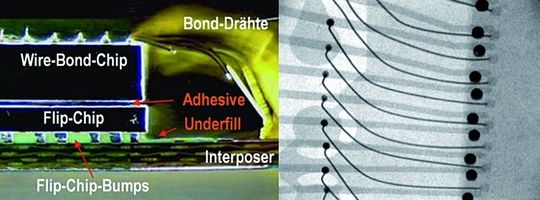

Geht man zur nächsten Integrationsstufe und montiert zusätzlich zwei oder mehrere Chips übereinander, lassen sich mittels Flip-Chip- und Draht-Bond-Technologie sehr kompakte Aufbauten realisieren, so genannte Stacked-Die-Packages. Dabei gibt es eine Vielzahl von Realisierungsmöglichkeiten. Eine Variante eines Stacked-Die-Package ist das Flip-Chip + Wire-Bond-Package (FC+WB) wie in Bild 7 dargestellt. Dieses SiP wird realisiert, indem ein Flip Chip mit Lotkugeln auf den Interposer montiert wird. Dieser wird verlötet und underfillt.

Anschließend wird ein Bare Die auf den Flip Chip geklebt. Dieses Chip-in-Package (CiP) wird dann durch Wire-Bonden mit dem Interposer kontaktiert (Bild 8). Danach wird der Aufbau mit einem Dam & Fill-Material verkapselt.

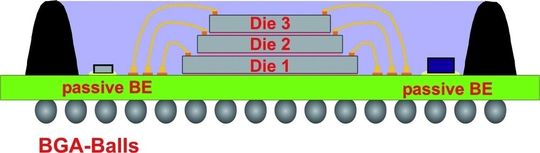

Eine Möglichkeit zur Kontaktierung von mehreren Wire-Bond-Chips zeigt Bild 9. Unterschiedlich große Bare Dice sind so gestapelt, dass ein pyramidenförmiger Aufbau entsteht, der unterste Chip ist der größte. Der Chip darüber ist wenigstens um die Größe der Bondpads des ersten Chips kleiner und so weiter. Somit sind die Bondpads immer frei zugänglich und können nach der Montage aller Chips von unten nach oben gebondet werden.

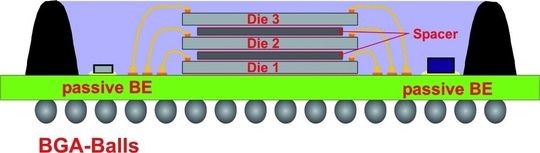

Sollen gleich große Chips in ein Package integriert (Bild 10) werden, ist dies mit-hilfe von Abstandshaltern (Spacern) möglich, die wenigstens um die Bond-Pads der Chips kleiner sind und zwischen den einzelnen Chips montiert werden. Die Höhe der Spacer ist dabei mindestens so groß, dass die Bondverbindungen des unten liegenden Chips überragt werden. Bei dieser Aufbauvariante muss der unten liegende Chip gebondet werden, bevor der darüber liegende auf den Spacer montiert wird, da sonst die Bond-Pads nicht mehr frei zugänglich sind.

Vertikal integrierte System-in-Packages (2,5D-SiP)

Die vertikale Montage von mehreren 2D- oder Stacked-SiP führt zu 2,5D-SIPs. Diese vertikale Integration elektronischer Komponenten in einem 2,5D-SiP ist eine der zukunftsträchtigsten Entwicklungen in der modernen Mikroelektronik. Die Entwicklung von 2,5D-SiP stellt besondere Anforderungen an die Designer. Jede Ebene muss als 2D-SiP entworfen werden. Die Aufteilung der Komponenten auf die Ebenen muss zu einem frühen Zeitpunkt festgelegt werden.

Die einzelnen Ebenen werden wie ein 2D-SiP gefertigt und im anschließenden Montageschritt zu einem quasi drei-dimensionalen Stack zusammengefügt. Eine Reparatur oder der Austausch einzelner Ebenen ist aber nur eingeschränkt möglich. Daher muss jede Ebene vor der Montage zum Gesamtsystem geprüft werden, um eine entsprechend hohe Ausbeute zu erzielen. Um die Ebenen übereinander kontaktieren zu können, müssen die elektrischen Signale, die auf anderen Ebenen benötigt werden, mittels einer Busarchitektur verfügbar sein.

Dazu wurden Stapelkonzepte mit peripher angeordneten Rahmenkontakten entwickelt. Um die elektrischen Signale zur nächsten Ebene weiterzuleiten und gleichzeitig die Bauteilehöhen zu überbrücken, werden Rahmenelemente (ebenfalls auf Leiterplattenbasis) eingesetzt. Auf diese Weise lassen sich bis zu fünf Ebenen übereinander montieren.

Eine weitere Kontaktierungsmöglichkeit für 2,5D-SiP stellt die Ausführung als Lead-Less-PCB-Frame dar. Hier werden die Signalpfade über außen liegende, angeschnittene und metallisierte Kontaktierungen realisiert (Bild 11). Vorteile sind weniger Fertigungs- und Lötschritte, ein relativ kompaktes, unempfindliches Gehäuse und eine gute Erreichbarkeit der Rahmensignale für Testzwecke. Nachteile sind die geringere Anzahl an Rahmenkontakten als bei anderen Rahmen-Varianten, eine aufwändigere manuelle Verlötung der Außenkontakte sowie eine erschwerte Wärmeabfuhr und Demontage. Besonders bei Prototypen und kleinen Stückzahlen ergibt sich eine Kosteneinsparung zur ersten Variante.

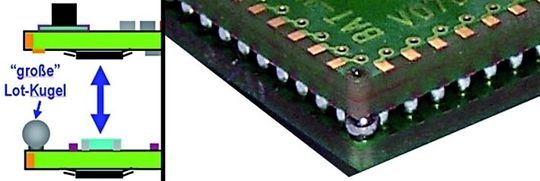

Als dritte Variante wurde die Nur-Solder-Ball-Variante (Bild 12) erprobt und eingeführt. Dabei wird der Rahmen komplett durch „große“ Lotkugeln ersetzt. Zur Verwendung kommen dabei Standard-BGA-Lotkugeln, die in einem speziellen Fertigungsschritt eine „große“ Lotkugel für den Rahmenbereich ausformen.

Die Vorteile sind eine kostengünstigere Lösung, da auf das Rahmenelement verzichtet wird. Durch die „offene“ Ausführung wird die Entwärmung verbessert. Nachteile sind eine geringere erreichbare Höhe von max. 1,5 mm (ausreichend für viele Standard-SMD-Packages und Chip-Aufbauten) sowie eine kleinere Anzahl an Rahmensignalen (64 bei 20 mm x 20 mm Kantenlänge), was aber für die meisten Anwendungen trotzdem ausreicht.

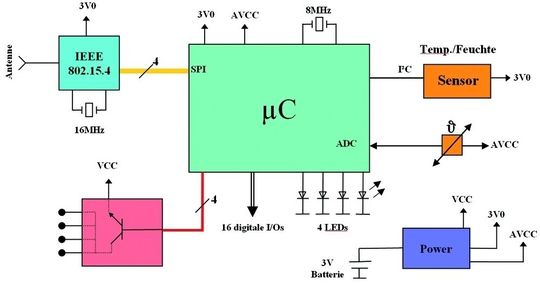

Bild 13 zeigt das Blockbild eines RF-Funkmodul im 2,5D-SiP-Package. Über eine austauschbare 3-V-Lithium-Batterie wird das Modul mit Energie versorgt und kann somit autonom betrieben werden. Die erfassten Daten (hier Temperatur und Luftfeuchtigkeit) werden über das lizenzfreie 2,4-GHz-Band übertragen. Als Übertragungsprotokoll wird IEEE802.15.4/ZigBee verwendet.

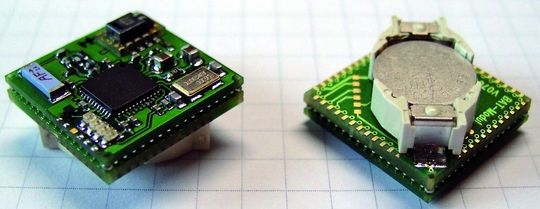

Das 2,5D-SiP besteht aus einer Elektronikebene mit Funkteil, Sensoren und Aktoren (LEDs und Funkantenne) auf der Oberseite (Bild 14 links). Im Inneren des 2,5D-SiP befindet sich ein RISC-Mikrocontroller mit Peripheriebeschaltung. Als Programmspeicher stehen 128 KByte FLASH und je 4 KByte RAM und EEPROM zur Messdatenspeicherung zur Verfügung, sodass das Modul Daten über lange Zeiträume erfassen kann, ohne diese an eine Basisstation übertragen zu müssen.

Die Unterseite des Moduls wird durch die Batterie-Ebene (Bild 14 rechts) gebildet. Diese Ebene besteht aus dem Batteriehalter und Anschlusspads zum Kontaktieren von 16 digital I/Os, vier Open-Collector-Ausgängen sowie vier analogen Eingängen.

Schon kleinere Stückzahlen rechnen sich

Durch SiPs lassen sich miniaturisierte Lösungen für vielfältige Anwendungen realisieren. Auch im kleineren Stückzahlbereich ist es interessant SiPs zu entwickeln und deren Potenzial zum eigenen Wettbewerbsvorteil zu nutzen. Binder Elektronik in Sinsheim entwickelt und fertigt kundenspezifische SiP auf Basis von Leiterplatten in einfacher oder hochkomplexer Technologie vom Prototypen bis zu mittleren Stückzahlen in verschiedenen Ausführungen für die Mess-, Regel-, Daten- und Medizintechnik. Dabei kommen Standard-SMD-Prozesse sowie moderne Hightech-Aufbau- und Verbindungstechnologien zum Einsatz, wie sie in SMD-Fertigungen und beim Chip-Packaging zu finden sind.

*Wolfgang Binder ist Geschäftsführer, Matthias Geiger ist Entwicklungsleiter beim EMS-Anbieter Binder Elektronik GmbH in Sinsheim.

(ID:230039)

:quality(80)/p7i.vogel.de/wcms/e9/ce/e9ce137e87eccac328ec5504c586c477/0129711019v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/68/46/684697b6eb687384e0d8c6803450401a/0130056395v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/0f/c0/0fc0d93c99a5d9066e58c39f41fb1b10/0130046764v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1d/d8/1dd8627e2323721d4ee5436f9401911e/0130147601v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/8e/d4/8ed4a2aa0bf362584aa1284f0adb2fdf/0130156040v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/65/f4/65f404dc6d19d4f1628ad7e49f6a22cf/0130136276v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fb/d3/fbd33264fcdf128866667be0a0a6b657/0130137877v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a5/5e/a55ec741a9c17cb890b2cb5bcb919477/0130162776v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/8d/fa8dedee195f29c33c89d86311c258ee/0130104146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cc/13/cc1378375499a26b5ddbb309d2155acb/0130085649v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/24/58/2458f1cae3100e375fbb8124f02c54af/0130111244v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/fc/fafc300481de3fd4d7f34400327d0d01/0130127049v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d2/cd/d2cd33084ab732ff8a600bc55ade1f47/0130096831v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/10/45/1045969e69a1db4aaa73d0f74f55cc02/0129962687v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c7/f6/c7f61d0437c7f8fca3c6ff947ba2ad62/0129322490v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/66/0c/660c31afa35398bac9be42f2be73fdc4/0129073529v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/af/35af7dd326d198475d06fbb69aa600b5/0130175971v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/2e/c02e7bf72bfc434888c37100e2511681/0130127767v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/95/a1/95a197490145b7afcfd4dc176a1b5ef9/0130096114v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bf/82/bf82f81061b759c454e15ec4c2e7560b/0130110139v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/74/96/74964a7715c738a9e8b17681445ceed3/0130103633v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/0d/18/0d183ecb569b03285578762658d2def6/0130061201v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/72/19/7219e53d462877119eaf0bd98783a46d/0129953146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6a/93/6a93991941467231d8798c8577882dfd/0130071573v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d3/76/d3760874d137b2f4bae5954b46dd5900/0130101582v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/42/de/42de87134adee379a83e5d633ba48c95/0130176499v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/90/0c/900ca1b73852ed45bd7e42a6119192dd/0130174841v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/5e/ed/5eed37b21283f8f364a37d025d53fa48/0130167146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bb/2a/bb2ac8404ae7b3f08a5c01d1ca0615a7/0130182922v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ef/9d/ef9dc7f8402f3f4ff42268e573921bc4/0130129635v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/66/1f/661fa8e004810/heitec-logo-2024-1200px-ae.png)

:fill(fff,0)/p7i.vogel.de/companies/64/21/64219ce08bf52/logo.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/69/7c/697cbb83628bc/logo-16-9.png)

:quality(80)/p7i.vogel.de/wcms/2e/b7/2eb712f6351a2abb0a606c1956cabc89/0124512500v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/df/41/df41bfae5223b6988b3291e519d36f47/0124990347v2.jpeg)