HDI-Leiterplatten - Teil 11 Worin sich der Design Rule Check beim Entwickler und Leiterplattenhersteller unterscheiden

In diesem Kapitel der HDI-Serie erläutert Karim Richlowski, Leiter CAM bei CONTAG, die Möglichkeiten, die Designregeln und deren Auswirkungen auf Qualität und Ausbeute bei der Leiterplattenfertigung zu überprüfen. Wichtig ist dabei, zwischen dem Design Rule Check (DRC) auf dem CAD-System des Entwicklers und dem finalen DRC auf dem CAM-System des Leiterplattenfertigers zu unterscheiden.

Anbieter zum Thema

Wie funktioniert ein Design Rule Check?

Heutzutage bieten die meisten CAD-Systeme Möglichkeiten, die Einhaltung vorgegebener Design-Regeln in Echtzeit oder in einem separaten Postprocessing-Lauf zu überprüfen. Dabei können zumindest einfachere Verstöße gegen die Designregeln festgestellt werden wie z.B. überlappende Potentiale, Verletzungen von Mindestabständen, Nichteinhaltungen von Winkeln (oft nur 45 und 90° erlaubt) sowie Objekte, die nicht auf dem vorgegebenen Raster liegen. Fehler werden als Fehlerliste und/oder grafisch im Layout angezeigt.

Bei einfachen Systemen sind dazu die Parameter global festgelegt. Hochwertigere (und damit kostenträchtigere) CAD- oder CAM-Systeme haben wesentlich umfangreichere Prüfmöglichkeiten und erlauben es, den DRC partiell und nach spezifischen Klassifizierungen durchzuführen.

Die Prüfkriterien (einzelne Prüfparameter) können dabei nach globalen (für die ganze Platine), layerspezifischen (für einzelne Layoutebenen), regionalen (auf bestimmte Bereiche innerhalb eines Layers oder der Platine z.B. ein BGA-Anschlussfeld), klassenspezifischen (für eine bestimmte Signalklasse, z.B. Bus-Stromversorgungs- oder allgemeine Signalleitungen) oder netzspezifischen (für ein ganz bestimmtes Signalnetz bzw. Potential) Regeln festgelegt werden. Dies ist speziell bei HDI-Leiterplatten mit ihren vielfältigen, teilweise höchst unterschiedlichen Anforderungen sinnvoll. Oft bleibt es jedoch beim guten Willen und beim lagenspezifischen DRC, weil eben das eigene CAD-System nicht mehr kann.

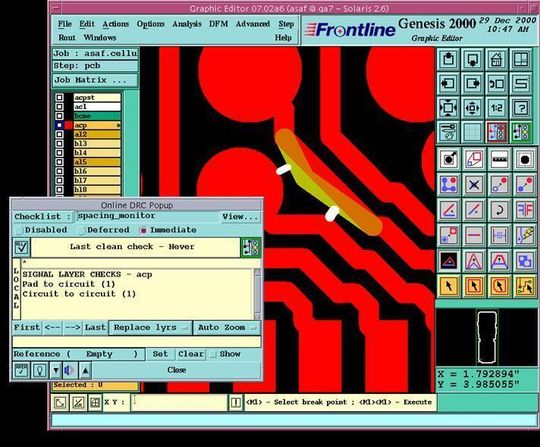

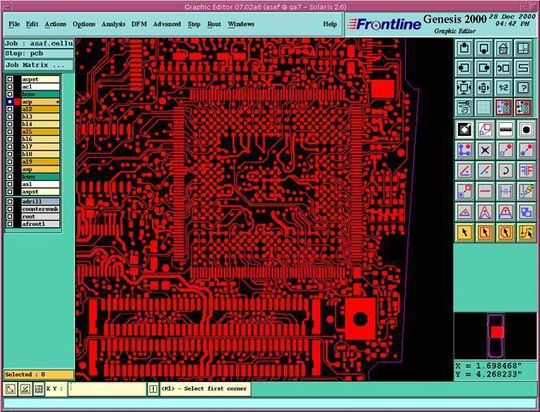

Damit lassen sich zumindest die unterschiedlichen Grundvoraussetzungen der Stromversorgungs- und Signallagen berücksichtigen, bei unterschiedlichen Anforderungen in den Signallagen müssen meist Kompromisse gemacht und spezielle Regeln mühsam und fehlerträchtig von Hand geprüft werden. Hier kann der Leiterplattenhersteller helfen, wenn er über ein leistungsfähiges CAM-System verfügt, das über all die oben erwähnten Klassifizierungsmöglichkeiten verfügt. So kommt zum Beispiel bei der Contag GmbH ein solches CAM-System vom Typ Genesis 2000 von Orbotech (Bild 2) zum Einsatz.

DRC beim Leiterplattendesigner

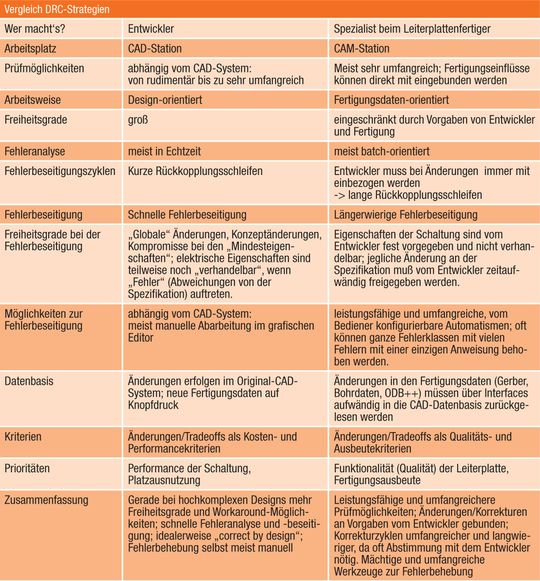

Durch die doppelte Prüfung mit unterschiedlichen Systemen wird das Risiko der Nichterkennung von Regelverletzungen durch Fehler in der Prüfsoftware weitestgehend ausgeschlossen. Was unterscheidet nun den DRC des Anwenders auf seinem System von dem DRC des Fertigers auf seiner CAMstation? Vielfach überschneidet sich die Funktionalität beider Prüfungen, was der oben erwähnten Fehlersicherheit zugute kommt. Dies trifft insbesondere für teuere Hochleistungs-CAD-Systeme zu, die vielfach sogar über eigene CAM-Module verfügen. Die wesentlichen Unterschiede zwischen dem DRC des Entwicklers auf dem CAD-System (meist online) und dem DRC des CAM-Spezialisten beim Leiterplattenhersteller liegen vor allem in der unterschiedlichen Prüfstrategie bzw. Anwendung des DRC, wie die Tabelle zeigt.

Der Ehrgeiz des Entwicklers bzw. Layouters liegt darin, eine schnelle und kostengünstige Lösung für sein Projekt zu finden. Stößt er an Grenzen, kann er selbst entscheiden, wo und wie er seine Schwerpunkte und Kompromisse (Trade-Offs) setzt. Notfalls kann er sein ganzes Design „umwerfen“ oder die Auswirkungen von Regeländerungen im Grenzbereich mit Simulation oder auf Basis von konkreten Erfahrungswerten abschätzen.

Von den Tücken der Fertigung und den Auswirkungen von Grenzannäherungen oder Verletzungen der Designregeln auf Qualität und Ausbeute der Leiterplatte hat er oft wenig Ahnung, da dies nicht in seinen unmittelbaren Aufgabenbereich fällt. Er behebt die Probleme die im beim Arbeiten sein DRC meist online liefert mehr oder weniger sofort. Er liefert ein nach seinen Gesichtspunkten und soweit mit den Möglichkeiten seines CAD-Systems feststellbar fehlerfreies Design ab und setzt es abschließend noch in fertigungstaugliche Formate wie Gerber/Excellon oder ODB++ um.

DRC beim Leiterplattenhersteller

Völlig anders ist die Situation des CAM-Spezialisten beim Leiterplattenhersteller. Er wird bei seinem wesentlich umfangreicheren, typischerweise im Hintergrund (Batch) ablaufenden DRC nach Fertigungsgesichtspunkten meist viele neue Probleme feststellen, obwohl er ja aus Sicht des Entwicklers ein (vermeintlich!) fehlerfreies Projekt bekommen hat. Er muß nun die vielen Meldungen des DRC mit Hilfe der in der CAM-Station verfügbaren Werkzeuge erst einmal priorisieren.

Dabei ist zu unterscheiden zwischen: Einerseits „harten“ Fehlern die zwingend behoben werden müssen, um die geforderte Mindestqualität und Funktionalität der Leiterplatte zu erreichen. Dies sind typischerweise die selben Themen wie beim DRC auf dem CAD-System des Entwicklers: Unterschreitungen von Mindestabständen, Kurzschlüsse, Nichteinhalten von Mindestbreiten, unerlaubte Einschnürungen, falsche PADs, nicht zum Signaltyp passende Leiterbahnen, etc. Dies alles, erweitert um die Aus- und Wechselwirkungen der jeweiligen Fertigungstechnologie des Herstellers.

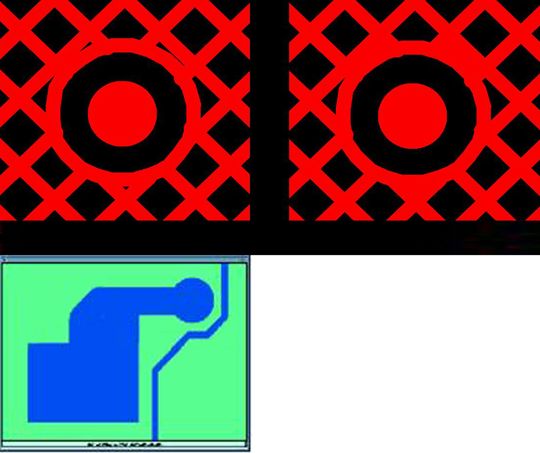

Andererseits (meist geometrischen) Problemzonen, welche die Ausbeute (Yield) verschlechtern könnten. In diese Klasse gehören z.B. feine Inseln in Kupferflächen (Pinholes, siehe Bild oben), kleine Nichtkupfer-Halbinseln, die zu Lötstopplack-Ablösungen führen könnten (Slivers, siehe Bild unten).

Danach wird er anhand der Möglichkeiten, die ihm seine CAM-Station bietet einen möglichst effizienten Weg einschlagen, diese Probleme zu beheben. Dies wird durch die eingangs beschriebenen Klassifizierungen der Problemzonen (global, layerspezifisch, regional, klassenspezifisch oder netzspezifisch stark erleichtert, da so für die notwendigen Änderungen gezielt auf die betroffenen Elemente bzw. Leitungssegmente zugegriffen werden kann.

Dies ist unkompliziert, wenn alle Modifikationen innerhalb des verfügbaren Platzes bzw. innerhalb der gegebenen Spezifikation durchgeführt werden können. Ist dies nicht der Fall, so wird es schnell zumindest zeitaufwändig, da die dann durchzuführende Änderungen mit dem Entwickler besprochen und durch ihn freigegeben werden müssen. Nicht zu unterschätzen ist auch der Aufwand der Kommunikation und der Rückführung der notwendigen Änderungen in die CAD-Datenbank des Entwicklers.

Gibt es entwicklungsseitig eine bidirektionelle Schnittstelle zu dem von CONTAG bevorzugten Datenaustauschformat ODB++, so lässt sich der Aufwand für den Datenaustausch (Back Annotation) mit dem CAD-System in vernünftigen Grenzen halten.

Sinnvoll ist es, mit dem Abarbeiten der DRC-Meldungen auch gleich weitere, die Ausbeute und Betriebssicherheit der Leiterplatte erhöhende Verbesserungen (meist Geometrieänderungen) vorzunehmen. Worum es bei diesen Design-for-Manufacturing Optimierungen geht und wie sie in der Praxis umgesetzt werden, erläutert Kapitel 12.

Hier finden Sie alle Teile der Beitragsreihe HDI-Leiterplatten.

(ID:241394)

:quality(80)/p7i.vogel.de/wcms/46/7c/467c0afffbfd10c3553c2888a4a6289f/0130479810v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/12/3d/123d9eb2c2e4ce13296371a2ad3718a4/0130412664v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d8/78/d878b7bfc23826e6ddfce42443836d28/0130384280v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/13/20/13208d1c2797edd67d9ff216b403726b/0130471595v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/38/cb/38cbe19e814dd30b94780bc3946547ab/0130446533v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a3/3e/a33e6d8a927d539ec6c3a0537f48f0f1/0130440028v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6b/61/6b61373f1c3f06f7f9343e6b0f0e9cc8/0130225062v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/15/93/1593dd152e6d58c5fc5da0d331777c54/0130357398v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/88/c28805ea7b2261235475146a5b0c61f8/0130313028v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/8d/fa8dedee195f29c33c89d86311c258ee/0130104146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cc/13/cc1378375499a26b5ddbb309d2155acb/0130085649v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6d/91/6d91abfa1b16ffcf470c7147facd7aa8/0130387695v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/85/b0/85b0b32128f6d1968e975043f1e0b67b/0130342166v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/1a/53/1a539631c940d184689460600bd2b395/0130410666v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/10/45/1045969e69a1db4aaa73d0f74f55cc02/0129962687v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c7/f6/c7f61d0437c7f8fca3c6ff947ba2ad62/0129322490v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/e4/bae4e54395e5a53088060531ef99b814/0130359274v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/af/35af7dd326d198475d06fbb69aa600b5/0130175971v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/2e/c02e7bf72bfc434888c37100e2511681/0130127767v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/7c/04/7c04916c305164fb10bc6cb05b51d934/0130431065v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/64/e5/64e5e333492f182ab7df5ab4c2b54c1e/0130463252v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/0a/95/0a95db4508128c4e11d5d268bf2c0a77/0130440053v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b3/65/b365dd5433c8b6d36c56c92b72f5b368/0130401081v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/85/c0/85c0cdd8fd326013aed52ca96777c998/0130426877v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f0/78/f07826d6c4e995980f1ada3377416aac/0130403626v4.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/c8/b6c8f7732da417bda3d298412f4c0ed8/0130453104v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/47/ce/47ce64bad7990f276f68cbb24505f6dd/0130472850v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/15/56/15564dea31861c376a385658c3b961a3/0130465243v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/98/ad/98ad595a6372aae8dbeac71681d23f41/0130450258v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bf/2a/bf2aad428ab1a80e6738fdbdc2efeb7e/0130453420v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/5f/88/5f8847c90d2e4/50-mm.jpg)

:quality(80)/p7i.vogel.de/wcms/2c/40/2c40cea54250c0cc97dbc8d8448798a5/0129385029v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/af/78/af78d1a793e1dc1cb774ecacafa12365/0126572790v2.jpeg)