HDI-Leiterplatten - Teil 9 Standardtechnik und HDI-/SBU-Technik im Kostenvergleich

Der Marktanteil von in HDI/SBU-Technologie gefertigten Leiterplatten liegt in Deutschland immer noch deutlich unter 15%. Vielfach werden vermeintlich höhere Kosten als Argument gegen die Einführung von HDI aufgeführt. Darum vergleichen wir konkret zwei Entwurfsvarianten eines Redesigns in klassischer Standardtechnik mit einer kostenoptimierten HDI-/SBU-Ausführung.

Anbieter zum Thema

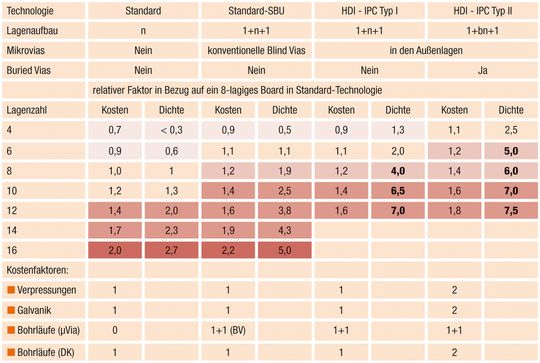

Grundsätzlich sind bei optimierten Designs vergleichbarer Projekte die Materialkosten bei HDI-Leiterplatten zum Teil deutlich geringer. Dies liegt an der bei HDI deutlich höheren Packungsdichte, die generell mit wesentlich weniger Fläche und damit auch Materialressourcen auskommt. Dies ist jedoch ins Verhältnis zu der meist deutlich aufwändigeren Fertigung zu setzen. Die Kostenfaktoren für die einzelnen Realisierungsvarianten sind nach den Erfahrungen der CONTAG GmbH in beiden Technologievarianten zumindest ähnlich, oft sogar identisch.

Diese fertigungsabhängigen Kostenfaktoren von HDI-Leiterplatten sind:

- Anzahl der nötigen Verpressungen,

- Anzahl und Komplexität der jeweils nötigen Galvanik-Durchgänge (Erzeugung von leitfähigen Durchkontaktierungen),

- Anzahl und Art der Bohrläufe (für die unterschiedlichen Bohrgrößen),

- Anzahl und Art der jeweiligen Bohrungen (Mechanisch/Laser),

- kleinste Bohrgröße bei mechanisch gebohrten Löchern,

- geringste Leiterbahnbreiten/-abstände der Mikrovia-Lagen,

- Aspect Ratio,

- Kern-, Laminat- und endgültige Leiterplattendicken,

- Flächenausnutzung auf dem Fertigungsnutzen,

- spezielle Anforderungen an den Aufbau wie z.B. spezifische Impedanzen oder Plugging,

- Sondermaterialien,

- sonstige Sonderanforderungen; speziell im Blick auf Genauigkeitsanforderungen außerhalb der eingefahrenen Standards und

- spezielle Oberflächen.

Was in der Praxis möglich ist

Das mögliche Lösungsfenster gibt in der Praxis die Spezifikation der Leiterplatte vor. Oft gibt es harte Kriterien wie eine maximale Platinengröße, eine Impedanzvorgabe oder auch ein spezifisches Bauteileraster, die nicht verhandelbar sind und gewisse Mindestwerte festsetzen.

Die verbleibenden weichen Parameter lassen sich dann nach Kosten- und Fertigungsgesichtspunkten gegeneinander abwägen. Dabei sind jedoch die Gesamtprojektkosten des Produktes über die Lebensdauer in Betracht zu ziehen; insbesondere auch das Verhältnis zwischen Einmalkosten und sich wiederholenden Kosten mit Blick auf die zu erwartenden produzierten Stückzahlen.

Normalerweise gilt es, vor allem die Fläche, die Anzahl der Durchkontaktierungen, die Lagenanzahl und die Anzahl der Verpressvorgänge zu reduzieren.

Die HDI/SBU-Technologie ermöglicht aufgrund ihrer feineren Strukturen und der viel Platz sparenden Mikrovias eine deutlich direktere und effizientere Leitungsführung, die in einer erheblichen Flächenreduzierung und in wesentlich weniger Durchkontaktierungen resultiert. Aber hebt dies auch den höheren Fertigungsaufwand auf (und die Anfangskosten für die Umstellung?

Eine grobe Abschätzung bietet die aktualisierte Tabelle 1, die wir in ähnlicher Form schon aus der zweiten Folge dieser Serie kennen. Bezugspunkt ist dabei ein achtlagiger Standard-Multilayer mit einer Dichte von etwa 500 Verbindungen bzw. Pins pro Quadratdezimeter. Die exakten Parameter ergeben sich für die jeweilige Schaltung immer ganz spezifisch und können je nach Einzelfall noch ganz erheblich abweichen

Ein konkretes Beispiel (1-2-1)

Grundannahme ist ein bestehendes Design mittlerer Komplexität, das keine besonderen oder flächendeckenden Anforderungen bezüglich hoher Frequenzen oder Signal- bzw. Powerintegrity stellt und einen festen Formfaktor hat (vorgegebene Platinengröße wie z.B. Computer-Board).

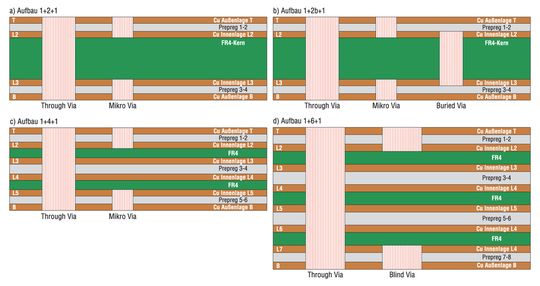

Da hier keine durchgehenden Power- und Ground-Ebenen benötigt werden, bietet es sich an, ein komplettes Redesign als nur 4-lagige Platine zu machen (Bild 1).

1-2-1 steht dabei für eine Realisierung als 4-lagiger sequenzieller Aufbau (SBU) mit jeweils einer auflaminierten Mikrovia-Lage auf der Oberseite (TOP), einer Kernlage mit 2 Layern und einer auflaminierten Mikrovia-Lage auf der Unterseite (BOTTOM).

Rein kostenmäßig attraktive Alternativen dazu wären ein vierlagiges HDI/SBU-Board mit buried Vias im Kern (1+2b+1; b), ein 6-lagiges HDI/SBU-Board (1+4+1; Bild c) oder eine 8-lagige Platine mit Sacklöchern in konventioneller Technologie als SBU (sequenzieller Lagenaufbau; Bild d).

Durch das Ausnutzen der dann möglichen höheren maximalen Verbindungsdichte wäre hier eine Kosteneinsparung über eine deutlich kleinere Platinenfläche zu erzielen. In unserem Beispiel ist dies wegen des festen Formfaktors aber nicht möglich. Und selbst wenn: Bei einer neuen Variante als klassisches Board mit Sacklöchern würden trotz der Kostenersparnis im Vergleich zur ursprünglichen Lösung der höhere Entflechtungsaufwand und die fehlende Zukunftssicherheit (Verwendbarkeit von Bauteilen mit kleinem/hochdichtem Anschlussraster) dagegen sprechen. Wie wir sehen gilt es, auf viele Punkte zu achten und im Projekt entsprechend zu optimieren.

Was es noch zu beachten gilt

Ausschlaggebend sind immer die Gesamtkosten über die Lebensdauer (TCO). Diese schließen Kriterien wie die langfristige Verfügbarkeit von Bauelementen und der Fertigungstechnologie mit ein, aber auch die jeweiligen Entwicklungskosten im Bezug auf die geplante Stückzahl. Oft gibt es von den Chipsatzherstellern konkrete Referenzdesigns und Anwendungsempfehlungen (Application Notes) mit Entflechtungsbeispielen (Breakout Patterns). Diese beziehen sich meist nur auf ein oder zwei ganz bestimmte Technologien.

Im Mainstream-Prozessorbereich ist dies sehr oft aus Kostengründen der hier im Beispiel erwähnte 1-2-1 Lagenaufbau in HDI-Technik. Hier kann der Entwickler also durch Verwendung von bewährten Referenzdesigns viel Zeit und damit Geld sparen und typische Fehler vermeiden. Zudem kann man so zuverlässig Blöcke auf die Schaltung übernehmen (z.B. schnelle Speicheranbindung), für die der Entwickler vielleicht noch kein so tiefes Knowhow hat.

Manchmal kommen hierzu auch Sondertechnologien wie Plugging (siehe Teil 8) zum Einsatz wie im Beispiel des 1-2b-1 Lagenaufbau des gezeigten Schliffbildes eines aktuellen PC-Prozessorboardes (Bild 2). Dies mag auf den ersten Blick aufwändig und teuer erscheinen, unter dem Strich rechnet es sich aber, da das gesamte Redesign trotz hochpinniger BGAs statt vorher mit 10 klassischen Lagen jetzt mit nur 4 HDI-Lagen auskommt.

Wichtig für den Entwickler sind hier absolute Zuverlässigkeit und Qualität des Leiterplattenfertigers für die jeweilige Technologie sowie eine umfangreiche Planungsunterstützung bereits im Vorfeld der Entwicklung.

CONTAG bietet hierzu eine umfangreich Beratung an. So können die Vor- und Nachteile von verschiedenen Varianten gemeinsam mit dem Anwender diskutiert und die für das jeweilige Projekt optimale Technologie ausgesucht werden.

Weitere Details zur Kostenabschätzung zeigt Kapitel 10 der HDI-Leiterplatten-Serie.

Hier finden Sie alle Teile der Beitragsreihe HDI-Leiterplatten.

(ID:235432)

:quality(80)/p7i.vogel.de/wcms/e9/ce/e9ce137e87eccac328ec5504c586c477/0129711019v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/68/46/684697b6eb687384e0d8c6803450401a/0130056395v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/0f/c0/0fc0d93c99a5d9066e58c39f41fb1b10/0130046764v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1d/d8/1dd8627e2323721d4ee5436f9401911e/0130147601v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/8e/d4/8ed4a2aa0bf362584aa1284f0adb2fdf/0130156040v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/65/f4/65f404dc6d19d4f1628ad7e49f6a22cf/0130136276v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fb/d3/fbd33264fcdf128866667be0a0a6b657/0130137877v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a5/5e/a55ec741a9c17cb890b2cb5bcb919477/0130162776v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/8d/fa8dedee195f29c33c89d86311c258ee/0130104146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cc/13/cc1378375499a26b5ddbb309d2155acb/0130085649v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/24/58/2458f1cae3100e375fbb8124f02c54af/0130111244v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/fc/fafc300481de3fd4d7f34400327d0d01/0130127049v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d2/cd/d2cd33084ab732ff8a600bc55ade1f47/0130096831v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/10/45/1045969e69a1db4aaa73d0f74f55cc02/0129962687v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c7/f6/c7f61d0437c7f8fca3c6ff947ba2ad62/0129322490v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/66/0c/660c31afa35398bac9be42f2be73fdc4/0129073529v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/af/35af7dd326d198475d06fbb69aa600b5/0130175971v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/2e/c02e7bf72bfc434888c37100e2511681/0130127767v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/95/a1/95a197490145b7afcfd4dc176a1b5ef9/0130096114v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bf/82/bf82f81061b759c454e15ec4c2e7560b/0130110139v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/74/96/74964a7715c738a9e8b17681445ceed3/0130103633v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/0d/18/0d183ecb569b03285578762658d2def6/0130061201v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/72/19/7219e53d462877119eaf0bd98783a46d/0129953146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6a/93/6a93991941467231d8798c8577882dfd/0130071573v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d3/76/d3760874d137b2f4bae5954b46dd5900/0130101582v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/42/de/42de87134adee379a83e5d633ba48c95/0130176499v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/90/0c/900ca1b73852ed45bd7e42a6119192dd/0130174841v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/5e/ed/5eed37b21283f8f364a37d025d53fa48/0130167146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bb/2a/bb2ac8404ae7b3f08a5c01d1ca0615a7/0130182922v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ef/9d/ef9dc7f8402f3f4ff42268e573921bc4/0130129635v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/62/3a/623ac694d217a/ept-connectors-rgb-quadrat.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/69/72/69721860571ff/logo.jpeg)

:quality(80)/p7i.vogel.de/wcms/af/78/af78d1a793e1dc1cb774ecacafa12365/0126572790v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/02/a6/02a682df26d6719ff336c961bd08213f/0125019920v2.jpeg)