Anbieter zum Thema

Wie bei SiC-Leistungsbausteinen von Cree üblich, ist der Z-FET der Industriestandard mit dem am gesamten Markt die niedrigsten Leckstrom. Der 1200 V/50 A-Z-FET weist bei 1200 V einen Leckstrom von 2 µA auf, sodass das Stromverhältnis zwischen Ein- und Aus-Zustand 2,5x107 beträgt. Derart niedrige Leckströme sind bei SiC-Leistungshalbleitern ein höchst wünschenswertes Merkmal, um die Effektivität des Screening-Prozesses zu maximieren, der dafür sorgt, dass keine Bauelemente mit Frühausfällen zur Auslieferung gelangen.

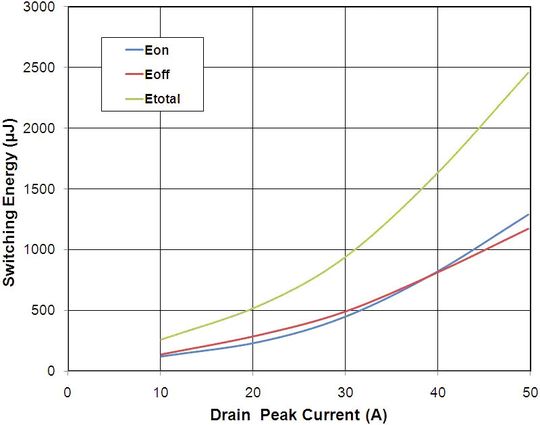

Mit dem neuen Z-FET wurden Doppelimpuls-Tests unter Verwendung einer standardmäßigen Anordnung zum Schalten einer induktiven Last mit Klemmung durchgeführt, mit einer Drossel von 856 µH und einem Kondensator von 42,3 µF. Ein externer Gatewiderstand von 3,8 Ω in Reihe mit dem internen Gatewiderstand von 1,5 Ω ergab einen Gesamt-Gatewiderstand von 5,3 Ω. Der Z-FET wurde mit 800 V im gesperrten Zustand geschaltet, und der Drainstrom nahm von 10 A auf 50 A zu.

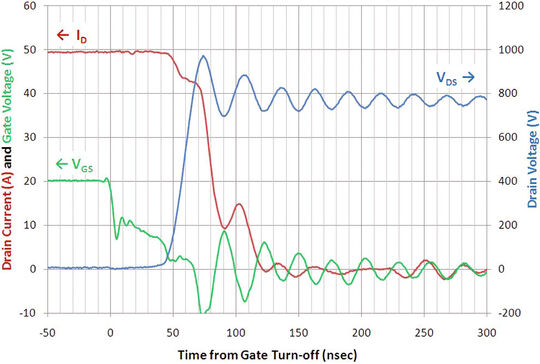

Die Abschaltkurven für 50 A sind in Bild 3 wiedergegeben. Man erkennt das extrem schnelle Abschaltverhalten des Z-FET, wenn die Gatespannung im Ein-Zustand 20 V und im Aus-Zustand 0 V beträgt. Die Zeitachse ist auf den Moment bezogen, in dem die Gatespannung auf weniger als 10% des Werts im Ein-Zustand gefallen ist, sodass die Schaltzeiten abgelesen werden können. Die Abschaltverzögerung beträgt 50 ns, gefolgt von einer Spannungs-Anstiegszeit von 18 ns und einer Strom-Abfallzeit von 30 ns.

Sämtliche Zustandswechsel erfolgen sehr scharf und ohne irgendwelche Tail-Ströme, die der Schaltfähigkeit konventioneller Si-IGBTs Grenzen setzen. Schaltungsdesigner können deshalb mit höheren Schaltfrequenzen experimentieren, um die Gesamtkosten des Systems zu senken. Das im Diagramm erkennbare Schwingen entsteht übrigens nicht durch den geprüften Baustein, sondern ist schaltungsbedingt und ließe sich durch ein besser optimiertes Design minimieren.

Artikelfiles und Artikellinks

(ID:36093640)

:quality(80)/p7i.vogel.de/wcms/9f/13/9f13686bb894142875a93de7f6c3aabe/0131278942v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e1/9c/e19ca48e7ee7b6604240bdb1a02a3a7d/0131251245v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/8c/f0/8cf0a380137d81e18ab1683a061b7531/0131171547v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/4b/c1/4bc195078a1cc19f3f42f3fdea3cc8c5/0131260433v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/42/65/426590889d9cc3c850ba2ed6184b28d8/0131183751v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/61/a8/61a87a52d28be928c7874cd43193f3d4/0131178325v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/17/71/1771c0b139e32eced60c0f60abd045dc/0131202175v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ab/6e/ab6ee4358adb3ef565a3af4e923dae6b/0131202314v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a0/b7/a0b74e201c3d9a12af0a204e1e578aad/0131136338v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d2/1c/d21cea8a73c1dc8b94322e896fb7cc2b/0131036508v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/be/81/be8197dbe5f61c3c5ade3732457725af/0131041847v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/58/ed/58ede6960020a2ded5f6771bd9b8e49d/0131277913v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/77/06/77065703c81be2dd11397359059b74ca/0131276872v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/22/fa22ead6e6fe569ec03e08eba146bedc/0131141465v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/2e/78/2e789ef76c84f5fcdf02b5697a22f9ab/0131062677v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d4/1d/d41d81ec84a42b4fd5d732d36d0021ce/0130877962v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9c/79/9c798ab2b4c18ba0a2c24f2491798d36/0130550888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/e7/b6e755d9e704319c0bb59dc1ac2d67e8/0130537290v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/34/1f/341f0c9b899c7509a01c9a13383af6cf/0131148001v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ca/8c/ca8cda9df29d8b2cf6f7b09abd8b7dda/0131065542v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/71/fa71d141fca285824eb23f3aba1333f2/0131012876v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/05/83/0583267ea76f0beb94c4acef52d485e1/0130855074v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b5/54/b5548923d20a751319550a3eb159af21/0131159519v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/87/b6/87b60368567da3c6b65107c55f5f69ec/0130689118v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b4/55/b455edd54c7e92e0f5bf2d059e2cc5ca/0130990400v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/22/c5/22c556143a9c1d17bff3c3ab153a1120/0131275477v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/42/fa424fa7fe94e1ba17869e270e2b2422/0131203375v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/75/10/75102cf1bcc950d376da7fc4e9722ebe/0131066528v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/9600/9682/65.jpg)

:fill(fff,0)/p7i.vogel.de/companies/69/72/69721860571ff/logo.jpeg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/111200/111228/65.jpg)

:quality(80)/p7i.vogel.de/wcms/09/1a/091a7ac9803320f236c17c8928b86860/0126675518v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/67/08/6708123c5c01f8b51299aee83b938579/0127450020v3.jpeg)