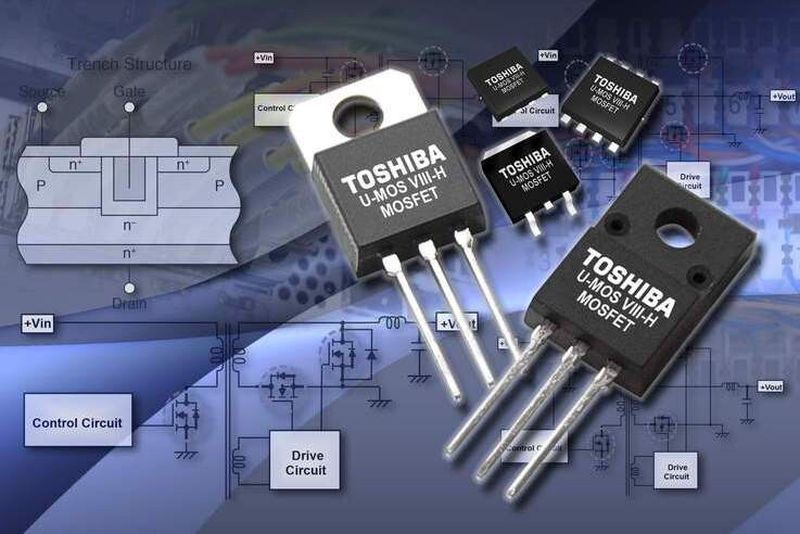

Low-Voltage-Leistungs-MOSFET Nächste U-MOS-Trench-Generation für Stromversorgungen

Die U-MOS-VIII-H-Struktur macht es möglich, bei unverändertem On-Widerstand die Chip-Größe um 47% zu verkleinern oder bei gleicher Die-Fläche den RDS(on) um mehr als die Hälfte zu senken.

Anbieter zum Thema

Der Druck seitens Kunden und Gesetzgebung sorgt zusammen mit einem höheren Umweltbewusstsein und der Sorge um eine sichere Energieversorgung für ständig verbesserte Wirkungsgrade bei Schaltnetzteilen. Entwickler von AC/DC- und DC/DC-Wandlern suchen nach Lösungen, um den Gesamtstromverbrauch weiter zu senken. Dabei müssen die Leistungsfähigkeit, der Platzbedarf der Leiterplatte, die Betriebsumgebung und die Kosten moderner Schaltnetzteile beachtet werden. Auf diesem Spielfeld übernehmen die Low-Voltage-Leistungs-MOSFETs eine besondere Rolle.

Diskrete Low-Voltage-Leistungs-MOSFETs bieten nur einen Bruchteil der Leitungsverluste von Schottky-Dioden, die üblicherweise in Gleichrichtern eingesetzt werden. Diese MOSFETs werden bei der Entwicklung von Stromversorgungen immer wichtiger – vor allem, wenn es um die Stromaufnahme, den Platzbedarf und die Leistungsfähigkeit geht. Dies trifft vor allem auf Bausteine mit Drain-Source-Spannungen unter 250 V zu, die in AC/DC- und DC/DC-Wandlern für Kommunikationstechnik, industriellen Steuerungen, Haushaltsgeräten und Computer-Peripherie zu finden sind. Wachsende Märkte für Low-Voltage-MOSFETs bilden die Antriebe für Elektrofahrräder und Elektrowerkzeuge sowie unterbrechungsfreie Stromversorgungen (USV).

Die Bilder 1 und 2 zeigen typische Anwendungen des Low-Power MOSFETs in zwei Wandlern, wie sie in Stromversorgungen für den Telekommunikationsbereich zum Einsatz kommen. Bild 1 ist das Blockdiagramm der AC/DC-Flyback-Stromversorgung. Sie wandelt die Netzwechselspannung um und stellt eine 48-VDC-Bus-Spannung bereit. Die High-Voltage MOSFETs mit einer Nennspannung von 600 V übernehmen das Schalten und die Leistungsfaktorkorrektur auf der Primärseite. Low-Voltage-MOSFETs mit UDSS von 100 bis 200 V sorgen für das sekundärseitige Schalten.

Einen isolierten Vollbrücken-DC/DC-Wandler zeigt die Schaltung in Bild 2. Ihre Low-Voltage-MOSFETs mit Nennspannungen zwischen 60 und 250 V übernehmen das Schalten auf das Primärseite. Das sekundärseitige Schalten erledigen MOSFETs mit den Nennwerten 30 und 60 V. Auch im weiteren Verlauf werden MOSFETs mit niedriger Nennspannung verwendet: in den High-Side- und Low-Side-Schaltern der nicht isolierten Point-of-Load-Wandler (PoL), die schließlich die erforderlichen niedrigen Spannungen für die CPUs und den Speicher bereitstellen.

Die richtige Wahl eines effizienten diskreten MOSFETs wurde früher durch den einfachen Vergleich des Durchlasswiderstandes (RDS(on)) verschiedener MOSFETs getroffen. Da jedoch immer schnellere Schaltzeiten und höhere Leistungsdichten gefordert sind, müssen Entwickler heute bei der Suche nach dem besten MOSFET auch die verschiedenen Gütezahlen (FOM – Figure of Merit) berücksichtigen.

Die richtigen Abwägungen für die Anwendung treffen

Durchlassverluste spielen weiterhin eine wichtige Rolle, allerdings rückt RDS(on)*A (Durchlasswiderstand pro Fläche) zunehmend ins Interesse, da die Chip-Fläche einen wichtigen Faktor der Produktkosten ausmacht. Schaltverluste durch parasitäre Induktivitäten und Gate-Ladungen sind ebenfalls von Bedeutung. Weil sich die Verluste abhängig von der Last ändern, muss auch RDS(on)*Ciss (das Produkt aus Durchlasswiderstand und Eingangskapazität) berücksichtigt werden. Damit ergibt sich eine FOM für die Bewertung von Ansteuerungs- und Schaltverlusten, die auch den Einfluss der Ausgangslast bei Spannungsversorgungen berücksichtigt.

Die Hersteller von Leistungs-MOSFETs stehen vor einem Dilemma: wird eine FOM verbessert, kann sich dies nachteilig auf eine der anderen FOMs auswirken. Wird zum Beispiel die Größe des MOSFET-Chips verkleinert, verbessern sich zwar die Schaltverluste, aber der Durchlasswiderstand steigt. Die Hersteller investieren daher in neue Halbleiterfertigungsprozesse und Gehäusetechnik, um diese Kompromisse zu mindern.

MOSFETs mit relativ niedriger UDSS werden heute in einem Halbleiterprozess mit Trench-Struktur gefertigt (Bild 3). Damit ergeben sich hohe Kanaldichten, da die Kanäle senkrecht miteinander verbunden werden und im Gate-Bereich eine U-Form bilden. Im Vergleich zu anderen Strukturen ergibt sich damit ein wesentlich geringerer RDS(on). Für Hersteller besteht die Herausforderung nun darin, diesen Prozess weiter zu verbessern, damit auch die bestmögliche Leistungsfähigkeit in Bezug auf andere Gütefaktoren erreicht wird.

(ID:37125930)

:quality(80)/p7i.vogel.de/wcms/0a/53/0a534c0daa99d98d76ef997c2feeadbc/0129851452v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/39/60/3960ad6bca80ca1cb5a8a2c9324ffb1d/0129805397v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f1/2f/f12fcea90f39543f7eeb41528887fffd/0129805649v6.jpeg)

:quality(80)/p7i.vogel.de/wcms/54/f7/54f7cf5677a326f971b22e707ec1f517/0129875407v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/4c/a4/4ca4c53a71bb38c669f5f52dfd1cfe5f/0129876711v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/a6/1c/a61c50d4dc4fcfae6232f2c8335116cd/0129831230v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/99/f0/99f06a9873a11a1ddc3d3f3f54340cb8/0129846572v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/8d/e3/8de3f22c5459f6be19786689dad60b22/0129853808v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6a/6d/6a6dea9b7759811b43eeb145e309b948/0129830738v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d4/bf/d4bf7f51c7650de295ea94bf5e9a0293/0129886904v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e1/78/e17860d5b42a0bc53e323868d2777d79/0129752421v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/7a/29/7a2925afc79f63be62ca5fcbc41a70af/0129690250v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/53/fc/53fcc66b478a0859ff3a7818d6bb4e05/0129773718v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/30/1f/301fa3142221a2ee6ba3ef07e89a4ec8/0129690250v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c7/f6/c7f61d0437c7f8fca3c6ff947ba2ad62/0129322490v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/66/0c/660c31afa35398bac9be42f2be73fdc4/0129073529v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9c/35/9c35ed04fa562b190cbc496a695a6802/0128823288v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/a9/ce/a9ceb592c1cd2e292da2584163d8a7d2/0129889562v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/a6/f7/a6f782ef14d445719c970b7b0f4c6c88/0129888616v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bf/e7/bfe77bc5e9766b56129987dabf83134f/0129479309v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d0/79/d079ad3243e85f7049897fdda5257176/0129890483v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/00/a2/00a297f29b3fc1dbb8d1ea62aaec607c/0129876517v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/50/0b/500b54241402014d31ee89af789da164/0129831604v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f3/21/f3219118c5e2062040c81b4c43687b16/0129793768v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/14/d5/14d5c3484ffafb3f8a4e10eb62d2c1ce/0129886083v4.jpeg)

:quality(80)/p7i.vogel.de/wcms/4a/be/4abed5c1ccf36bb32c6020119bb70ee4/0129714009v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6e/71/6e71876dbb108efe74095bf5b4e8a42c/0129894048v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6a/cc/6acc4f803241cfe5b6d60560c0a2b4d9/0126684948v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/69/72/69721860571ff/logo.jpeg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/111200/111228/65.jpg)

:fill(fff,0)/p7i.vogel.de/companies/66/fa/66fa95f62cfdb/logo-positiv-rgb-276x106px.jpeg)

:quality(80)/p7i.vogel.de/vogelonline/bdb/552200/552265/original.jpg)

:quality(80)/p7i.vogel.de/vogelonline/bdb/552200/552266/original.jpg)

:quality(80)/p7i.vogel.de/vogelonline/bdb/552200/552267/original.jpg)

:quality(80)/p7i.vogel.de/vogelonline/bdb/552200/552268/original.jpg)

:quality(80)/p7i.vogel.de/wcms/75/e5/75e5504b9854db5224ef1c6cc6336646/0124132139v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/37/42/3742266667f58f76cce4058d6ffe30f8/0127447996v3.jpeg)