Anbieter zum Thema

Problematische Vias in Kupferflächen

Einige Designer verwenden für Zuleitungen auch Kupferflächen. Beim manuellen Verlegen achtet der Layouter auf die minimale Breite der Kupferfläche. Jedoch kann es später durch dynamisches Freistellen von Vias oder bei der Ausgabe von Gerberdaten zu ungewollten und unentdeckten Verjüngungen der Kupferflächen kommen. Eine optische Kontrolle ist nur mit Kenntnis des funktionellen Designs möglich und eine schlechte Dokumentation eine häufige Fehlerquelle bei Redesigns, weil sich unbeabsichtigt Verjüngungen einschleichen und lokale Überhitzungen verursachen.

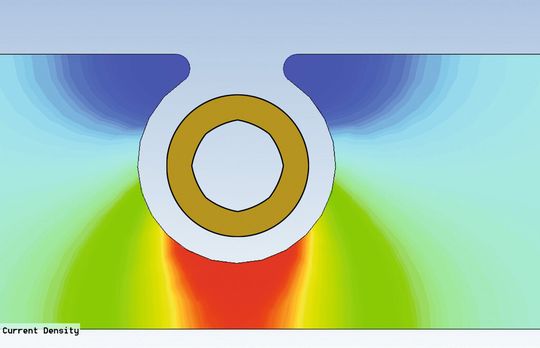

In Bild 2 ist die Stromdichte einer Kupferfläche zu sehen, in die eine Durchkontaktierung mit entsprechender Freistellung eingebracht wurde. Der Querschnitt der Kupferfläche hat sich hier auf etwa 25% reduziert und führt an der Engstelle zu einer unzulässigen Überhitzung. Dass man Vias später durch Kupferflächen führt, ist ein häufiger Anwendungsfall.

Mit der IR-Drop-Analyse lässt sich der Spannungsabfall und auch die Stromdichteverteilung im Kupfer analysieren. Überall an den Stellen, an denen die Stromdichte einen vorgegebenen Grenzwert übersteigt, muss die Verjüngung beseitigt werden. Diese Analyse lässt sich auch über den Constraint Manager automatisieren und alle Hochstromleitungen bzw. Flächen, Vias und Anschlusspins auf die maximale Stromdichte hin untersuchen.

Same Net DRC – Regelprüfung für Sense-Leitungen

Versorgungsleitungen mit hohen Strömen müssen meist über eine Messleitung (englisch sense) kontrolliert werden. Dabei ist es wichtig, dass das Routen des elektrischen Netzes in einer bestimmten vorgegebenen Reihenfolge erfolgt und dass vom letzten Punkt eine Messleitung zurück zum Schaltnetzteil eine gekoppelte Regelung steuert.

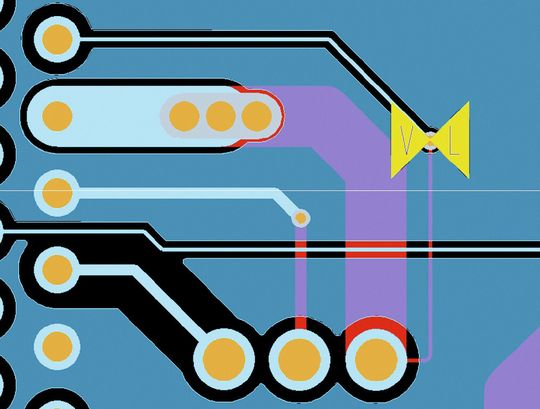

Im Allegro Constraint Manager kann man die Reihenfolge der Anschlusspunkte mit Net-Scheduling exakt vorgeben und es wird sofort auf Verstöße hingewiesen. Die Sense-Leitung hat meist eine unterschiedliche Leiterbahnbreite, weil hier kaum Strom fließt. Somit werden die Leiterbahnbreiten mit unterschiedlichen Leitungsbreiten definiert. Zusätzlich ist auch ein Mindestabstand der Sense-Leitung zum Hochstromsegment des gleichen Netzes gefordert.

Mit Same Net DRC kann der Mindestabstand definiert und als DRC kontrolliert werden, damit es nicht zu ungewollten Kurzschlüssen mit dem selben Netz kommt (was zwar elektrisch keinen Fehler darstellt, jedoch die Messung des Spannungsabfalls am letzten Verbraucher verfälscht und damit dem Schaltnetzteil falsche Werte einkoppelt).

Bei Strömen bis 125 A auf der Leiterplatte zusammen mit FPGAs und SMT-Bauteilen reichen meist die üblichen Leiterbreiten nicht mehr aus, sodass dann direkt unter der Top-Lage ein blanker Draht in der Leiterplatte integriert werden kann. Die Drahtschreibetechnik hat den Vorteil von planen Oberflächen, die eine spätere SMT-Bestückung zulassen.

Artikelfiles und Artikellinks

(ID:32498630)

:quality(80)/p7i.vogel.de/wcms/9f/13/9f13686bb894142875a93de7f6c3aabe/0131278942v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e1/9c/e19ca48e7ee7b6604240bdb1a02a3a7d/0131251245v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/8c/f0/8cf0a380137d81e18ab1683a061b7531/0131171547v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/40/00/4000cee04363c2ad502a5cfadded2e0e/0131287222v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/4b/c1/4bc195078a1cc19f3f42f3fdea3cc8c5/0131260433v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/42/65/426590889d9cc3c850ba2ed6184b28d8/0131183751v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/17/71/1771c0b139e32eced60c0f60abd045dc/0131202175v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ab/6e/ab6ee4358adb3ef565a3af4e923dae6b/0131202314v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a0/b7/a0b74e201c3d9a12af0a204e1e578aad/0131136338v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d2/1c/d21cea8a73c1dc8b94322e896fb7cc2b/0131036508v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/be/81/be8197dbe5f61c3c5ade3732457725af/0131041847v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/5b/f2/5bf2fc2e46775b70614326a4003940ea/0131238162v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/58/ed/58ede6960020a2ded5f6771bd9b8e49d/0131277913v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/77/06/77065703c81be2dd11397359059b74ca/0131276872v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/2e/78/2e789ef76c84f5fcdf02b5697a22f9ab/0131062677v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d4/1d/d41d81ec84a42b4fd5d732d36d0021ce/0130877962v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9c/79/9c798ab2b4c18ba0a2c24f2491798d36/0130550888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/e7/b6e755d9e704319c0bb59dc1ac2d67e8/0130537290v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/aa/79/aa79a807ba1ce61e6656226679e05f9c/0131288690v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/34/1f/341f0c9b899c7509a01c9a13383af6cf/0131148001v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ca/8c/ca8cda9df29d8b2cf6f7b09abd8b7dda/0131065542v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/c2/35c2b1da065361aefeea668c786531c9/0131280558v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/05/83/0583267ea76f0beb94c4acef52d485e1/0130855074v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b5/54/b5548923d20a751319550a3eb159af21/0131159519v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/87/b6/87b60368567da3c6b65107c55f5f69ec/0130689118v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/7d/5b/7d5bd7b3575dd8745fac17cf8619a7c2/0131253052v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/94/82/948296f1541e8d3b2060978cfeae90e8/0131311058v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/42/fa424fa7fe94e1ba17869e270e2b2422/0131203375v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/19/75/1975839f578e6bed7a0db82789cd96a4/0131312221v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/69/9c/699c6104d5166/logo-pp-rot-quadratzuschnitt-inv512px.png)

:fill(fff,0)/p7i.vogel.de/companies/64/21/64219ce08bf52/logo.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/5f/88/5f8847c90d2e4/50-mm.jpg)

:quality(80)/p7i.vogel.de/wcms/66/c1/66c14543fd48c69fe35aeca2e513966a/0125007023v5.jpeg)

:quality(80)/p7i.vogel.de/wcms/ea/38/ea382ed3c791a2d0af94477a28f458a3/0126028434v2.jpeg)