Hochspannungshalbleiter HV-Si-MOSFETs im Vergleich zur SiC- und GaN-Technologie

Wie schneidet die Siliziumtechnologie im Vergleich zu SiC und GaN ab? Der Beitrag zeigt die Unterschiede der Technologien hinsichtlich Herstellung, Leistung und Preis.

Anbieter zum Thema

In der Vergangenheit ist die Frage aufgeworfen worden, wie sich wohl Silizium gegenüber Materialien mit großem Bandabstand (Wide Band Gap), wie Siliziumkarbid (SiC) und Galliumnitrid (GaN), behaupten wird. Heute kommen bei Silizium-Hochspannungsbauelementen viele verschiedene Technologien zum Einsatz. Die MOSFET- und JFET-Technologien teilen sich auf in MOSFET (Si) mit konventioneller Planar-Technologie und Superjunction-Technologie, MOSFETs (SiC) in konventioneller Planarstruktur und JFETs (GaN) als selbstleitend und selbstsperrend.

Bei MOSFETs ist das Segment der Hochspannungsbauelemente (für Spannungen von mindestens 400 V) dasjenige, das die größten Zuwachsraten aufweist. Gegenwärtig betrifft ein Großteil der Nachfrage nach Superjunction-Bauelementen den Bereich von 500 bis 650 V, ein kleinerer Anteil den Bereich von 800 bis 900 V. Konventionelle Planar-Bauelemente machen hier einen Wert von 1,5 Mrd. US-$ aus, wobei die wichtigsten Marktsegmente Computer, Büro- und Konsumartikel sind.

Konventionelle Planar- und Superjunction-MOSFETs

Ein Vergleich der beiden Si-MOSFET-Technologien bei ähnlichen Chipgrößen zeigt, dass beide ihre Vorteile haben. Superjunction-MOSFETs sind leistungsorientiert. Ihre Leitungsverluste sind geringer, da sie, verglichen mit herkömmlichen Planar-Bauelementen, bei gleicher Spannung den On-Widerstand auf ein Viertel herabsetzen können. Außerdem hat ihr niedriger On-Widerstand niedrigere Schaltverluste zur Folge, da solche Schalteigenschaften wie QGD und Rückwirkungskapazität (Crss) verringert werden.

Die konventionellen Planar-MOSFETs sind wertorientiert. Bei gleichem On-Widerstand wie ein Superjunction-Bauelement bietet ihr größerer Chip höhere UIS-Robustheit (Unclamped Inductive Switching) und bessere Wärmeableitung. Darüber hinaus sind aufgrund des einstufigen Epitaxialwachstums ihre Herstellungskosten geringer und mit ihren niedrigeren Schaltgeschwindigkeiten einfacher zu integrieren.

Konventionelle Si-Planar- vs. Si-Superjunction-Technologie

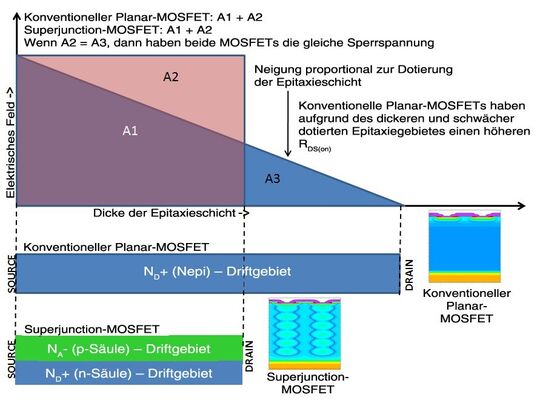

Um den Unterschied zwischen den beiden Si-MOSFET-Technologien zu erklären, müssen wir bei den Grundlagen beginnen. Konventionelle Planar-MOSFETs haben in der Regel einen hohen RDS pro Einheitsfläche. Deshalb sind große Chips erforderlich, um einen niedrigen RDS(on) zu erzielen. Ein größerer Chip weist jedoch eine geringere Stromdichte und eine bessere Wärmeableitung auf. Das führt dazu, dass konventionelle Planar-MOSFETs robuster als Superjunction-Bauelemente mit gleichem On-Widerstand sind.

Bei der Superjunction-Struktur (ladungsausgeglichen) besteht ein linearer Zusammenhang zwischen On-Widerstand und Durchbruchspannung. Bei dicker werdender Epitaxieschicht nimmt der On-Widerstand proportional zur Durchbruchspannung zu. Tatsächlich ist der On-Widerstand eines Superjunction-MOSFET bei gleicher Durchbruchspannung und Chipgröße niedriger als bei einem konventionellen Planar-Bauelement.

Kleinere Chipgrößen mit gleichem On-Widerstand werden bei Superjunction-MOSFETs durch den Ladungsausgleich erzielt. Bei einer stärkeren Dotierung der n-Zone nimmt ihr On-Widerstand ab. Die in der n-Zone vorhandene Ladung wird durch die Ladung in den p-Säulen ausgeglichen. Dies ermöglicht eine lineare Beziehung von On-Widerstand und Durchbruchspannung. Der spezifische On-Widerstand von Superjunction-Bauelementen beträgt heute in der Regel etwa ein Viertel von dem konventioneller Planar-MOSFETs, abhängig von der Betriebsspannung. Die Verringerung des Widerstandes bei Superjunction-Bauelementen hat offensichtliche Vorteile wie etwa geringere Leitungsverluste, eine Verkleinerung der Chipfläche bei dieser Technologie und geringere Kapazitäts- und Dynamikverluste.

Hinweis: Bei einer Zunahme des On-Widerstandes von konventionellen Planar-MOSFETs nimmt auch die Kapazität zu. Das liegt daran, dass bei dicker werdender Epitaxieschicht bei konventionellen Planar-Bauelementen der Chip vergrößert werden muss, was die Kapazität erhöht (höherer Rds-A).

Da konventionelle Planar-MOSFETs mit einer einzigen, in einem Schritt aufgewachsenen Epitaxieschicht hergestellt werden, sind ihre Produktionskosten geringer als bei Superjunction-Bauelementen, was sie zu einem Value Play macht. Deshalb werden sie hauptsächlich im Konsum- und Massenmarkt eingesetzt.

Durch Verwendung der Ladungsausgleichs-Technologie kann Vishay hervorragende spezifische On-Widerstandswerte bei den 600- und 650-V-MOSFETs bieten.

(ID:37951610)

:quality(80)/p7i.vogel.de/wcms/d8/78/d878b7bfc23826e6ddfce42443836d28/0130384280v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e9/ce/e9ce137e87eccac328ec5504c586c477/0129711019v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/68/46/684697b6eb687384e0d8c6803450401a/0130056395v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/88/a1/88a15070daae8c090f4256580cf8a61c/0130329906v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f7/90/f79070d95e48c6d1a5c77c5d05a7e4da/0130344018v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/1b/bb/1bbb096db776f5ab19ff87fc7f86392f/0130318021v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6a/42/6a423ced6604acf7d3eef8e4c0c2bd39/0130317237v4.jpeg)

:quality(80)/p7i.vogel.de/wcms/a2/31/a2319b6d6b473424b275f6489bbce348/0130213768v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/88/c28805ea7b2261235475146a5b0c61f8/0130313028v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/8d/fa8dedee195f29c33c89d86311c258ee/0130104146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cc/13/cc1378375499a26b5ddbb309d2155acb/0130085649v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/85/b0/85b0b32128f6d1968e975043f1e0b67b/0130342166v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/81/c0/81c03683c33cf69903df78a57145bcca/0130328599v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6d/f0/6df06a1488ceb6357c287fee993fad65/0130161592v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/10/45/1045969e69a1db4aaa73d0f74f55cc02/0129962687v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c7/f6/c7f61d0437c7f8fca3c6ff947ba2ad62/0129322490v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/66/0c/660c31afa35398bac9be42f2be73fdc4/0129073529v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/e4/bae4e54395e5a53088060531ef99b814/0130359274v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/af/35af7dd326d198475d06fbb69aa600b5/0130175971v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/2e/c02e7bf72bfc434888c37100e2511681/0130127767v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/ac/31/ac31fbd47f85c24ae7d13a73555c85e6/0130236430v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ef/a0/efa0d8af7bcf1d64636b877a04b853d9/0130136738v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bf/82/bf82f81061b759c454e15ec4c2e7560b/0130110139v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/74/96/74964a7715c738a9e8b17681445ceed3/0130103633v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/2f/b5/2fb51bc9f8702faa2195070c97fe7754/0130349161v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/78/ab/78abfaed29756f96d23ae135f707026a/0130332461v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b9/e5/b9e56a5eba2fbf56a6e3efac57f96dbb/0130345302v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9c/06/9c0651d3c2cec436277af3f698a6cf3f/0130342944v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/02/f8/02f84dfb1ad4ccfe94f3b4045bcee023/0130316909v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a2/b5/a2b54e377a6050b54acf8ac938b63ef8/0130318106v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/00/08/0008cc4b713f15ab39492f6c66b0485f/0130362942v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/9600/9682/65.jpg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/130400/130457/65.jpg)

:fill(fff,0)/p7i.vogel.de/companies/62/16/621651a93b1ef/logo-we-rgb-pos.png)

:quality(80)/p7i.vogel.de/vogelonline/bdb/553000/553063/original.jpg)

:quality(80)/p7i.vogel.de/vogelonline/bdb/553000/553064/original.jpg)

:quality(80)/p7i.vogel.de/vogelonline/bdb/553000/553065/original.jpg)

:quality(80)/p7i.vogel.de/vogelonline/bdb/553000/553066/original.jpg)

:quality(80)/p7i.vogel.de/wcms/67/fc/67fc1449e69e0f99e382a008f31eec5a/0124431173v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a8/1b/a81bfd6dda03473ba0c5b2ffa2bbd9e4/0127371990v2.jpeg)