Leiterplatten-Design Holistischer Routing-Ansatz von Cadence halbiert die Entflechtungszeit komplexer PCB-Designs

Herkömmliche Autorouter mit sequentiellen Entflechtungsalgorithmen sind durch ein komplexes Board-Design überfordert. Integrierte Strukturen wie DDR2/3, FPGA oder CPU verlangen ein grundlegend anderes Konzept, um den Design-Regeln schnell entsprechen zu können. Global Routing Enviroment heißt eine neue interaktive Methode, die mit durchschnittlich 40% Zeitersparnis für die geforderte Effizienz sorgt. Wie sie funktioniert, zeigt der Beitrag.

Anbieter zum Thema

Ein ganzheitlicher (holistischer) Ansatz zur Leiterplatten-Entflechtung erfordert die Betrachtung aller Arbeitsbereiche, wobei nicht nur die übergeordneten Prozesse zu berücksichtigen sind, sondern auch welche Prozesse von mehreren Arbeitsbereichen und Anwendern genutzt werden. Der Anwender versucht daher die Daten so gut wie möglich zu definieren und führt eine Reihe von Plausibilitätsprüfungen (DRC-Zyklen oder andere Überprüfungen) durch. Die dadurch gewonnenen Informationen werden solange verfeinert, bis ein befriedigendes Ergebnis vorliegt.

Bei jedem Durchlauf muss der Anwender überlegen, was diese Daten im Einzelnen bedeuten und dabei immer die komplette Lösung im Auge behalten. Abhängig vom jeweiligen Status des Designs können Umfang und Art der zur Verfügung stehenden Daten sehr unterschiedlich sein. Bei der Platzierung der Bauteile werden anfänglich meist nur die geometrischen Daten und die Verbindungen benötigt.

Das logische Verbindungsmuster schaffen

Aus der Perspektive der EDA-Design-Software stellen geometrische Daten dar, was im endgültigen Design in Form von Metall/Kupfer realisiert wird, etwa Pins, Durchkontaktierungen, Kupferflächen oder Verbindungsleitungen. In diesem frühen Stadium können zudem auch Design-Regeln vorliegen. Die Aufgabe in dieser Phase besteht darin, herauszufinden wie alle Komponenten auf dem verfügbaren Platz untergebracht werden können, sodass sich ein logisches Verbindungsmuster ergibt.

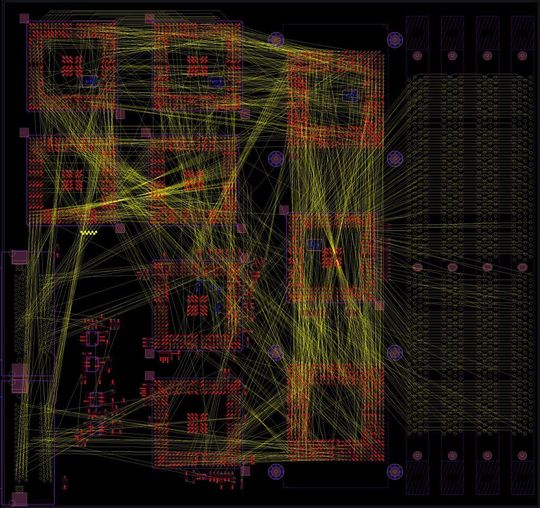

Oft ist hier die Datenmenge ein Problem. Die Anschlussfähigkeit kann Tausende von Elementen erfordern, die das Ganze unübersichtlich machen (Bild 1). Eine Abstraktion der Daten ist somit zwingend. Dadurch kann ein Clustering-Effekt erzeugt werden, der nur die Verbindungen darstellt, die wirklich nötig sind ohne den Bildschirm mit redundanten Informationen zu Verbindungsdaten zu überladen.

Nach der Platzierung kann mit dem Routing des Designs begonnen werden. In dieser Phase sind die Design-Regeln bereits umfassend definiert und lassen sich nun auf die Verbindungen anwenden. Der Anwender hofft jetzt, dass seine Design-Absicht richtig ist. Aber erst wenn die Leiterplatte vollständig entflochten ist, zeigt sich, ob ausreichend Platz verfügbar war, um diese auch implementieren zu können.

Gruppierungen suchen und Bundles bilden

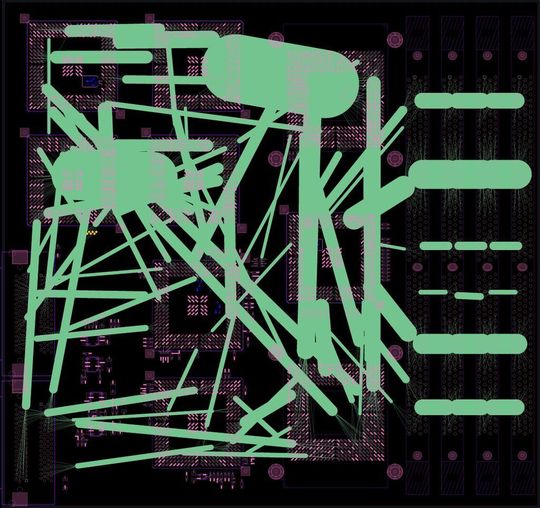

Bild 1 zeigt große Gruppen von Elementen (Ratlines), die mit den gleichen Punkten oder Bauteilen verbunden sind. Diese lassen sich gruppieren und durch eine einzige größere Einheit (ein Bundle) darstellen (Bild 2). Ein derartiges Bundle enthält Informationen zu Leitungsbreiten und Abständen aller enthaltenen Signale und kann auch die Informationen über die jeweilige Topologie umfassen, wie beispielsweise die Reihenfolge (Treiber links, T-Punkt in der Mitte, Last-Pins rechts).

Wird dieser Bundle-Ansatz nun auf das ursprüngliche Design übertragen, erhalten wir eine klare Darstellung der Design-Connectivity ohne den Bildschirm zu überfrachten und den Anwender zu überfordern. Damit der Anwender sich auf bereits bekannte Referenzpunkte beziehen kann, sollten für die in der grafischen Interconnect-Flow-Planungsarchitektur verwendeten Objekte ähnliche Namen, Konzepte und Attribute genutzt werden, wie sie der Anwender aus seiner Arbeit in der Cadence-Allegro-PCB-Umgebung bereits kennt.

Umsetzen der Bundles in andere Strukturen

(ID:334410)

:quality(80)/p7i.vogel.de/wcms/46/7c/467c0afffbfd10c3553c2888a4a6289f/0130479810v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/12/3d/123d9eb2c2e4ce13296371a2ad3718a4/0130412664v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d8/78/d878b7bfc23826e6ddfce42443836d28/0130384280v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/13/20/13208d1c2797edd67d9ff216b403726b/0130471595v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/38/cb/38cbe19e814dd30b94780bc3946547ab/0130446533v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a3/3e/a33e6d8a927d539ec6c3a0537f48f0f1/0130440028v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6b/61/6b61373f1c3f06f7f9343e6b0f0e9cc8/0130225062v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/15/93/1593dd152e6d58c5fc5da0d331777c54/0130357398v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/88/c28805ea7b2261235475146a5b0c61f8/0130313028v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/8d/fa8dedee195f29c33c89d86311c258ee/0130104146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cc/13/cc1378375499a26b5ddbb309d2155acb/0130085649v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6d/91/6d91abfa1b16ffcf470c7147facd7aa8/0130387695v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/85/b0/85b0b32128f6d1968e975043f1e0b67b/0130342166v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/1a/53/1a539631c940d184689460600bd2b395/0130410666v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/10/45/1045969e69a1db4aaa73d0f74f55cc02/0129962687v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c7/f6/c7f61d0437c7f8fca3c6ff947ba2ad62/0129322490v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/e4/bae4e54395e5a53088060531ef99b814/0130359274v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/af/35af7dd326d198475d06fbb69aa600b5/0130175971v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/2e/c02e7bf72bfc434888c37100e2511681/0130127767v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/7c/04/7c04916c305164fb10bc6cb05b51d934/0130431065v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/64/e5/64e5e333492f182ab7df5ab4c2b54c1e/0130463252v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/0a/95/0a95db4508128c4e11d5d268bf2c0a77/0130440053v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b3/65/b365dd5433c8b6d36c56c92b72f5b368/0130401081v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/85/c0/85c0cdd8fd326013aed52ca96777c998/0130426877v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f0/78/f07826d6c4e995980f1ada3377416aac/0130403626v4.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/c8/b6c8f7732da417bda3d298412f4c0ed8/0130453104v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/47/ce/47ce64bad7990f276f68cbb24505f6dd/0130472850v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/15/56/15564dea31861c376a385658c3b961a3/0130465243v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/98/ad/98ad595a6372aae8dbeac71681d23f41/0130450258v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bf/2a/bf2aad428ab1a80e6738fdbdc2efeb7e/0130453420v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/5f/88/5f8847c90d2e4/50-mm.jpg)

:quality(80)/p7i.vogel.de/wcms/9c/21/9c21e09a281f8cafe81528fc9060e43e/0125420315v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/de/48/de48603453b0bd091cef84dbbefe37c1/0126851659v2.jpeg)