Anbieter zum Thema

JTAG-Schnittstelle für Debugging

Die JTAG-Schnittstelle kann auch für das Program-Debugging benutzt werden. Das JTAG Interface ist auf dem Digital-Board mit den Pins 91 bis 96 der MCU galvanisch verbunden. Der JTAG-Bus besteht aus folgenden Leitungen: Test, TDO, TDI, TMS, TCLK und RESET (RST). TDO steht für Test Data Out; TDI für Test Data In. TMS bedeutet Test Mode Selektion und TCLK ist der Testtakt. Mit verschieden Tools wie IAR Systems oder CCS kann der Programmcode-Download via JTAG durchgeführt werden.

Für die USB-Schnittstelle wurde ein USB-Chipset implementiert, das aus dem TUSB3410 (IC8), TPD4E001 (IC9) und einem Speicherbaustein (IC10) besteht. Der TPD4E001 dient als ESD-Schutz am USB-Eingang. Der USB-Serial-Controller (IC8) verbindet den Host-PC mit dem seriellen Anschluss des Hauptcontrollers MSP430F5438. Dieser überwacht mit Hilfe des Port P2.0 (interruptfähig), der als Eingang konfiguriert ist, die USB-Verbindung zum Host. Wird ein High-Signal am Bus detektiert, wird der Hauptcontroller vom Low-Power-Modus in den aktiven Modus gebracht. Alle verwendeten Bausteine mit Ausnahme des Speicher-ICs sind von TI.

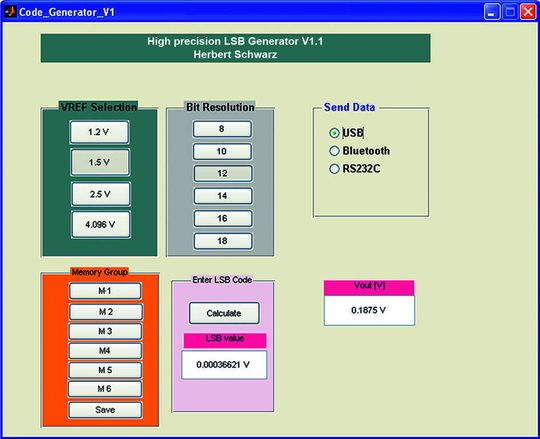

Bild 2 zeigt die entwickelte Matlab-Oberfläche als GUI (Graphical User Interface). Da diese Applikation mit einer USB-Schnittstelle ausgestattet ist, kann der LSB-Generator auch in ein automatisiertes Test-Setup integriert werden. Dabei spielt es keine Rolle mit welchem Programm das Setup realisiert wurde. Viele Engineering Tools wie Matlab, LabView oder Agilent VEE Pro sind dafür geeignet. Hier wurde Matlab verwendet.

Artikelfiles und Artikellinks

(ID:298594)

:quality(80)/p7i.vogel.de/wcms/9f/13/9f13686bb894142875a93de7f6c3aabe/0131278942v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e1/9c/e19ca48e7ee7b6604240bdb1a02a3a7d/0131251245v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/8c/f0/8cf0a380137d81e18ab1683a061b7531/0131171547v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/8c/87/8c87c3a5ca9b98a84775dd79fc0e3261/0131341947v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/0f/3e/0f3e4cfa27ea41173ebece10fa1b6128/0131337152v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/40/00/4000cee04363c2ad502a5cfadded2e0e/0131287222v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/b9/c2b94412f90cbea098c5b0a49e93e3f7/0131368512v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/17/71/1771c0b139e32eced60c0f60abd045dc/0131202175v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ab/6e/ab6ee4358adb3ef565a3af4e923dae6b/0131202314v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/4e/a8/4ea857349b0630ab44c1ed52a2b8ea67/0131332364v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a0/b7/a0b74e201c3d9a12af0a204e1e578aad/0131136338v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d2/1c/d21cea8a73c1dc8b94322e896fb7cc2b/0131036508v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/5b/f2/5bf2fc2e46775b70614326a4003940ea/0131238162v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/58/ed/58ede6960020a2ded5f6771bd9b8e49d/0131277913v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/2e/78/2e789ef76c84f5fcdf02b5697a22f9ab/0131062677v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d4/1d/d41d81ec84a42b4fd5d732d36d0021ce/0130877962v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9c/79/9c798ab2b4c18ba0a2c24f2491798d36/0130550888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/e7/b6e755d9e704319c0bb59dc1ac2d67e8/0130537290v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a9/3f/a93f4dac41be6ba50eb634f5e4e7f7b7/0131355751v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/aa/79/aa79a807ba1ce61e6656226679e05f9c/0131288690v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/34/1f/341f0c9b899c7509a01c9a13383af6cf/0131148001v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/c2/35c2b1da065361aefeea668c786531c9/0131280558v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/05/83/0583267ea76f0beb94c4acef52d485e1/0130855074v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b5/54/b5548923d20a751319550a3eb159af21/0131159519v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/87/b6/87b60368567da3c6b65107c55f5f69ec/0130689118v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/7d/5b/7d5bd7b3575dd8745fac17cf8619a7c2/0131253052v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/48/51/48516b200b1181bdca44488163b1aeb7/0131056202v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/fc/fafc9d7589391638461f0a7647e03154/0131317785v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/94/82/948296f1541e8d3b2060978cfeae90e8/0131311058v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/3c/c9/3cc901afed76679636db88f3c6f6ed8a/0131354452v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/68/7f/687fac7d01bdb/ag-2024-logo-4c.png)

:fill(fff,0)/p7i.vogel.de/companies/61/a8/61a8d8e6ca4c2/glyn-logo-profilbild.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/66/1f/661fa8e004810/heitec-logo-2024-1200px-ae.png)

:quality(80)/p7i.vogel.de/wcms/66/ae/66ae52f8630cb5cb79cca71abfee3484/0125308171v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/9b/c29b9e2c5bf7d79336ea3a2a8f8198cd/0127139048v2.jpeg)