Anbieter zum Thema

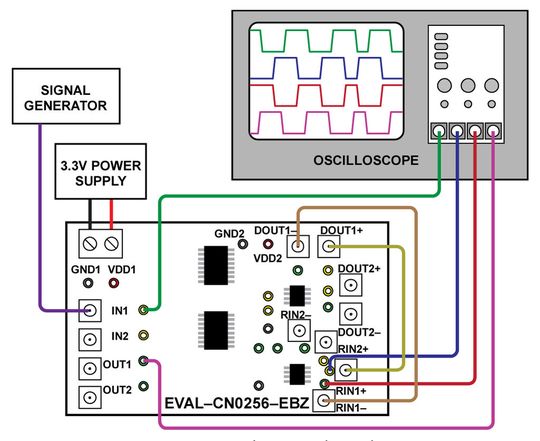

Der LVDS-Empfänger ADN4664 kann LVDS-Signale an RIN1+, RIN1− und RIN2+ bzw. RIN2− empfangen. Die Empfängerausgänge (die ROUT1- und ROUT2-Testpunkte) sind mit dem ADuM3442 verbunden, um die Signale zu isolieren. Die korrespondierenden Logikausgänge am ADuM3442 sind OUT1 und OUT2.

Die Schaltung wird auf der Logikseite über eine Verbindung mit VDD1 versorgt. Diese Versorgungsspannung kann 3,3 oder 5 V betragen und versorgt die Logikseite des ADuM3442 (die Signalisolation für die Schaltung). Außerdem versorgt sie den ADuM5000, der eine isolierte Versorgung für die Bus-Seite der Schaltung liefert.

Der Ausgang VISO des ADuM5000 liefert die 3,3-V-Versorgung für den LVDS-Treiber (ADN4663) und den LVDS-Empfänger (ADN4664) sowie für die Bus-Seite des ADuM3442.

Die in der Applikationsschrift AN-0971 beschriebenen Richtlinien „Recommendations for Control of Radiated Emissions with isoPower Devices” wurden bei der Realisierung des Schaltungslayouts beachtet. Zusätzlich wurde das Layout für eine schnelle differenzielle Signalführung optimiert.

Schnelle differenzielle Signalführung

Die LVDS-Eingangs/Ausgangs-Leiterbahnen haben die gleichen Längen und Impedanzen von 50 Ω gegenüber Masse (100 Ω zwischen differenziellen Paaren). Testpunkte an jedem Paar befinden sich ebenfalls in gleichen Abständen vom Treiber/Empfänger. Mehrere Vias zur Masse sind entlang der Leiterbahnen platziret, um die Signalintegrität bei hohen Frequenzen zu verbessern.

Abschlusswiderstände (R1, R2) von 100 Ω befinden sich an den LVDS-Eingängen RIN1+, RIN1− und RIN2+ bzw. RIN2−. Das Empfangsende aller an DOUT1+, DOUT1− und DOUT2+ bzw. DOUT1− angeschlossenen Busse sollten entsprechende Abschlüsse aufweisen.

Die Versorgung und Masse sind über einen Schraubanschluss (VDD1 und GND1) angeschlossen. Logik-Eingänge/Ausgänge ((IN1, IN2/OUT1, OUT2) sind über vier SMB-Steckverbinder angeschlossen.

Die Bus-Signale sind auf ähnliche Weise über acht SMB-Steckverbinder angeschlossen. Diese sind mit dem LVDS-Treiber (ADN4663) und dem Empfänger (ADN4664) über Leiterbahnen mit Impedanzen von 50 Ω gegen Masse verbunden.

Schaltungsevaluierung und Test

Zur Versorgung der isolierten LVDS-Schnittstellenboards legt man 3,3 oder 5 V an VDD1 an. Um zu testen, dass die Schaltung richtig versorgt wird, überprüft man den Spannungspegel am Testpunkt VDD2. Dieser Testpunkt ist die isolierte Versorgung von ADuM5000 und sollte entsprechend 3,3 oder 5 V betragen.

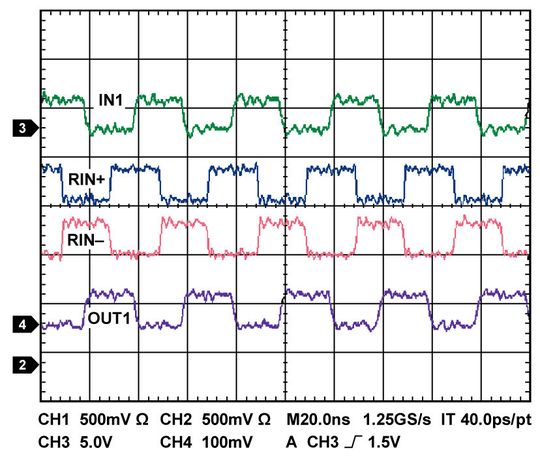

Die Messungen wurden mit Tastköpfen mit niedriger Kapazität (<1 pF) am LVDS-Bus durchgeführt. Für höhere Datenraten sollte man kürzere Leitungen zwischen den LVDS-Aus- und Eingängen verwenden.

* Dr. Conal Watterson arbeitet als Applikationsingenieur in der Gruppe Interface & Isolation Technology (ITG) bei Analog Devices in Limerick, Irland.

(ID:37410220)

:quality(80)/p7i.vogel.de/wcms/d8/78/d878b7bfc23826e6ddfce42443836d28/0130384280v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e9/ce/e9ce137e87eccac328ec5504c586c477/0129711019v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/68/46/684697b6eb687384e0d8c6803450401a/0130056395v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/88/a1/88a15070daae8c090f4256580cf8a61c/0130329906v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f7/90/f79070d95e48c6d1a5c77c5d05a7e4da/0130344018v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/1b/bb/1bbb096db776f5ab19ff87fc7f86392f/0130318021v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6a/42/6a423ced6604acf7d3eef8e4c0c2bd39/0130317237v4.jpeg)

:quality(80)/p7i.vogel.de/wcms/a2/31/a2319b6d6b473424b275f6489bbce348/0130213768v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/88/c28805ea7b2261235475146a5b0c61f8/0130313028v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/8d/fa8dedee195f29c33c89d86311c258ee/0130104146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cc/13/cc1378375499a26b5ddbb309d2155acb/0130085649v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/85/b0/85b0b32128f6d1968e975043f1e0b67b/0130342166v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/81/c0/81c03683c33cf69903df78a57145bcca/0130328599v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6d/f0/6df06a1488ceb6357c287fee993fad65/0130161592v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/10/45/1045969e69a1db4aaa73d0f74f55cc02/0129962687v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c7/f6/c7f61d0437c7f8fca3c6ff947ba2ad62/0129322490v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/66/0c/660c31afa35398bac9be42f2be73fdc4/0129073529v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/e4/bae4e54395e5a53088060531ef99b814/0130359274v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/af/35af7dd326d198475d06fbb69aa600b5/0130175971v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/2e/c02e7bf72bfc434888c37100e2511681/0130127767v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/ac/31/ac31fbd47f85c24ae7d13a73555c85e6/0130236430v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ef/a0/efa0d8af7bcf1d64636b877a04b853d9/0130136738v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bf/82/bf82f81061b759c454e15ec4c2e7560b/0130110139v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/74/96/74964a7715c738a9e8b17681445ceed3/0130103633v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/2f/b5/2fb51bc9f8702faa2195070c97fe7754/0130349161v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/78/ab/78abfaed29756f96d23ae135f707026a/0130332461v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b9/e5/b9e56a5eba2fbf56a6e3efac57f96dbb/0130345302v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9c/06/9c0651d3c2cec436277af3f698a6cf3f/0130342944v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/02/f8/02f84dfb1ad4ccfe94f3b4045bcee023/0130316909v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a2/b5/a2b54e377a6050b54acf8ac938b63ef8/0130318106v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/00/08/0008cc4b713f15ab39492f6c66b0485f/0130362942v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/60/81/6081635146580/odu-logo-ohne-rgb.jpg)

:fill(fff,0)/p7i.vogel.de/companies/69/72/69721860571ff/logo.jpeg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/111200/111228/65.jpg)

:quality(80)/p7i.vogel.de/wcms/cf/c3/cfc33246e9c679418c119edc6de56c90/0124718130v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/85/d68511b043f3cd31b2642019b8234432/0126403283v2.jpeg)