Physically Unclonable Function Erhöhte FPGA-Sicherheit durch Integration einer PUF

Unter Ausnutzung einer Physically Unclonable Function schaffen Sie mit Hilfe eines FPGAs ein ausfallsicheres, umfassend authentifiziertes und dennoch programmierbares Sicherheitsschema.

Anbieter zum Thema

Da die Vielfalt und Anzahl der Sicherheitsrisiken weiter zunimmt, müssen komplexe Systeme und Geräte geschützt werden. FPGAs sind hier keine Ausnahme, und alle FPGA-Hersteller haben die Sicherheitsfunktionen ihrer Bausteine im Laufe der Zeit weiter erhöht.

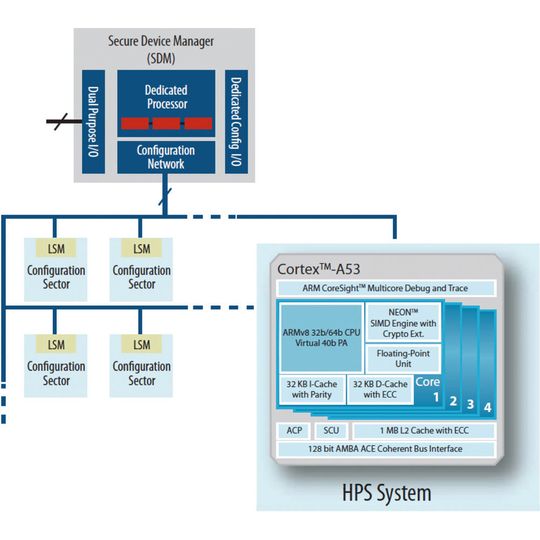

Eine Möglichkeit, die Sicherheitsfunktionen zu verwalten, ist das Erstellen eines Mikroprozessor-Blocks, der als Security Device Manager (SDM) dient. So lässt sich ein voll authentifiziertes Konfigurationsverfahren umsetzen, mit dem Entwickler die Gerätekonfiguration anpassen, alle Daten auf Null setzen (im Falle eines Sicherheitsverstoßes) und Schlüssel verwalten können.

Altera verwendet dieses Schema in seinen Stratix 10 SoC FPGAs. Aus Sicht der Systemkonfiguration ist der SDM der Eintrittspunkt für JTAG-Befehle. Im Stratix 10 SoC FPGA laufen die wesentlichen Sicherheitsfunktionen in einem Voting-Schaltkreis eines 3-fach redundanten Lock-Step-Mikroprozessors. Stimmen alle drei Prozessoren überein, ergibt sich eine inhärent sichere Implementierung.

Die drei Verschlüsselungsblöcke AES, SHA2 und ECDSA bieten die Möglichkeit, Verschlüsselung und Authentifizierung für alle Chipfunktionen bereitzustellen. Der Secure Hashing Algorithm (SHA) und der Elliptic Curve (ECDSA) Funktionsblock bieten einen mehrstufigen Ansatz für die Authentifizierung. Damit lassen sich mehrere Signaturen mit verschiedenen Schlüsseln auf sensiblen Datenblöcken anwenden.

Die Authentifizierungs- und Verschlüsselungsfunktionen werden durch die Physically Unclonable Function (PUF) ergänzt. In Alteras Stratix-Bausteine sind die PUF-Algorithmen als Befehlscode anstelle hardware-basierter PUF-Blöcke implementiert. Das von Intrinsic ID entwickelte PUF erzeugt einen völlig bausteinbezogenen, nicht klonbaren Schlüssel, den Entwickler für die Baustein-Authentifizierung und das Schlüssel-/Key-Wrapping verwenden können.

PUFs verwenden Zufallsmuster, um Bausteine voneinander zu unterscheiden. Intrinsic IDs Technik nutzt den einzigartigen Charakter der Sub-Micron-Prozessschwankungen innerhalb der FPGA-SRAM-Transistoren. Da bestehende FPGA-Blöcke verwendet werden, wird der verfügbare Platz für das Design nicht beeinträchtigt.

Das Prinzip hinter SRAM PUF ist, dass es die Start-up-Werte einer Reihe von SRAM-Zellen nutzt. Der Ausgangszustand jeder Zelle ist eine Funktion aus den Prozessschwankungen während der Fertigung, was den Zustand der SRAM-Zelle entweder auf Eins oder Null setzt. Diese Start-up-Werte sind aufgrund der Prozessschwankungen völlig zufällig und unmöglich zu kontrollieren.

Das resultierende SRAM-Muster und die PUF selbst sind somit nicht vorhersehbar und somit einzigartig. Da der Schlüssel abgeleitet und nicht dauerhaft gespeichert wird, ist die PUF eine äußerst sichere Art, einen Schlüssel zu erzeugen. Versucht ein Hacker, den Baustein auszulesen oder zu manipulieren, wäre dies völlig sinnlos.

(ID:43813520)

:quality(80)/p7i.vogel.de/wcms/37/ec/37ece4c276f37114e8f40696ff5dcd66/0130537789v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/46/7c/467c0afffbfd10c3553c2888a4a6289f/0130479810v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/12/3d/123d9eb2c2e4ce13296371a2ad3718a4/0130412664v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/e7/b6e755d9e704319c0bb59dc1ac2d67e8/0130537290v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/8b/10/8b10d1edceb749de99c1df3ad97be01e/0130564619v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ac/da/acda3bafe46d3bf8e104a2a7bc2ac557/0130535476v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ca/9b/ca9b681785123f9700518a46897f9779/0130428786v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/38/cb/38cbe19e814dd30b94780bc3946547ab/0130446533v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/88/c28805ea7b2261235475146a5b0c61f8/0130313028v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/8d/fa8dedee195f29c33c89d86311c258ee/0130104146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/7a/697a270ed7538378d1fbc0f0b240ed25/0130534691v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/e7/a4/e7a4e048491e60cb30e22a860f5d68bc/0130519425v4.jpeg)

:quality(80)/p7i.vogel.de/wcms/1b/f0/1bf02d41e3eac721823841a4c1228753/0130519149v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1a/53/1a539631c940d184689460600bd2b395/0130410666v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/10/45/1045969e69a1db4aaa73d0f74f55cc02/0129962687v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/e4/bae4e54395e5a53088060531ef99b814/0130359274v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/af/35af7dd326d198475d06fbb69aa600b5/0130175971v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/2e/c02e7bf72bfc434888c37100e2511681/0130127767v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/8c/42/8c4211320be4a5ef78ca36d37b2406f2/0130561321v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e1/0b/e10bc04827e33786548587e32bbae422/0130438700v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/06/3506f2a8d33a696aaef12a30771bd8d8/0130496747v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/ed/e5ed08c670c44565a9130e95a760dddc/0130494578v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/34/6d/346d110316228e54143f67e9f273972b/0130589338v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/7a/c07aaa9f6122aeb6faed4f2a74dcb77f/0130542642v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/3a/72/3a722ed2ad6ac4894c352e6ce87b6560/0130567207v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e9/19/e919aaa1fb20114acd7f56479d9d6c0d/0130599660v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1c/33/1c3399d0f7fb55bda7808310088accaf/0130565746v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/2e/95/2e9597b5dc1873771c7fe9c32ac41e82/0130549010v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/15/56/15564dea31861c376a385658c3b961a3/0130465243v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/67/d1/67d1a4da69c1f/b--rklin-logo-digital--002-.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/66/1f/661fa8e004810/heitec-logo-2024-1200px-ae.png)

:fill(fff,0)/p7i.vogel.de/companies/5f/15/5f157c2d880f4/ish-logo2020.jpg)

:quality(80)/p7i.vogel.de/vogelonline/bdb/981200/981248/original.jpg)

:quality(80)/p7i.vogel.de/vogelonline/bdb/981200/981250/original.jpg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/4a/e0/4ae0e2c46707c68597af9c5e1bc59696/0124937059v2.jpeg)