Anbieter zum Thema

Die Folgen von Datenversatz und Fehlbildern

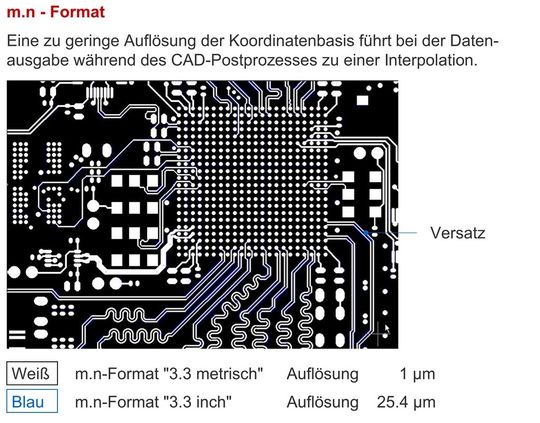

Bei einem m.n.-Format von "2.3in" beträgt die Interpolation von CAD-Daten +,- 12,7 µm. Das erscheint ein geringer Wert zu sein, der vernachlässigt werden kann. Schließlich hat das ja die letzten Jahrzehnte anstandslos funktioniert. Warum also jetzt diese Probleme ? Nun, inzwischen werden Layouts im Grenzbereich konstruiert. Leiterplatten und Baugruppen sind hochwertige Präzisionsprodukte geworden. Ein Versatz zwischen den Daten für die Bildbearbeitung und den Daten für die mechanische Bearbeitung führt heute nicht nur zu Toleranzen zwischen den Arbeitsschritten zur Fertigung der Leiterplatte. Es ergeben sich auch unnötige Toleranzen zwischen der Leiterplatte und der Produktion der Baugruppe. Sogar die physikalische Funktion der Baugruppe kann drastisch in Mitleidenschaft gezogen werden.

Das klassische Interpolation betrifft die Passung zwischen Bohrung (= Mechanik) und Pad (= Leiterbild). Für Vias sind die Restringe inzwischen bereits minimal konstruiert, um beim Layouten eine möglichst hohe Verdrahtungsdichte erreichen zu können. Ein durch den Postprozess des CAD-Systems bedingter Versatz zwischen Via-Bohrung und Pad kann fatale Folgen haben. Wird die fertigungstechnisch zulässige Toleranz während der Leiterplattenfertigung bereits in Anspruch genommen, dann führt der datenbedingte Versatz dazu, dass die Bohrung außerhalb des Pads liegt. Das entspricht einer Reduzierung des Sicherheitsabstandes zu benachbarten Strukturen von maximal 12,7 µm. Bei HDI-Layouts mit 100 µm Strukturabstand entspricht das einer Reduzierung von 12,7%. Weil die Interpolation benachbarter Strukturen gegenläufig sein kann ('links' wird aufgerundet und 'rechts' wird abgerundet), sind auch Abstandreduzierungen von bis zu 25,4 µm oder 25,4% möglich (Bild 3).

Der Begriff „benachbarte Strukturen“ ist eine allgemeine Formulierung. Das können auch parallel verlaufende Leiterbahnen sein. Bei einer gegenläufigen Interpolation durch Abrunden einerseits und Aufrunden andererseits können die Leiterbahnen unerwartet nah zusammenrücken. Für einen guten Leiterplattenhersteller mag das fertigungstechnisch keine Komplikation bedeuten. Ein ungewolltes und in der Funktionssimulation nicht vorgesehenes Übersprechen (Crosstalk) kann jedoch zur Folge haben, dass die bestückte Baugruppe nicht die stabile Funktionssicherheit bietet, die von der Anwendung benötigt wird und die vom Konstrukteur auch korrekt vorausberechnet wurde.

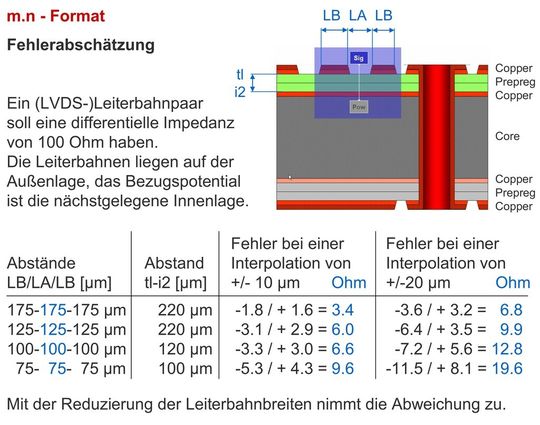

Dass keineswegs nur Leiterplatten und Baugruppen in MFT (MicroFinelineTechnology) betroffen sind, zeigt die Analyse des Einflusses einer möglichen Interpolation auf die Varianz des Impedanzwertes bei differentieller Signalübertragung. In der Tabelle von Bild 4 ist für einen Abstand von 175-175-175 (= Leiterbahn-Leiterbahnabstand-Leiterbahn) bei einer Interpolation von +,- 10 µm eine Impedanzabweichung von 3,4 Ohm zu erwarten. Wohlgemerkt, nur auf Grund der Daten des CAD-Systems, es ist also noch gar kein Fertigungsschritt durchgeführt worden.

Wagen wir einen Blick in die nahe Zukunft, dann zeigt die Tabelle, dass für die gezeigte Geometrie bei einem Abstand von 75-75-75 der Impedanzwert um bis zu 9,6 Ohm abweicht. Das entspricht der heute insgesamt zulässigen Abweichung, die sich durch reale Fertigungstoleranzen ergeben darf.

Liegt die Interpolation über +,- 10 µm, dann die Abweichung bereits über der realen Fertigungstoleranz und das Produkt wäre bereits unbrauchbar, noch bevor überhaupt das erste Loch gebohrt oder die erste Leiterbahn geätzt worden wäre.

Fazit: Die richtige Koordinatenauflösung muss vom CAD-System kommen. Prüfen Sie am CAD-System die Einstellungen für den Postprozess. Stellen Sie alle Ausgabeformate einheitlich auf metrisch ein. Die technisch umsetzbare Auflösung beträgt 1 µm. Das sinnvolle und ideale m.n.-Format ist dann also "3.3mm".

* Arnold Wiemers, Mitinhaber der LA-LeiterplattenAkademie GmbH, Berlin.

(ID:32672610)

:quality(80)/p7i.vogel.de/wcms/46/7c/467c0afffbfd10c3553c2888a4a6289f/0130479810v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/12/3d/123d9eb2c2e4ce13296371a2ad3718a4/0130412664v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d8/78/d878b7bfc23826e6ddfce42443836d28/0130384280v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/13/20/13208d1c2797edd67d9ff216b403726b/0130471595v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/38/cb/38cbe19e814dd30b94780bc3946547ab/0130446533v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a3/3e/a33e6d8a927d539ec6c3a0537f48f0f1/0130440028v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6b/61/6b61373f1c3f06f7f9343e6b0f0e9cc8/0130225062v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/15/93/1593dd152e6d58c5fc5da0d331777c54/0130357398v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/88/c28805ea7b2261235475146a5b0c61f8/0130313028v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/8d/fa8dedee195f29c33c89d86311c258ee/0130104146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cc/13/cc1378375499a26b5ddbb309d2155acb/0130085649v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6d/91/6d91abfa1b16ffcf470c7147facd7aa8/0130387695v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/85/b0/85b0b32128f6d1968e975043f1e0b67b/0130342166v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/1a/53/1a539631c940d184689460600bd2b395/0130410666v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/10/45/1045969e69a1db4aaa73d0f74f55cc02/0129962687v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c7/f6/c7f61d0437c7f8fca3c6ff947ba2ad62/0129322490v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/e4/bae4e54395e5a53088060531ef99b814/0130359274v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/af/35af7dd326d198475d06fbb69aa600b5/0130175971v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/2e/c02e7bf72bfc434888c37100e2511681/0130127767v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/7c/04/7c04916c305164fb10bc6cb05b51d934/0130431065v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/64/e5/64e5e333492f182ab7df5ab4c2b54c1e/0130463252v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/0a/95/0a95db4508128c4e11d5d268bf2c0a77/0130440053v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b3/65/b365dd5433c8b6d36c56c92b72f5b368/0130401081v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/85/c0/85c0cdd8fd326013aed52ca96777c998/0130426877v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f0/78/f07826d6c4e995980f1ada3377416aac/0130403626v4.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/c8/b6c8f7732da417bda3d298412f4c0ed8/0130453104v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/47/ce/47ce64bad7990f276f68cbb24505f6dd/0130472850v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/15/56/15564dea31861c376a385658c3b961a3/0130465243v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/98/ad/98ad595a6372aae8dbeac71681d23f41/0130450258v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bf/2a/bf2aad428ab1a80e6738fdbdc2efeb7e/0130453420v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/60/f6/60f6829670d63/beta-layout-logo.jpeg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/68800/68851/65.jpg)

:quality(80)/p7i.vogel.de/wcms/80/7b/807bc9dc4d65da8b9d67314d544b9e13/0128113873v4.jpeg)

:quality(80)/p7i.vogel.de/wcms/43/fe/43fef5f4f1ecffcc91680a16c26401cd/0127019959v2.jpeg)