Anbieter zum Thema

DSP-Spezialgebiet: Filterfunktionen

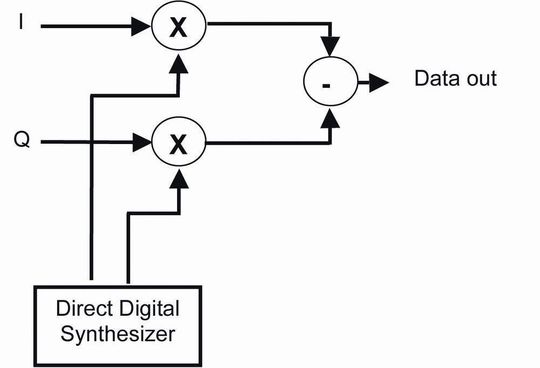

Viele Applikationen setzen Mixer für die Verschiebung der Frequenz eines Signals ein. Vom Konzept her könnte man zwar mit einem einzigen Multiplizierer auskommen, doch es hat mehrere Vorteile, die Zahlen in komplexer Form darzustellen. Meist erfolgt dies durch Repräsentation der Signale als I- und Q-Komponenten. Bild 4 zeigt einen Mixer, wie man ihn für die digitale Aufwärtswandlung verwenden würde.

Wie diese häufig vorkom-menden Funktionen illustrieren, bilden Multiplizierer, gefolgt von Addition, Subtraktion oder Akkumulation, den Kern der meisten DSP-Applikationen. DSP-Universalchips verbinden effiziente Implementierungen dieser Funktionen mit einem Mehrzweck-Mikroprozessor. Sie bestehen meist aus einem bis vier Multiplizierern. Der Prozessor sequenzialisiert die Daten und schickt sie durch die Multiplizier- und sonstigen Funktionen, wobei er die Zwischenergebnisse im Speicher oder in Akkumulatoren zwischenspeichert.

Die Geschwindigkeit lässt sich hauptsächlich durch Erhöhung der für die Multiplikation verwendeten Taktfrequenz steigern. Die typischen Taktfrequenzen liegen zwischen mehreren 10 MHz bis 1 GHz. Die in Millionen-Multiplizier-Akkumulationen (MMAC) pro Sekunde gemessene Geschwindigkeit liegt normalerweise zwischen 10 und 4000. Funktionen, die eine höhere Geschwindigkeit erfordern, müssen auf mehrere DSP-Module verteilt werden. Der Preis solcher Chips reicht von ein paar Dollar am unteren Ende des Leistungsspektrums bis zu mehreren Hundert Dollar im oberen Leistungsbereich. Der Vorteil bei diesem Ansatz ist die Möglichkeit, Algorithmen, die in einer problemorientierten Programmiersprache wie C geschrieben sind, direkt zu implementieren.

DSP-orientierte FPGAs

DSP-orientierte FPGAs bieten die Möglichkeit, auf dem Chip viele Funktionen parallel zu implementieren. Universell verwendbare Routing-, Logik- und Speicherressourcen werden verwendet, um die Funktionen zu verbinden, zusätzliche Funk-tionen auszuführen und Daten zu sequenzialisieren und, wenn nötig, zwischenzuspeichern. Einige elementarere Bausteine unterstützen nur das Multiplizieren, während alle anderen Funktionen in Logik konstruiert werden müssen. Anspruchsvollere Bausteine bieten Additions-, Subtraktions- und Akkumulatorfunktionen bereits als Bestandteil ihrer DSPs. FPGAs verfügen normlerweise über mehrere Dutzend Multiplizierelemente und arbeiten mit Taktfrequenzen von mehreren 100 MHz.

Mit den LatticeECP/EC-Bausteine können die Entwickler jetzt zwischen drei niedrigpreisigen FPGAs der aktuellen Generation wählen. Die Cyclone-FPGAs von Altera enthalten kein DSP-orientiertes Element, was es schwierig macht, größere DSP-Funktionen ohne erhebliche Beanspruchung der internen Ressourcen zu implementieren. Ebenso schwierig ist es auch, mit solchen Implementierungen hohe Leistungsfähigkeit zu erreichen. Allerdings wurde inzwischen Cyclone II angekündigt, der über eine Multiplizierfähigkeit verfügt. Die Spartan-3-Familie von Xilinx bietet elementare Multiplizierfähigkeiten. Das ist sicher besser, als ganz ohne DSP-Fähigkeit auskommen zu müssen, doch es müssen immer noch erhebliche FPGA-Ressourcen verbraucht werden, um die Addierer, Subtrahierer, Akkumulatoren und Pipeline-Register zu implementieren.

Der LatticeECP-DSP-Baustein wurde speziell für DSP-Applikationen konzipiert (Bild 5). Er besteht aus einer kostengünstigen FPGA-Struktur, verbunden mit vier bis zehn integrierten und optimierten sysDSP-Blöcken.

(ID:207530)

:quality(80)/p7i.vogel.de/wcms/37/ec/37ece4c276f37114e8f40696ff5dcd66/0130537789v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/46/7c/467c0afffbfd10c3553c2888a4a6289f/0130479810v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/12/3d/123d9eb2c2e4ce13296371a2ad3718a4/0130412664v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/e7/b6e755d9e704319c0bb59dc1ac2d67e8/0130537290v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/8b/10/8b10d1edceb749de99c1df3ad97be01e/0130564619v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ac/da/acda3bafe46d3bf8e104a2a7bc2ac557/0130535476v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ca/9b/ca9b681785123f9700518a46897f9779/0130428786v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/38/cb/38cbe19e814dd30b94780bc3946547ab/0130446533v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/88/c28805ea7b2261235475146a5b0c61f8/0130313028v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/8d/fa8dedee195f29c33c89d86311c258ee/0130104146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/7a/697a270ed7538378d1fbc0f0b240ed25/0130534691v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/e7/a4/e7a4e048491e60cb30e22a860f5d68bc/0130519425v4.jpeg)

:quality(80)/p7i.vogel.de/wcms/1b/f0/1bf02d41e3eac721823841a4c1228753/0130519149v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1a/53/1a539631c940d184689460600bd2b395/0130410666v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/10/45/1045969e69a1db4aaa73d0f74f55cc02/0129962687v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/e4/bae4e54395e5a53088060531ef99b814/0130359274v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/af/35af7dd326d198475d06fbb69aa600b5/0130175971v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/2e/c02e7bf72bfc434888c37100e2511681/0130127767v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/e1/0b/e10bc04827e33786548587e32bbae422/0130438700v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/06/3506f2a8d33a696aaef12a30771bd8d8/0130496747v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/ed/e5ed08c670c44565a9130e95a760dddc/0130494578v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ce/33/ce336bc438b912829effe8d4704dc159/0130480307v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/3a/72/3a722ed2ad6ac4894c352e6ce87b6560/0130567207v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e4/d1/e4d122a8ecce14b98c8298c1cc130194/0130561462v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/3c/55/3c5505dd3ca3971cddd09c583a4c907d/0130458429v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/47/ce/47ce64bad7990f276f68cbb24505f6dd/0130472850v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/2e/95/2e9597b5dc1873771c7fe9c32ac41e82/0130549010v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/15/56/15564dea31861c376a385658c3b961a3/0130465243v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bf/2a/bf2aad428ab1a80e6738fdbdc2efeb7e/0130453420v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/66/f6/66f673630a98a/logo-mc-rgb-300x300.png)

:fill(fff,0)/p7i.vogel.de/companies/66/1f/661fa8e004810/heitec-logo-2024-1200px-ae.png)

:fill(fff,0)/p7i.vogel.de/companies/5f/15/5f157c2d880f4/ish-logo2020.jpg)

:quality(80)/p7i.vogel.de/wcms/de/48/de48603453b0bd091cef84dbbefe37c1/0126851659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/16/f5/16f53e7661525c7f1c4db7a75de9cec1/0130519539v2.jpeg)