Referenzplattform für die Display-Ansteuerung Display-Controller auf FPGA-Basis implementieren

Um Entwicklern eine flexible, skalierbare und langzeitverfügbare Ansteuerung unterschiedlicher Display-Technologien zu ermöglichen, hat Sasco Holz gemeinsam mit RevisionOne Engineering die Systemreferenzplattform „PABLO“ entwickelt. Die Plattform macht sich programmierbare Logik zu Nutze und vereinfacht die Entwicklung und das Design von Display-Controllern.

Anbieter zum Thema

Auf dem Markt für Displays zeigen sich derzeit zwei grundlegende Trends: Zum einen nahm der Absatz von Displays (z.B. TFT-LCD) deutlich zu; zum anderen werden Displays von Jahr zu Jahr günstiger. Beide Entwicklungen verdeutlichen die Attraktivität dieses Marktes. Die TFT-LCD-Produktion wird von 1,2 Mrd. Stück im Jahr 2006 auf 2,5 Mrd. bis 2011 ansteigen, verlautete das Portal „Digitimes“.

Eine zentrale technische Herausforderung bei der Entwicklung von Display-Technologien ist deren flexible Ansteuerung. Eine Alternative zu den traditionell verwendeten Display-Controller-ASSPs bietet programmierbare Logik in Form von frei programmierbaren FPGAs. Als Grafik- und Display-Controller bieten sie größtmögliche Flexibilität bei der Anpassung an die unterschiedlichen Displaytechnologien, machen unabhängig von eventuellen Produktabkündigungen der ASSP-Lösungen und ermöglichen eine kosteneffiziente Entwicklung.

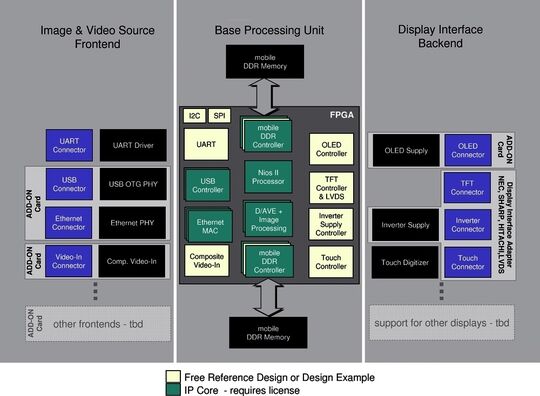

Gemeinsam mit RevisionOne Engineering hat der Distributor Sasco Holz die Referenzplattform PABLO konzipiert. Display-Anwendungen lassen sich damit einfacher und schneller entwickeln. Die Plattform umfasst Hardware (Basis-Board, zusätzliche Eingangs-Boards und verschiedene Display-Adapter), Beispiele von IP-Cores, die Unterlagen zum PABLO-Hardware-Referenzdesign und Applikationsbeispiele.

Schneller und einfacher entwickeln

Damit können Anwender FPGA-basierte Display-Controller-Lösungen in ihre Anwendungen integrieren – von kleinformatigen OLEDs über große TFT-Displays bis hin zu neuesten Dual-View-Displays. Bei PABLO greift Sasco Holz auf Bausteine und Lösungen von Altera, Analog Devices, ASTEC, IDT, Linear Technology, Micrel, Microchip, Osram und Tyco Electronics zurück. Die verfügbaren IP-Cores und Referenzdesigns stammen von Altera, Arrow, MaCo-Engineering, RevisionOne Engineering und TES.

Die Entwicklungskosten im Blick, sehen sich Entwickler einer Vielzahl von Technologie-Anwendungen gegenüber, darunter zahlreiche Steuerungslösungen, ausgehend von einfachen softwarebasierten Display-Controllern bis hin zu Prozessoren mit integrierten Grafikfunktionalitäten bzw. von Grafik-ICs und vollwertigen PC-Grafikkarten.

Die Möglichkeiten sind vielfältig und führen häufig zu einer Vielzahl von firmeninternen Insellösungen, die sich nur mit großem Aufwand zusammenführen lassen. Dagegen lässt eine skalierbare Plattform auf Basis intelligenter FPGA-Architekturen mit der Integration von Grafik-Controllern und Display-Schnittstellen herkömmliche Controller- und ASSP-Lösungen hinter sich. Einfache Display-Timing-Anpassungen lassen sich damit ebenso realisieren wie komplexere Video- und Bildverarbeitungssysteme.

Eine weitere Herausforderung für Entwickler ist die Tatsache, dass es noch keine einheitliche Schnittstelle für die Anbindung von Display-Panels gibt, um Displays führender Hersteller zu unterstützen. Die Entwickler von PABLO lösten dieses Problem mit Cross-Adaptern. Diese passen die an die Displays gesendeten Signale und Versorgungsspannungen des Boards an. Derzeit kann eine große Auswahl an Displays mit unterschiedlichen Auflösungen und Größen mit LVDS- oder paralleler Schnittstelle unterstützt werden.

Basis-Board mit Cyclone-II-FPGA

Kern des PABLO-Basis-Boards sind ein Cyclone-II-FPGA von Altera (EP2C20F484C6N) und zwei Mobile-DDR-SDRAM-Speicher für die Bildspeicherung. Weitere Bestandteile sind Kommunikations- und Kontrollschnittstellen, Erweiterungen für zusätzliche Add-On-Karten, ein Touch Digitizer von Analog Devices und eine Stromversorgungseinheit von Linear Technology.

Die Mobile-DDR-SDRAM-Technologie ermöglicht eine hohe Speicherbandbreite bei reduzierter Leistungsaufnahme und einfacher Anbindung. Die hohe Skalierbarkeit des Basis-Boards ergibt sich aus der Kombination von externem Speicher (als Frame Buffer verwendbar) und den FPGA-internen 20.000 Logikelementen und Speicherblöcken (als Line Buffer verwendbar).

Zudem sind die I/O-Pins zur Display-Schnittstelle konfigurierbar als LVDS-Schnittstelle mit 2,5 V Spannungspegel oder als parallele 3,3-V-Schnittstelle. Die Schnittstellen dienen auch der direkten Ansteuerung der Displays, z.B. über einen externen Host-Prozessor. Vier konfigurierbare Status-LEDs, Push-Buttons und ein Tactile Switch (Joystick) ermöglichen dem Anwender direkte Einflussnahme.

Das Basis-Board bietet zwei Steckplätze im Altera-Santa-Cruz-Format, über die die Plattform mit zusätzlichen Hardwarefunktionen erweitert werden kann. Eine Composite-In-Karte speist analoge Video- und Bilddaten von DVD-Spielern, Überwachungskameras oder anderen Quellen ein, eine andere Hardwarekarte bietet eine DVI-Schnittstelle als Bilddateneingangsquelle. Eine Vielzahl anderer Erweiterungsmöglichkeiten ist über Drittanbieter gegeben.

Designbeispiele für Testzwecke

Das PABLO-Basis-Board ist mit Design-Beispielen ausgestattet, so dass Anwender zunächst einmal die Funktionalitäten des Boards testen können. Um verschiedene Displays ansteuern zu können, verfügt ein Designbeispiel über einen TFT & Timing Controller in verschiedenen Ausführungen, mit einem Output von 18 Bit RGB oder LVDS. Der Mobile-DDR-SDRAM-Controller wurde hinsichtlich der Speicherbandbreite so optimiert, dass ein hoher Durchsatz an Videodaten möglich ist.

Alternativ lassen sich der Alteras DDR-SDRAM-IP-Core und der Multiport-SDRAM-Controller von Microtronix für diesen Zweck einsetzen, was die flexiblen Einsatzmöglichkeiten unterstreicht. Da es Displays mit speziellen Anforderungen gibt, verfügt das Board zudem über verschiedene Wandler- und Display-Steuerungsfunktionen. Auf diese Weise kann der Entwickler schnell in die Thematik FPGA-basierter Display- und Grafik-Controller einsteigen. Die Designpartner von Sasco Holz stehen bei weiteren, individuellen Anforderungen zur Verfügung.

FPGAs bieten bei Display-Anwendungen zahlreiche Vorteile: Die digitalen I/Os können standardmäßig als „single-ended“ konfiguriert werden, aber auch als LVDS-Pins. Damit adressiert das FPGA digitale CMOS-Schnittstellen mit 3 × 6 Bit RGB und LVDS-Schnittstellen, die bis zu 640 MBit/s bieten.

Die jeweiligen Timing-Anforderungen lassen sich mit den logischen Elementen des FPGA abdecken. Die logischen Elemente werden mit den internen Speicherblöcken kombiniert, um Grafik-Funktionalitäten zu realisieren. Integrierte Hardware-Multiplizierer sorgen für zusätzliche DSP-Funktionalität und Performance für die Bildverarbeitung.

Kostenlose FPGA-Entwicklungsumgebung

Kombiniert mit den logischen Elementen lassen sie sich zu leistungsfähigen Videoverarbeitungs-Subsystemen ausbauen. Die externe Anbindung jeglicher Speichermodule und die flexible Pin-Migration ermöglicht Projekte jeder Größe. Hilfreich ist dabei die Software Quartus II Web Edition, eine kostenlose Entwicklungsumgebung von Altera, die Tools auf Systemebene für das Design der Display-Anwendungen bereithält. In wenigen Minuten ist es möglich, mithilfe der Tools SOPC Builder und C2H, komplexe Systeme zu erstellen.

*Klaus Maier ist Marketing Director bei Sasco Holz in Putzbrunn bei München.

(ID:240412)

:quality(80)/p7i.vogel.de/wcms/e9/ce/e9ce137e87eccac328ec5504c586c477/0129711019v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/68/46/684697b6eb687384e0d8c6803450401a/0130056395v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/0f/c0/0fc0d93c99a5d9066e58c39f41fb1b10/0130046764v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6a/42/6a423ced6604acf7d3eef8e4c0c2bd39/0130317237v4.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/60/fa6016fc48ac8609a451038ca38b0eca/0130241261v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/57/97/5797ffe4c6e19cf02aa75a7f742598b3/0130160607v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a2/31/a2319b6d6b473424b275f6489bbce348/0130213768v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fb/d3/fbd33264fcdf128866667be0a0a6b657/0130137877v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/8d/fa8dedee195f29c33c89d86311c258ee/0130104146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cc/13/cc1378375499a26b5ddbb309d2155acb/0130085649v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/24/58/2458f1cae3100e375fbb8124f02c54af/0130111244v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/6d/f0/6df06a1488ceb6357c287fee993fad65/0130161592v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/65/f4/65f404dc6d19d4f1628ad7e49f6a22cf/0130136276v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/fc/fafc300481de3fd4d7f34400327d0d01/0130127049v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/10/45/1045969e69a1db4aaa73d0f74f55cc02/0129962687v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c7/f6/c7f61d0437c7f8fca3c6ff947ba2ad62/0129322490v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/66/0c/660c31afa35398bac9be42f2be73fdc4/0129073529v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/af/35af7dd326d198475d06fbb69aa600b5/0130175971v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/2e/c02e7bf72bfc434888c37100e2511681/0130127767v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/95/a1/95a197490145b7afcfd4dc176a1b5ef9/0130096114v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ac/31/ac31fbd47f85c24ae7d13a73555c85e6/0130236430v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ef/a0/efa0d8af7bcf1d64636b877a04b853d9/0130136738v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bf/82/bf82f81061b759c454e15ec4c2e7560b/0130110139v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/74/96/74964a7715c738a9e8b17681445ceed3/0130103633v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f1/58/f158a1c680219c67cff9c099186ab50d/siemens-20ubtech-20hmnd-1920x1079v1.png)

:quality(80)/p7i.vogel.de/wcms/6a/93/6a93991941467231d8798c8577882dfd/0130071573v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/19/31/193191c71275b1f480fff0e5827be766/0130211045v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d1/d1/d1d103805ed7ac0df7feda4c46522b8c/0130164847v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/68/7e/687ebf75f8024edeec7ebd6d3582327f/0130240314v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/68/7f/687fac7d01bdb/ag-2024-logo-4c.png)

:fill(fff,0)/p7i.vogel.de/companies/66/1f/661fa8e004810/heitec-logo-2024-1200px-ae.png)

:fill(fff,0)/p7i.vogel.de/companies/60/37/6037a859ec501/dmb-rgb-quadrat-online.jpg)

:quality(80)/p7i.vogel.de/wcms/88/0b/880b1539aba182d2b26dc2b5a3f0541e/0125283151v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/68/fe/68fe4eae41615d24a3485bf72dbdeb4a/0129696639v2.jpeg)