Anbieter zum Thema

Ein konkretes Schaltungsbeispiel

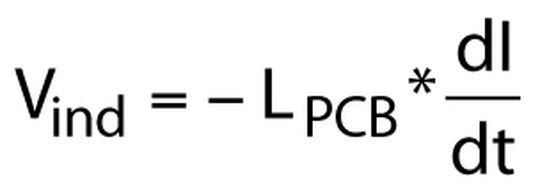

Das folgende Beispiel verdeutlicht die Auswirkung hoher Schaltgeschwindigkeiten: 10 mm Leiterbahn entsprechen rund 10 nH Induktivität. Ein Schaltvorgang mit einer Stromsteilheit von 1000 A/µs verursacht also einen Spannungsabfall von 10 V auf diesem kurzen 10 mm langen Leiterbahnabschnitt (allerdings nur während des Schaltvorgangs). Formel 1 zeigt den Zusammenhang.

Bei diesen hohen Schaltgeschwindigkeiten muss das Layout sehr sorgfältig ausgelegt werden. Hierfür müssen sternförmige Masseführungen eingeplant werden, um den Einfluss dieser kurzer Spannungsspitzen auf sensible analoge Schaltungsteile zu minimieren. Zudem bewirken diese Spannungsspitzen symmetrische EMV-Störungen, die durch die Verwendung eines Eingangsfilters mit hinreichend hoher Dämpfung im entsprechenden Frequenzbereich zu filtern sind. Die kritischen Elemente stellen hier alle parasitären Kapazitäten und die Serieninduktivitäten dar, die am Lade- und Entladevorgang der Ausgangskapazitäten der Schalter beteiligt sind.

Dieser Lade- und Entladestrom während des Schaltvorgangs wird durch Formel 2 definiert.

Resonanzkreis und Spitzenspannung

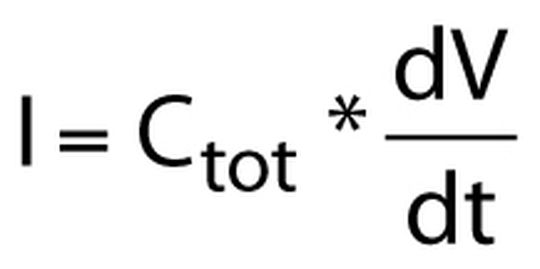

Die Kombination parasitärer Induktivitäten und Kapazitäten bilden einen Resonanzkreis. Die Energie schwingt zwischen den kapazitiven und induktiven Elementen in der Resonanzfrequenz hin und her (Formel 3).

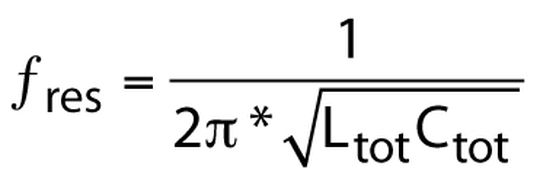

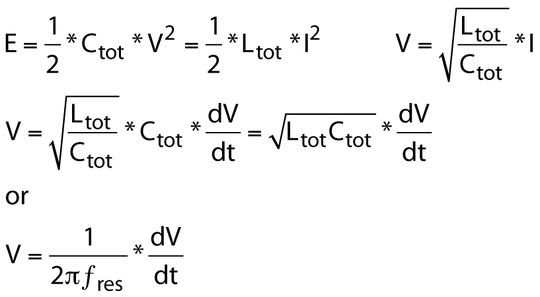

Der Spitzenwert der Überschwinger kann durch den Vergleich der Energieformeln (Formel 4) bestimmt werden:

V = Vpeak stellt die Amplitude der Störung dar, fres ist die Frequenz der Überschwinger und dV/dt die Steilheit der Spannungsänderung während des Schaltvorgangs. Die parasitären Kapazitäten und Induktivitäten beeinflussen demnach die Störungen. Werden diese Parameter reduziert, erhöht sich die Frequenz und folglich verringert sich auch die Spitzenspannung.

Die Reduzierung der Schaltgeschwindigkeit verringert ebenfalls die Funkentstörpegel, allerdings mit dem unerwünschten Effekt steigender Schaltverluste. Bei zu hoher EMI ist die Reduzierung der dV/dt oftmals trotzdem die einzige Problemlösung. Diese Reduzierung wird durch Erhöhung des Gate-Widerstandes RG erzielt.

Schalter mit Sicherheitsreserve

Den Hauptanteil der Kapazitäten Ctot bilden die Ausgangskapazitäten der Schalter. Sobald ein Schalter ausgewählt und eine hohe dV/dt eingestellt wurde, um die Schaltverluste zu minimieren, ist der weitere zu berücksichtigende Aspekt das Layout: Reduzieren der Serieninduktivitäten der Leiterbahnen und vorhandener parasitärer Kapazitäten. Diese Kapazitäten könnten in den Windungen der induktiven Bauelemente oder in der Kopplung der Transistoren zum geerdeten Kühlkörper versteckt sein. Die Serieninduktivität wird durch Länge und Breite der Leiterbahn bestimmt.

Leider ist aufgrund der erforderlichen Kühlkörpermontage und der vorgegebenen Größe der Komponenten eine bestimmte Länge der Leiterbahnen festgelegt. Werden die IGBTs und die Kondensatoren (die den Strom während der kurzen Schaltzeiten liefern) sorgfältig plaziert, ist es dennoch möglich, die Induktivität des Layouts um mehrere nH zu verringern.

Ein letzter zu berücksichtigender Punkt ist die Möglichkeit, etwas größere Überschwinger am Schalter zuzulassen. Beispielsweise bietet der Einsatz eines 650-V-Schalters, wie des FGH40N65UFD anstelle des FGH40N60UFD, eine höhere Sicherheitsreserve insbesondere beim Auftreten der Überschwinger. Zusätzliche Vorteile stellen die höhere Sicherheitsreserven bei niedrigeren Temperaturen dar, wo die Durchbruchspannungen der IGBTs oder der MOSFETs zurückgehen. Desweiteren wird die Zuverlässigkeit der der Schalter und damit verbunden auch der Applikation durch die Durchbruchspannung von 650 V signifikant erhöht.

*Peter Haaf ist Technical Marketing Manager bei Fairchild, Böblingen.

(ID:321896)

:quality(80)/p7i.vogel.de/wcms/9f/13/9f13686bb894142875a93de7f6c3aabe/0131278942v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e1/9c/e19ca48e7ee7b6604240bdb1a02a3a7d/0131251245v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/8c/f0/8cf0a380137d81e18ab1683a061b7531/0131171547v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/8c/87/8c87c3a5ca9b98a84775dd79fc0e3261/0131341947v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/0f/3e/0f3e4cfa27ea41173ebece10fa1b6128/0131337152v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/40/00/4000cee04363c2ad502a5cfadded2e0e/0131287222v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/b9/c2b94412f90cbea098c5b0a49e93e3f7/0131368512v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/17/71/1771c0b139e32eced60c0f60abd045dc/0131202175v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ab/6e/ab6ee4358adb3ef565a3af4e923dae6b/0131202314v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/4e/a8/4ea857349b0630ab44c1ed52a2b8ea67/0131332364v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a0/b7/a0b74e201c3d9a12af0a204e1e578aad/0131136338v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d2/1c/d21cea8a73c1dc8b94322e896fb7cc2b/0131036508v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/5b/f2/5bf2fc2e46775b70614326a4003940ea/0131238162v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/58/ed/58ede6960020a2ded5f6771bd9b8e49d/0131277913v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/2e/78/2e789ef76c84f5fcdf02b5697a22f9ab/0131062677v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d4/1d/d41d81ec84a42b4fd5d732d36d0021ce/0130877962v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9c/79/9c798ab2b4c18ba0a2c24f2491798d36/0130550888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/e7/b6e755d9e704319c0bb59dc1ac2d67e8/0130537290v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a9/3f/a93f4dac41be6ba50eb634f5e4e7f7b7/0131355751v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/aa/79/aa79a807ba1ce61e6656226679e05f9c/0131288690v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/34/1f/341f0c9b899c7509a01c9a13383af6cf/0131148001v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/c2/35c2b1da065361aefeea668c786531c9/0131280558v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/05/83/0583267ea76f0beb94c4acef52d485e1/0130855074v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b5/54/b5548923d20a751319550a3eb159af21/0131159519v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/87/b6/87b60368567da3c6b65107c55f5f69ec/0130689118v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/7d/5b/7d5bd7b3575dd8745fac17cf8619a7c2/0131253052v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/48/51/48516b200b1181bdca44488163b1aeb7/0131056202v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/fc/fafc9d7589391638461f0a7647e03154/0131317785v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/94/82/948296f1541e8d3b2060978cfeae90e8/0131311058v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/3c/c9/3cc901afed76679636db88f3c6f6ed8a/0131354452v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/93300/93330/65.jpg)

:fill(fff,0)/p7i.vogel.de/companies/60/b6/60b601af20368/et-system-logo-rgb.png)

:fill(fff,0)/p7i.vogel.de/companies/62/16/621651a93b1ef/logo-we-rgb-pos.png)

:quality(80)/p7i.vogel.de/wcms/86/5b/865b2cba53325ffc9471e690a10b5d42/0129696419v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/3c/88/3c8863ad57e80adc0acb9c9d9ea30351/0129319571v2.jpeg)