Die Flip-Chip-Montage von morgen Copper Pillar Bumps ersetzen herkömmliche Solder Bumps

Von Advanpack Solutions in Singapur, Spezialist für Wafer Level Bumping und mehrfacher Patentinhaber, stammt die Idee für Flip-Chip-Kontaktierung der Zukunft: zylinderförmige Anschlüsse aus Kupfer mit einer Kappe aus Lot – Copper Pillar Bumps – ersetzen die herkömmlichen Solder Ball Bumps. Das Ergebnis: verbesserte elektrische und thermische Eigenschaften der Anschlüsse, höhere Anschlussdichte durch die schlanken Kontaktierungen und RoHS-Konformität. Die Fertigung ist mit dem Standardprozess beim Wafer-Level-Bumping vergleichbar und auch aus Kostensicht interessant.

Anbieter zum Thema

Eine innovative Chiptechnologie allein reicht nicht aus, um ein Produkt erfolgreich am Markt zu etablieren. Ebenso wichtig ist eine fortschrittliche Gehäuse- und Verarbeitungs-technologie, welche die Leistungsfähigkeit des IC nicht einschränken darf.

Die Flip-Chip-Technik hält mit der steigenden Anschlussdichte der ICs Schritt und ist in der Lage, die Performance der Halbleiter auf die Leiterplatte zu übertragen (siehe unten). Bei immer kleiner werdendem Abstand der Anschlüsse zueinander (Pitch) stößt die Flip-Chip-Technik mit Solder Ball Bumps zwangsläufig an ihre technischen Grenzen.

Der Grund ist die Kugelgeometrie der Bumps. Dieser Herausforderung hat sich der in Singapur ansässige Spezialist für das Wafer-Level-Bumping Advanpack Solutions Pte. Ltd. (APS) gestellt. Die Aufgabe lautet, ein IC-Package entwickeln, das den technologischen Herausforderungen der Zukunft hinsichtlich verbesserter elektrischer und thermischer Eigenschaften sowie hoher Zuverlässigkeit bei optimiertem Preis-Leistungs-Verhältnis gerecht wird. Die Lösung heißt Copper Pillar. Bei dieser patentierten Kontakttechnologie für die Flip-Chip-Montage von APS fungieren spezielle Kupferanschlüsse mit einem Lotdepot anstatt der üblichen Solder Ball Bumps als Verbindungselement zwischen Halbleiter und Substrat.

Überlegen in den elektrischen und thermischen Eigenschaften

Überlegen in den elektrischen und thermischen Eigenschaften

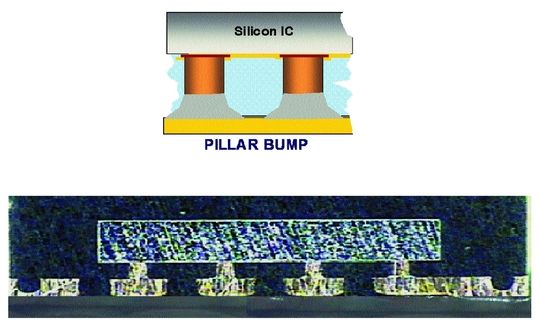

Der Copper Pillar Bump besteht aus zwei Elementen: dem ca. 60 bis 70 µm hohen Zylinder aus Kupfer sowie einer kleinen Kappe aus Lot. Hierbei kann eutektisches Zinn-Blei-Lot oder eine bleifreie Legierung mit hohem Zinnanteil zum Einsatz kommen. Während die Lotkappe lediglich die mechanische Verbindung zwischen IC und Verdrahtungsträger oder Leiterplatte herstellt, stellt der Kupfer-Pillar den elektrischen Kontakt her.

Zum Vergleich: Der konventionelle Solder Ball Bump fungiert gleichermaßen als mechanische und elektrische Verbindung. Gegenüber der Lotkugel bietet der Copper Pillar noch einen Vorteil: Der Pillar Bump ist trotz gleicher Höhe schmaler als der kugelförmige Solder Ball Bump. Damit ermöglicht die Copper-Pillar-Bump-Geometrie nicht nur ein feineres Anschlussraster, die schlanken Anschlüsse verbessern die elektrischen Eigenschaften des Anschlusses, während sich aufgrund des hohen Kupferanteils das thermische Verhalten verbessert (höhere Leitfähigkeit). Der Pillar Bump kann zudem unterschiedlich geformt werden, um die bei bestimmten Halbleitern auftretenden Probleme der steigenden Spannung und Wärmeentwicklung zu lösen.

Gleich bleibende Qualität im Fertigungsprozess

Gleich bleibende Qualität im Fertigungsprozess

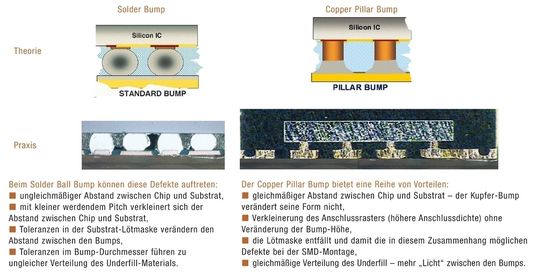

Im konventionellen Solder-Bump-Prozess verformen sich die Lotkugeln beim Umschmelzen und beim Reflow-Löten auf das Substrat oder die Leiterplatte. Die Folge ist ein ungleicher Abstand wischen den Bumps, der sich schwer kontrollieren lässt. Bei der Chip-Montage fließt der Underfill zwischen IC und Substrat vorrangig in die größeren Lücken zwischen den Solder Balls und lässt kleinere aus. Die daraus resultierenden Hohlräume beeinträchtigen die Zuverlässigkeit des Bauteils.

Beim Copper Pillar Bump ist die Verformung der Anschlüsse aufgrund der wesentlich geringeren Lotmenge viel kleiner. Zudem behält der zylindrische Kupferteil seine Form im Umschmelz- und Reflow-Prozess bei. Die gleichmäßigen Abstände zwischen den Bumps bedeuten weniger Hohlräume nach dem Underfill-Prozess und eine höhere Verarbeitungsqualität und Bauteilzuverlässigkeit.

Die Copper-Pillar-Technologie eignet sich gleichermaßen als Flip Chip in Package in den bekannten Standardgehäusen CSP, QFN, SOT, TO-220 usw. und als Flip Chip on Board. Die neuartige Chip-Kontaktierung trägt dazu bei, die elektrischen und thermischen Eigenschaften des IC und somit die Zuverlässigkeit zu verbessern.

Die Pillar Bumps lassen sich flexibel auf dem Die platzieren. Vorteil: Das löst Designprobleme und eröffnet neue Möglichkeiten beim IC-Design. Eine Möglichkeit, ist die strategische Positionierung der Pillar Bumps an Hotspots, um die Verlustwärme vom Chip gezielt abzuleiten. Darüber hinaus lassen sich die neuen schmalen Kontakte enger positionieren und somit noch höhere Anschlussdichten realisieren.

Ein weiterer Vorteil ist die RoHS-Konformität der neuen Kontakte: Kupfer fällt nicht in das Stoffverbot der RoHS und für die Lotkappe ist bleifreies Lot ge-eignet. Im Test haben sich Copper Pillar Bumps mit Reinzinn bewährt.

Eine echte Alternative zum Draht-Bonden

Das QFN-Package mit Cu-Pillar-Bumps ist spezifiziert für MSL 1 (85%RH/85°C) bis 5000 Temperaturzyklen für Temperaturzyklus B (-55 bis 125°C) und 1000 h HTST (Hot Temperature Storage Test).

Auch der Chip-On-Board-Montage macht die Copper-Pillar-Technologie ernsthaft Konkurrenz. Im Vergleich zum Bonddraht verbessert sich beim Copper Pillar Bump die Wärmeableitung vom Chip zum Substrat und der kürzere Signalpfad hat geringere Signalverzerrungen zur Folge. Hinzu kommt die kleinere Leiterplattenfläche. Langfristig und insbesondere bei hohen Volumen rechne sich der Bump-Prozess im Vergleich zur Wire-Bond-Technik, glauben die Experten.

Patentiert von Advanpack Solutions in Singapur

Die 1997 gegründete Advanpack Solutions Pte. Ltd. (APS) ist ein Tochterunternehmen der Advanced Systems Automation Limited (ASA) Singapur mit 50 Mitarbeitern. Das auf Wafer-Level-Packaging spezialisierte Unternehmen verfügt über viele Patente und fertigt Prototypen und Kleinserien. Für die Großserienfertigung hat der Packaging-Experte Jointventures mit UNISEM Malaysia (UAT) und JCAP China gegründet. Advanpack Solutions wird Europa von Ernst-A. Weissbach von der Firma HTC-Consulting vertreten.

APS bietet folgende Wafer-Bumping-Verfahren an:

- Solder-Bump-Technologie (eutektisches Zinn-Blei-Lot, bleifreies Lot),

- Gold-Bump-Technologie (TOP, COG),

- Pillar-Bump-Technologie (eutektisches Zinn-Blei-Lot, bleifreies Lot).

- Die Pillar-Bump-Technik realisiert APS bereits für namhafte Unternehmen.

- Typische Anwendungen sind:

- Fine-Pitch-ICs in extrem kleinen Gehäuseformen für Speicher, Hörgeräte und RFID-Lösungen,

- Power MOSFETS, die einen niedrigeren Widerstand und zugleich eine gute thermische Leitfähigkeit voraussetzen sowie

- Vorverstärker und RF-Module, bei denen gute thermische Leitfähigkeit und hohe Arbeitsgeschwindigkeiten erforderlich sind.

Der Copper-Pillar-Prozess ist qualifiziert und APS stellt entsprechende Zuverlässigkeitsdaten zur Verfügung.

Flip Chip: Im CSP oder BGA von außen nicht erkennbar

Bei der Flip-Chip-Montage wird der Die mit der strukturierten Seite nach unten auf den Schaltungsträger montiert (engl. flipped). Kontakthöcker (Bumps) aus Lot, die im Reflow-Prozess aufschmelzen, stellen die mechanische und elektrische Verbindung zwischen Chip und Trägersubstrat her. Vorteil: Bumps sind kürzer als Bonddrähte und haben einen größeren Durchmesser, was geringere induktive und kapazitive Beiträge der Bump-Verbindungen zur Folge hat.

Die Flip-Chip-Montage bietet im Vergleich zur Bondverbindung aber nicht nur kürzere Anschlüsse, sondern sie ermöglicht auch eine direkte Platzierung des Chips in der zugehörigen elektrischen Umgebung, das bedeutet Einsparung an Leitungslänge und verringert die parasitäre Wirkung weiter. Die Bump-Verbindungen lassen sich zudem mit hoher Reproduzierbarkeit herstellen, was das Verhalten des elektrischen Übergangs mit guter Genauigkeit vorhersagbar macht.

Die Flip-Chip-Montage auf der Leiterplatte (Flip Chip on Board) ist das Gebiet von Spezialisten, welche die empfindlichen Dice unter Reinraumbedingungen verarbeiten können und den anspruchsvollen Underfill-Prozess und das Aushärten beherrschen. Für Massenanwendungen prädestiniert ist das Flip Chip in Package, wobei der Flip Chip in BGA- oder CSP-Gehäusen untergebracht ist. Damit steht ein vollgeprüftes SMD-Bauelement zur Verfügung, das sich mit Standard-Equipment und -Prozessen verarbeiten lässt, während der IC in seinen elektrischen Eigenschaften anähernd die Performance des Flip Chip erreicht

(ID:242644)

:quality(80)/p7i.vogel.de/wcms/37/ec/37ece4c276f37114e8f40696ff5dcd66/0130537789v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/46/7c/467c0afffbfd10c3553c2888a4a6289f/0130479810v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/12/3d/123d9eb2c2e4ce13296371a2ad3718a4/0130412664v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/e7/b6e755d9e704319c0bb59dc1ac2d67e8/0130537290v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/8b/10/8b10d1edceb749de99c1df3ad97be01e/0130564619v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ac/da/acda3bafe46d3bf8e104a2a7bc2ac557/0130535476v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ca/9b/ca9b681785123f9700518a46897f9779/0130428786v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/38/cb/38cbe19e814dd30b94780bc3946547ab/0130446533v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/88/c28805ea7b2261235475146a5b0c61f8/0130313028v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/8d/fa8dedee195f29c33c89d86311c258ee/0130104146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/7a/697a270ed7538378d1fbc0f0b240ed25/0130534691v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/e7/a4/e7a4e048491e60cb30e22a860f5d68bc/0130519425v4.jpeg)

:quality(80)/p7i.vogel.de/wcms/1b/f0/1bf02d41e3eac721823841a4c1228753/0130519149v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1a/53/1a539631c940d184689460600bd2b395/0130410666v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/10/45/1045969e69a1db4aaa73d0f74f55cc02/0129962687v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/e4/bae4e54395e5a53088060531ef99b814/0130359274v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/af/35af7dd326d198475d06fbb69aa600b5/0130175971v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/2e/c02e7bf72bfc434888c37100e2511681/0130127767v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/e1/0b/e10bc04827e33786548587e32bbae422/0130438700v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/06/3506f2a8d33a696aaef12a30771bd8d8/0130496747v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/ed/e5ed08c670c44565a9130e95a760dddc/0130494578v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ce/33/ce336bc438b912829effe8d4704dc159/0130480307v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/3a/72/3a722ed2ad6ac4894c352e6ce87b6560/0130567207v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e4/d1/e4d122a8ecce14b98c8298c1cc130194/0130561462v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/3c/55/3c5505dd3ca3971cddd09c583a4c907d/0130458429v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/47/ce/47ce64bad7990f276f68cbb24505f6dd/0130472850v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/2e/95/2e9597b5dc1873771c7fe9c32ac41e82/0130549010v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/15/56/15564dea31861c376a385658c3b961a3/0130465243v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bf/2a/bf2aad428ab1a80e6738fdbdc2efeb7e/0130453420v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/60/81/6081635146580/odu-logo-ohne-rgb.jpg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/76800/76895/65.jpg)

:fill(fff,0)/p7i.vogel.de/companies/64/21/64219ce08bf52/logo.jpeg)

:quality(80)/p7i.vogel.de/wcms/e9/ce/e9ce137e87eccac328ec5504c586c477/0129711019v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/b9/b4/b9b48e164a8adfc48d941f0d06eb8e31/0128873058v2.jpeg)