Boundary-Scan-Verfahren Wie sich hochintegrierte Baugruppen kostengünstig testen lassen

Im ersten Teil zeigen wir elektrische Testverfahren mit Schwerpunkt auf Boundary-Scan und einen neuen, kostengünstigen Ansatz zum Einstieg in die Thematik.

Anbieter zum Thema

Die Miniaturisierung moderner Baugruppen nimmt ständig zu. Dabei enthalten diese immer mehr hochintegrierte Bauteile, die große Teile der Leiterplatte verdecken, was ein klassisches Testen in bestücktem Zustand mit traditionellen Testmethoden verteuert, erschwert oder gänzlich unmöglich macht.

Meist kann der Entwickler davon ausgehen, von seinem Leiterplattenlieferanten fehlerfrei gefertigte Leerplatinen erhalten zu haben. Wenn die bestückte Platine bei der Inbetriebnahme gar nicht oder zumindest nicht so wie erwartet funktioniert stellt sich die Frage: Woran liegt es? Handelt es sich um einen Design- oder einen Fertigungsfehler?

An Fehlermöglichkeiten gibt es in der Fertigung bekanntlich viele: fehlende oder mangelhafte elektrische Verbindungen durch schadhafte Lötstellen oder beschädigte Leiterbahnen, Kurzschlüsse durch Lotbrücken, defekte oder falsch bestückte Bauteile, um nur die häufigsten Probleme zu nennen.

Ein Überblick über die verschiedenen Testverfahren

In der Praxis haben sich über die Jahrzehnte viele Testverfahren etabliert, von denen jedes einzelne seine Stärken und Schwächen hat. Eine vollständige Testabdeckung erhält man grundsätzlich nur durch die Kombination mehrerer Verfahren. Aber ist dies auch immer sinnvoll, nötig und bezahlbar?

Es gilt, einen optimalen Kompromiss zu finden und gleichzeitig Ausschuss und Testkosten zu minimieren. Die speziellen Anforderungen des einzelnen Projektes und dieser Kompromiss beeinflussen hierbei die Auswahl des jeweiligen (elektrischen) Testverfahrens.

Bildgebende Verfahren wie AOI, der Automatisierten Optischen Inspektion, und Röntgen liefern alleine keine hinreichenden Ergebnisse, sie können die elektrischen oder logischen Tests sinnvoll unterstützen, speziell bei Fehlbestückungsproblemen.

Bei funktionalen Tests ist es ohne aufwändige und umfangreiche Prüfprogramme kaum möglich, Fehler für eine exakte Diagnose und zur Reparatur genau genug einzugrenzen. Dies erfordert langjährig erfahrenes Personal, entsprechende Software und viel Zeit für die Umsetzung. Nicht umsonst wird vieles an Testentwicklung an entsprechend spezialisierte Testhäuser ausgelagert.

Boundary-Scan-Verfahren als Kompromiss zwischen Aufwand und Aussagekraft

Tests mit In-Circuit Testern benötigen entsprechendes Equipment, jedoch sprengen oft allein die Prüfadapterkosten den vorgegebenen Kostenrahmen, besonders bei geringen Stückzahlen, wie sie im Embedded-Bereich oft anzutreffen sind. Oft ist es bei kompakten Baugruppen nicht einmal möglich, alle benötigten Testpunkte auf den Außenseiten der Platine unterzubringen. Im Zeitalter von "Buried Vias" und BGA-Gehäusen mit Hunderten von Pins ist typischerweise nur noch ein geringer Teil der Netze an den Bauelementen oder Durchkontaktierungen frei zugänglich.

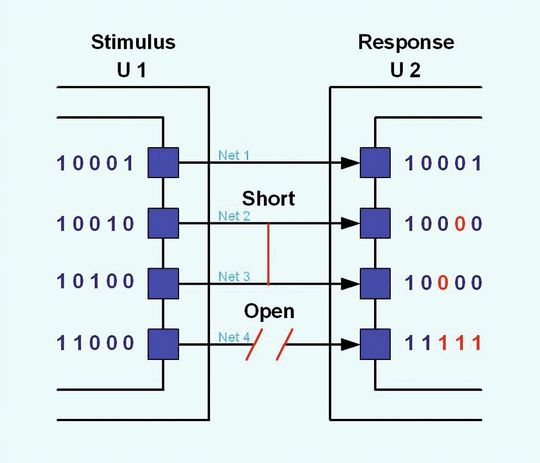

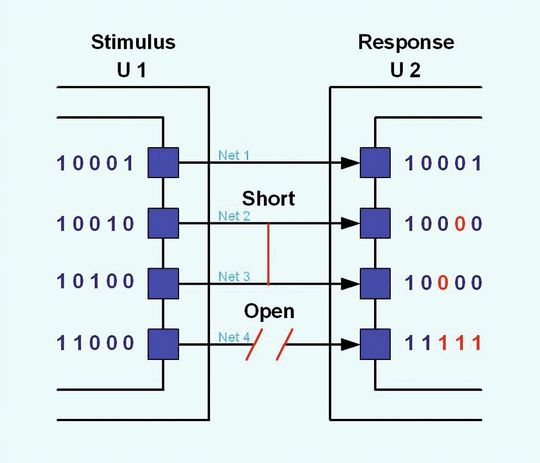

Einen guten Kompromiss zwischen Aufwand und Aussagekraft der Ergebnisse stellt das Boundary-Scan-Testverfahren dar. Dieses wurde ursprünglich von der JTAG entwickelt und 1990 erstmals im IEEE-Standard 1149.1 festgelegt [1]. Hierbei werden Boundary-Scan-fähige Bauteile in einen speziellen Testmodus gesetzt, um mit speziellen Testmustern stimuliert zu werden. Aus den Rückantworten oder durch das resultierende Ausgangsmuster dieses „Scans“ können aussagekräftige Rückschlüsse auf Funktion und Konnektivität der Schaltung gezogen werden [Bild 2].

Zugang zum Board via JTAG-Schnittstelle

Der zusätzliche Aufwand ist überschaubar, da die komplette Boundary-Scan-Logik mit vier oder fünf Signalen auskommt, die zwischen den Boundary-Scan-fähigen Bauelementen zusätzlich entflochten werden müssen.

Zugang zur Platine erfolgt über einen intelligenten, meist an einen PC angeschlossenen JTAG-Controller, der über eine entsprechende JTAG-Schnittstelle mit der Schaltung verbunden wird. Diese JTAG-Schnittstelle ist bei vielen Leiterplatten, insbesondere Prozessor-Boards, bereits vorhanden, da sie auch zum Debuggen einzelner Bauteile während der Produktentwicklung benötigt wird.

Es ist erforderlich, dass mindestens ein IEEE1149.1-kompatibles Bauteil in der zu testenden Schaltung vorhanden und über seinen Test Access Port [TAP] zugänglich ist, um die Baugruppe mit Boundary Scan testen zu können.

Auf der nächsten Seite: Wie sich die Prüfzeiten verkürzen lassen

(ID:31216900)

:quality(80)/p7i.vogel.de/wcms/37/ec/37ece4c276f37114e8f40696ff5dcd66/0130537789v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/46/7c/467c0afffbfd10c3553c2888a4a6289f/0130479810v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/12/3d/123d9eb2c2e4ce13296371a2ad3718a4/0130412664v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/e7/b6e755d9e704319c0bb59dc1ac2d67e8/0130537290v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/8b/10/8b10d1edceb749de99c1df3ad97be01e/0130564619v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ac/da/acda3bafe46d3bf8e104a2a7bc2ac557/0130535476v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ca/9b/ca9b681785123f9700518a46897f9779/0130428786v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/38/cb/38cbe19e814dd30b94780bc3946547ab/0130446533v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/88/c28805ea7b2261235475146a5b0c61f8/0130313028v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/8d/fa8dedee195f29c33c89d86311c258ee/0130104146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/7a/697a270ed7538378d1fbc0f0b240ed25/0130534691v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/e7/a4/e7a4e048491e60cb30e22a860f5d68bc/0130519425v4.jpeg)

:quality(80)/p7i.vogel.de/wcms/1b/f0/1bf02d41e3eac721823841a4c1228753/0130519149v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1a/53/1a539631c940d184689460600bd2b395/0130410666v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/10/45/1045969e69a1db4aaa73d0f74f55cc02/0129962687v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/e4/bae4e54395e5a53088060531ef99b814/0130359274v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/af/35af7dd326d198475d06fbb69aa600b5/0130175971v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/2e/c02e7bf72bfc434888c37100e2511681/0130127767v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/e1/0b/e10bc04827e33786548587e32bbae422/0130438700v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/06/3506f2a8d33a696aaef12a30771bd8d8/0130496747v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/ed/e5ed08c670c44565a9130e95a760dddc/0130494578v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ce/33/ce336bc438b912829effe8d4704dc159/0130480307v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/3a/72/3a722ed2ad6ac4894c352e6ce87b6560/0130567207v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e4/d1/e4d122a8ecce14b98c8298c1cc130194/0130561462v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/3c/55/3c5505dd3ca3971cddd09c583a4c907d/0130458429v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/47/ce/47ce64bad7990f276f68cbb24505f6dd/0130472850v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/2e/95/2e9597b5dc1873771c7fe9c32ac41e82/0130549010v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/15/56/15564dea31861c376a385658c3b961a3/0130465243v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bf/2a/bf2aad428ab1a80e6738fdbdc2efeb7e/0130453420v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/5f/15/5f157c2d880f4/ish-logo2020.jpg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/68800/68851/65.jpg)

:fill(fff,0)/p7i.vogel.de/companies/5f/88/5f8847c90d2e4/50-mm.jpg)

:quality(80)/p7i.vogel.de/wcms/ff/e4/ffe44f0dcf0fc0323926b1bc0a60d94f/0129386849v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/4f/22/4f2287af1f07561a5703d6a20f39494b/0128418964v2.jpeg)