HDI-Leiterplatten - Teil 15 Welche Fertigungseinflüsse sich wie auf die Toleranzen bei der Impedanz auswirken

Nachdem wir in Kapitel 14 die grundlegenden Begriffe und Aufgaben bei impedanzkontrollierten Leiterplatten veranschaulicht haben, folgt nun die Praxis. Karim Richlowski, Leiter CAM beim Berliner Leiterplattenhersteller CONTAG erklärt, worauf Entwickler bei Leiterplatten mit impedanzkontrollierten Leiterzügen in der praktischen Anwendung achten müssen.

Anbieter zum Thema

Wie wir in der letzten Folge gelernt haben, ist die Grundimpedanz einer Leiterbahn primär abhängig von deren Geometrie (Querschnitt) und dem Abstand zu den Bezugslagen. Beides wird bereits mit dem Lagenaufbau festgelegt. Durch die diskreten (also nicht stufenlos und frei wählbaren) Vorgaben der Werte für Laminat- und Kupferschichtdicke sowie die üblichen Leiterbahnraster (z.B. 75, 100, 125 und 150 mm) ist hier die Anzahl an sinnvollen Kombinationsmöglichkeiten für eine bestimmte Zielimpedanz nicht allzu groß. Zudem werden die möglichen Laminatdicken auch noch durch das maximale Aspect Ratio eingeschränkt. Dies gilt insbesondere bei der Verwendung der in der HDI-Technik üblichen Mikrovias.

So ergibt sich aus der geforderten Verdrahtungsdichte zunächst die Anzahl an benötigten Lagen, die Nennbreite der Leiterbahnen und die Größe der verwendeten Vias und Mikrovias. Daraus folgt die maximale jeweilige Lagendicke. Danach wird versucht, durch Variation von Kupferschichtdicke und Leiterbahnbreite die gewünschte Zielimpedanz einzustellen.

Impedanz schwankt produktionsbedingt ±10%

Zur groben Abschätzung kann man hier meist Tabellen des Leiterplattenherstellers oder auch Empfehlungen aus den Datenblättern der Halbleiterhersteller verwenden. In der Praxis liegt dann die produktionsbedingte Schwankungsbreite der Impedanz bei etwa ±10% für eine Standardtechnologie, was für viele Anwendungsfälle bereits genügt.

Zu berücksichtigen ist dabei aber auch, dass sich diese Schwankung auf den errechneten Nennwert bezieht. Weicht dieser bereits von der Zielimpedanz ab, so ist diese Abweichung der Toleranz hinzuzufügen. Will man also z.B. eine Zielimpedanz von 100Ω erreichen und der sich aus den Geometrien errechnende Nennwert liegt bei nur 96Ω, so ergibt sich dann bei einer Produktionstoleranz von ±10% ein Minimum von etwa 86Ω was dann schon einer maximalen Abweichung von gut 14% entspricht!

Wichtig ist das passende Impedanzmodell

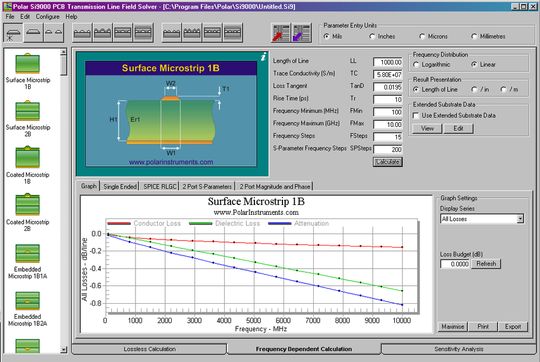

Will man die in Sondertechnologien erreichbaren minimalen Toleranzen von ±5% und weniger erreichen, so genügen einfache Tabellen und Überschlagsrechnungen nicht mehr, sondern die jeweiligen Impedanzwerte müssen einschließlich ihrer jeweiligen Toleranzen exakt kalkuliert werden. Dies fängt bereits mit der Wahl der richtigen und detaillierten Impedanzmodelle an. Moderne Software für diese Berechnung wie die bei CONTAG eingesetzte von Polar Instruments verfügt über knapp hundert unterschiedliche Impedanzmodelle!

In der Praxis ist es zwingend erforderlich, dass der Leiterplattenhersteller auf seinem CAM-Arbeitsplatz sensitivitäts-kritische Parameter optimieren kann. Viele der Impedanz beeinflussenden Werte sind im Detail produktionsspezifisch. Als Beispiel sei hier die Breite und (Trapez-)Form der Leiterbahnen genannt, die sich durch Unter- oder Überätzung stark ändern können. Weitere Toleranzfaktoren sind unter anderem die Pressdicke in Abhängigkeit von Kupferdicke und Kupferbelegung, Lötstopplacke, Kupfer-Schichtaufträge in Abhängigkeit von Kontaktierungen sowie Bearbeitungsschritte wie Planen und Schleifen beim eventuellen Hole-Plugging-Prozess.

Hier kann der Entwickler dem Leiterplattenhersteller bereits wirkungsvoll zuarbeiten, indem er z.B. bei impedanzkritischen Leiterbahnen die nächst größere Leiterbahnbreite oder eine andere Kupferschichtdicke wählt, um die Sensitivität der Leiterbahnimpedanz gegenüber den Ätzeinflüssen herunterzusetzen. Viele CAD-Werkzeuge enthalten heute bereits hilfreiche Hilfsmittel zur Impedanzberechnung und ermöglichen so dem Entwickler sinnvolle Voruntersuchungen anzustellen. Vor der endgültigen Festlegung einer Designtechnologie sollte aber unbedingt der Fertigungspartner mit ins Boot genommen und dessen Erfahrungswerte berücksichtigt werden.

Impedanzkritische Signale wenn irgend möglich als Innenlagen führen

Wie in Kapitel 14 wird auch hier noch einmal ausdrücklich auf die Tatsache hingewiesen, dass sich die Kupfer-Schichtdicken auf die tatsächliche Schichtdicke beziehen. Wie der aufmerksame Leser dieser Serie aber weiß, nimmt die Kupferschichtdicke beim sequentiellen Lagenaufbau auf den Innenlagen durch die Ätzprozesse ab und auf allen Außenlagen, auf denen Kontaktierungen enden durch den Kontaktierungsprozess zu. Dabei ist die Abnahme der wirksamen Schichtdicke auf den Innenlagen wesentlich gleichmäßiger und zuverlässiger kalkulierbar als der Schichtaufbau auf den beim jeweiligen Kontaktierungsprozess wirksamen Aussenlagen.

Sinnvollerweise sollten daher impedanzkritische Signale soweit irgendwie möglich auf einem Kern als Innenlagen geführt werden. Zur Vermeidung von ungewollten differentiellen Impedanzen sind die Mindestabstände zu Nachbarleitungen und Potentialflächen auf der gleichen Ebene unbedingt einzuhalten.

Impedanzen müssen während oder direkt nach der Leiterplattenfertigung ermittelt werden

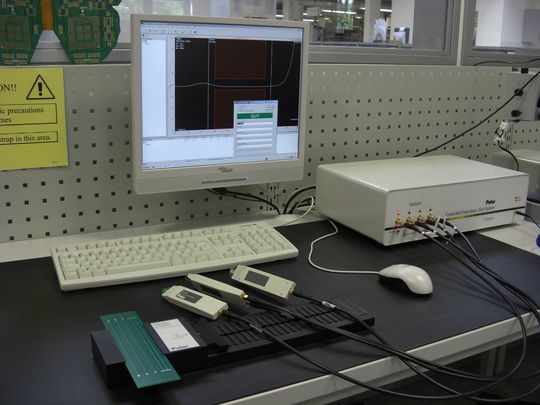

Ist die Leiterplatte erst einmal bestückt lassen sich die Impedanzen der Leiterbahnen nicht mehr bestimmen. Kritische Impedanzwerte müssen also noch während oder unmittelbar nach dem Produktionsprozess der Leiterplatte ermittelt werden. Dazu werden auf den Produktionsnutzen zusätzlich zu den einzelnen Leiterplatten eigene Leiterplatten zum Impedanztest mit aufgebracht. Diese werden als Testcoupons bezeichnet und enthalten für die jeweilige Technologie charakteristische Leiterbahnzüge, aus denen dann durch Vermessen die entsprechenden Qualitätsaussagen für die Leiterplatten auf dem gleichen Nutzen getroffen werden können. Diese werden dann entweder einzeln oder im Stichprobenverfahren an einem speziellen Messplatz ausgewertet.

Bei CONTAG kommt hier zur Endkontrolle mit einem CITS900s von Polar ein Messgerät der allerneuesten Generation zum Einsatz. Die Ergebnisse der Prüfung werden nach DIN ISO 9002 protokolliert und stehen auf Anforderung zur Verfügung. Vielfach können auch Teststrukturen (ggf. auch zusätzlich zu den Testcoupons) auf den Leiterplatten selbst mit aufgebracht werden, wenn dies platz- und funktionsmäßig möglich ist.

Auch hier gilt wieder: Wichtig ist die sorgfältige und frühzeitige Abstimmung mit dem Lieferanten des Vertrauens. Mit dessen Know-How und Erfahrung können unnötige Fehler und Irrwege bereits frühzeitig vermieden und Kosten eingespart werden.

Hier finden Sie alle Teile der Beitragsreihe HDI-Leiterplatten

(ID:256595)

:quality(80)/p7i.vogel.de/wcms/e9/ce/e9ce137e87eccac328ec5504c586c477/0129711019v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/68/46/684697b6eb687384e0d8c6803450401a/0130056395v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/0f/c0/0fc0d93c99a5d9066e58c39f41fb1b10/0130046764v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/60/fa6016fc48ac8609a451038ca38b0eca/0130241261v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/57/97/5797ffe4c6e19cf02aa75a7f742598b3/0130160607v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1d/d8/1dd8627e2323721d4ee5436f9401911e/0130147601v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fb/d3/fbd33264fcdf128866667be0a0a6b657/0130137877v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a5/5e/a55ec741a9c17cb890b2cb5bcb919477/0130162776v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/8d/fa8dedee195f29c33c89d86311c258ee/0130104146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cc/13/cc1378375499a26b5ddbb309d2155acb/0130085649v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/24/58/2458f1cae3100e375fbb8124f02c54af/0130111244v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/6d/f0/6df06a1488ceb6357c287fee993fad65/0130161592v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/65/f4/65f404dc6d19d4f1628ad7e49f6a22cf/0130136276v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/fc/fafc300481de3fd4d7f34400327d0d01/0130127049v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/10/45/1045969e69a1db4aaa73d0f74f55cc02/0129962687v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c7/f6/c7f61d0437c7f8fca3c6ff947ba2ad62/0129322490v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/66/0c/660c31afa35398bac9be42f2be73fdc4/0129073529v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/af/35af7dd326d198475d06fbb69aa600b5/0130175971v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/2e/c02e7bf72bfc434888c37100e2511681/0130127767v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/95/a1/95a197490145b7afcfd4dc176a1b5ef9/0130096114v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ef/a0/efa0d8af7bcf1d64636b877a04b853d9/0130136738v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bf/82/bf82f81061b759c454e15ec4c2e7560b/0130110139v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/74/96/74964a7715c738a9e8b17681445ceed3/0130103633v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/0d/18/0d183ecb569b03285578762658d2def6/0130061201v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f1/58/f158a1c680219c67cff9c099186ab50d/siemens-20ubtech-20hmnd-1920x1079v1.png)

:quality(80)/p7i.vogel.de/wcms/6a/93/6a93991941467231d8798c8577882dfd/0130071573v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/19/31/193191c71275b1f480fff0e5827be766/0130211045v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d1/d1/d1d103805ed7ac0df7feda4c46522b8c/0130164847v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/68/7e/687ebf75f8024edeec7ebd6d3582327f/0130240314v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bb/2a/bb2ac8404ae7b3f08a5c01d1ca0615a7/0130182922v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/62/16/621651a93b1ef/logo-we-rgb-pos.png)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/68800/68851/65.jpg)

:quality(80)/p7i.vogel.de/wcms/2c/40/2c40cea54250c0cc97dbc8d8448798a5/0129385029v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/65/cf/65cf468d1d69175315e2ad58882d9db3/0127037035v2.jpeg)