Anbieter zum Thema

Speziell für SIL 3 von IEC61508 ausgelegter Mikrocontroller

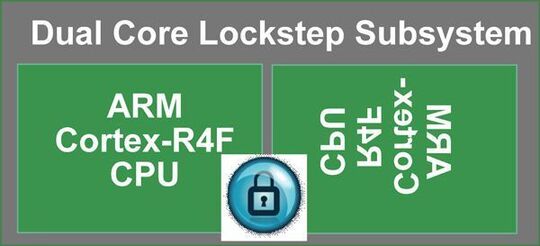

Die Mikrocontroller TMS570 sind speziell für den Safety Integrity Level 3 (SIL3) des IEC61508-Standards ausgelegt. Die TMS570LS-Familie verwendet auf dem Chip zwei identische ARM Cortex R4F CPUs, die dasselbe Programm im lock-step-Verfahren bearbeiten. Operationen und Ergebnisse beider Berechnungen werden in jedem CPU-Zyklus miteinander verglichen, um mögliche Fehler zu erkennen. Beide CPUs haben geometrische und zeitliche Diversität, um physikalische Fehler gemeinsamer Ursache zu erkennen. So ist die zweite R4F-CPU gespiegelt und gedreht und in der Abarbeitung um wenige Zyklen verzögert. Im Falle einer Fehlererkennung kann binnen weniger CPU-Zyklen ein fehlersicherer Zustand hergestellt werden. Da die Fehlererkennung rein von der Hardware bewerkstelligt wird, ist sie für die Software transparent.

In jeder CPU ist eine Fehlerkorrekturlogik integriert

Um Fehler im Programm- und Datenspeicher erkennen und darauf reagieren zu können, hat jede ARM Cortex R4F CPU eine integrierte Error-Correction-Logik (ECC), mit der sich einzelne Bitfehler korrigieren und Doppelfehler erkennen lassen. Zusätzlich werden intern Adress-Busse und Decoder überwacht.

Zwei Arten von Built-In-Self-Test-Modulen überwachen CPUs (LBIST) und Datenspeicher (PBIST). Das LBIST-Modul überprüft die ARM Cortex R4F CPU während der Initialisierung des Kontrollers oder während der laufenden Applikation auf versteckte CPU-Defekte. Das PBIST-Modul testet das RAM mit verschiedenen wählbaren Algorithmen. Generell helfen die eingebauten BIST-Module, die Software um entsprechende Test-Routinen zu erleichtern. Peripheriemodule, die über einen eigenen Datenspeicher verfügen, sind durch Paritätslogik abgesichert. Diese RAM-Bereiche können ebenso per PBIST getestet werden.

Signaling Module meldet Fehler nach außen

Um Zugriffe auf bestimmte Speicherbereiche zu überwachen und um diesen Bereichen spezifische Zugriffsrechte zuzuweisen, kann die integrierte Memory Protection Unit (MPU) verwendet werden. Zum Test gespeicherter statischer Daten ist eine 64-Bit-CRC-Einheit vorhanden, die per DMA im Hintergrund betrieben werden kann. Zusätzlich haben die Peripherie-Module eigene Fehlererkennungs-Fähigkeiten, z.B. den Selbsttest der A/D-Wandler.

Alle wichtigen Module zur Fehlererkennung sind mit dem Error Signaling Module verbunden, das eine zentralisierte Priorisierung und Auswertung sowie Signalisierung aller erkannten Fehler nach Außen ermöglicht.

Texas Instruments hat bei kundenspezifischen Lösungen auch langjährige Erfahrung mit asymmetrischen (nicht lock-step) TMS570-Architekturen, bei denen eine Cortex-R4- und eine Cortex-M3-CPU auf einem Chip integriert wurden. Hier kann bei sicherheitskritischen Applikationen die Cortex M3 CPU die Cortex-R4-CPU überwachen oder umgekehrt. Zusätzlich kann jede CPU eigene Aufgaben übernehmen, um so die Rechenleistung insgesamt zu erhöhen.

Mit Cache werden zukünftige Derivate noch leistungsfähiger

Die verwendeten Mikrocontroller-Kerne von ARM wurden u.a. für den automobile Anwendungen entwickelt und werden von vielen Halbleiterherstellern als Rechnerkerne verwendet. Die Vorteile liegen in einer Standardisierung, die es einer Vielzahl von Drittanbietern ermöglicht hat, diese CPU Kerne mit Entwicklungswerkzeugen und Softwarekomponenten zu unterstützen. FlexRay-Treiber und AUTOSAR-Pakete sind für den TMS570LS vorhanden.

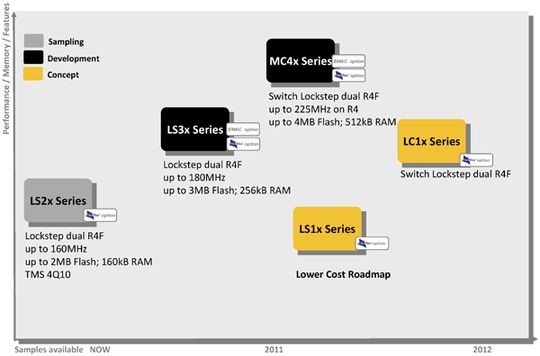

Auf dem Horizont der TMS570 Roadmap stehen Derivate mit 4 MByte Flash-Speicher, basierend auf zwei ARM Cortex R4F CPU in lock-step, der allerdings zur getrennten simultanen Abarbeitung unterschiedlicher Programme auftrennbar ist. Cache wird bei diesen Derivaten noch höhere Rechenleistungen ermöglichen, unterstützt durch einen optionalen zusätzlichen On-Chip-I/O-Prozessor.

*Gerhard Wenderlein ist Automotive System Applications Engineer bei Texas Instruments in Freising.

(ID:356586)

:quality(80)/p7i.vogel.de/wcms/f5/5e/f55e737a7d227f2d048c579cab8e6985/0130834955v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/33/b4/33b4ab2c6baf7bd98f6f31747f105ab7/0130823277v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/96/97/96978cf39fdc205e816e3218f39499e5/0130663068v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/37/59/37594ae9b98dc4acb8eeab90c835c984/0131089404v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/39/2b/392b7f42b33965cee9d46984d8e1c021/0131069829v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/14/e8/14e887156fd8fb66138bfc7972c4cd3f/0131074909v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/2e/78/2e789ef76c84f5fcdf02b5697a22f9ab/0131062677v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d9/92/d9920f978cf2b03bb4f2b4e6cfbface3/0131055455v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d2/1c/d21cea8a73c1dc8b94322e896fb7cc2b/0131036508v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/be/81/be8197dbe5f61c3c5ade3732457725af/0131041847v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/0d/34/0d34c0b5b16676a55682e081ca59da32/0130890395v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/cc/bacc37befe18c7062ab18bdae3ea75c7/0131064254v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f2/fb/f2fb476fbd80a9145a022a4d162002df/0131122156v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/c5/42/c542a36bfc0e9beb119924d176f19e06/0131065166v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/d4/1d/d41d81ec84a42b4fd5d732d36d0021ce/0130877962v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9c/79/9c798ab2b4c18ba0a2c24f2491798d36/0130550888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/e7/b6e755d9e704319c0bb59dc1ac2d67e8/0130537290v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ca/8c/ca8cda9df29d8b2cf6f7b09abd8b7dda/0131065542v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/71/fa71d141fca285824eb23f3aba1333f2/0131012876v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e1/39/e13927f73987c9fb63d6f7145a597e6a/0130656559v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/87/b6/87b60368567da3c6b65107c55f5f69ec/0130689118v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b4/55/b455edd54c7e92e0f5bf2d059e2cc5ca/0130990400v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9b/96/9b96763092ce22624400387c5f264287/0130960582v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/82/71/8271e36a4b6aa180fa903edd1de396f1/0130907348v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1e/27/1e27744bed9341deb4f1d27d541e04e3/0131125212v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/96/e4/96e4b9434e4bb7b4e06cccc26e8a6497/0131080817v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ec/6b/ec6bb7201f5a2e41cd4942d59b23b999/0131074433v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/0a/350a177ef33b960e8f24c9be3717c653/0131061473v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ae/92/ae92a78425f17c6358d01ffd9b1c90ed/0131050297v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fc/5e/fc5e77b8434779834850aab40a903347/0131047752v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/43/c2439a5f7ecd10d2d7f02a4a5f38e97d/0131046056v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/66/f6/66f673630a98a/logo-mc-rgb-300x300.png)

:fill(fff,0)/p7i.vogel.de/companies/64/21/64219ce08bf52/logo.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/5f/15/5f157c2d880f4/ish-logo2020.jpg)

:quality(80)/p7i.vogel.de/wcms/0a/f9/0af9ef52ce077b935efc629bd4e357a6/0128162746v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/51/be/51beb098c6a7b0e36878e833cb53a5c2/0128222643v2.jpeg)