SOC-Design mit konfigurierbaren CPUs Verlustleistung, Stromaufnahme und Kosten von SOC-Lösungen senken

Steigende Taktraten verursachen auch eine höhere dynamische Verlustleistung und Stromaufnahme, die in heutigen SOC-Lösungen zu einer nicht hinnehmbaren Wärmebildung und Energieaufnahme führt. Um die Taktraten herunterzuschrauben, muss der inhärente Parallelismus der Bausteinarchitektur ausgenutzt werden. Konfigurierbare Prozessoren helfen dabei.

Anbieter zum Thema

Die Weiterentwicklung von System-on-Chip-(SOC-)Lösungen wird heute durch die höhere Wärmebildung und Stromaufnahme bei steigenden Taktraten gehemmt. Eine Möglichkeit, diesen Trend umzudrehen, ist die Ausnutzung des inhärenten Parallelismus, der hohe Taktraten herunterschraubt. Programmierbare, konfigurierbare Mikroprozessor-Cores spielen bei der parallelen Datenverarbeitung eine wichtige Rolle. Auf herkömmliche Weise (mit festen ISA-/Befehlssatzarchitektur-Prozessoren) kann dies nicht erreicht werden. Die dynamische Leistungsaufnahme und der Energieverbrauch steigen mit der Taktfrequenz nach der Formel: Pdyn = ½ CU²f. Darin ist C die gesamte geschaltete Kapazität aller Knoten auf dem Chip, U die Core-Betriebsspannung und f die Taktfrequenz.

Die dynamische Leistungsaufnahme ist direkt proportional zur Taktfrequenz – SOCs müssen aber bei höheren Core-Spannungen betrieben werden, um die höchstmöglichen Taktfrequenzen zu erzielen. Dies bringt wiederum U² mit ins Spiel, was zu einer superlinearen Beziehung zwischen dynamischer Leistungsaufnahme und Betriebsfrequenz führt. Die Batterielebensdauer ist umgekehrt proportional zum Leistungsverbrauch. SOCs, die eine hohe Leistung aufnehmen, führen zu Produkten mit kurzen Betriebs- bzw. Sprechzeiten und inakzeptablen Standby-Zeiten. Dann sind größere und teurere Batterien und Stromversorgungen erforderlich, die viel Energie verbrauchen, um SOCs zu versorgen, die dementsprechend viel Leistung benötigen.

Kleinere Taktrate – weniger Leistungsaufnahme

Energieeinsparungen finden grundsätzlich auf Systemebene statt. Der Schlüssel für solche Einsparungen in digitalen Systemen ist eine geringere Taktrate. Niedrigere Taktraten verringern sofort die dynamische Leistungsaufnahme und den Bedarf an fortschrittlichen IC-Prozessen. Damit kehrt sich der gegenwärtige Aufwärtstrend bei der statischen Energieaufnahme um. Eine Möglichkeit, Taktraten zu reduzieren ist eine höhere Parallelität bei der Ausführung. Hardwareentwickler nutzen von Grund auf Parallelismus — Mikroprozessor-basierte Designs arbeiten aber genau umgekehrt. Um den Hardwareaufwand zu verringern, nutzen MPU-basierte Systeme Multitasking-Betriebssysteme, die es dem Prozessor erlauben, verschiedene Tasks parallel auszuführen.

Die Taktrate des Prozessors wird somit die zusammengefügte Taktrate, die nötig ist, um alle diese Tasks auszuführen. Als die Stromaufnahme noch kein Problem war, MPUs in einzelnen Gehäusen verfügbar waren und Tasks noch einfach gehalten wurden, machte es Sinn, die Hardwarekosten durch Multitasking zu verringern. Prozessoren in 90- und 65-nm-SOCs verbrauchen aber weniger als 1 mm² Siliziumfläche. Um hohe Taktraten und einen unnötigen Energieverbrauch zu vermeiden, macht es heute Sinn, mehr Prozessoren mit niedrigerer Taktrate zu verwenden (weniger Multitasking). Es macht auch Sinn, jeden Prozessor für seine zugewiesene Aufgabe maßzuschneidern. Dazu dient die in konfigurierbaren Prozessoren vorhandene ISA-Erweiterung. Diese Anpassung macht jeden On-Chip-Prozessor bei der Ausführung bestimmter Algorithmen effizienter. Eine höhere Effizienz erlaubt es dem Prozessor, den Algorithmus in der gleichen Zeit aber mit weniger Befehlen auszuführen.

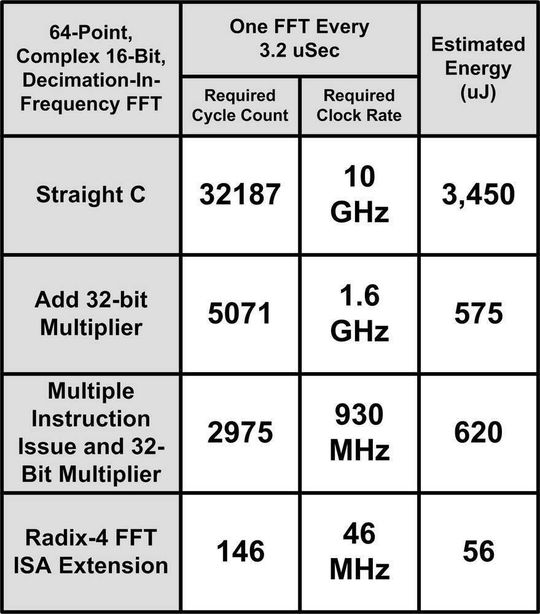

Die Fast-Fourier-Transformation (FFT) dient als Beispiel für einen Algorithmus, der sich durch ISA-Anpassung erheblich beschleunigen lässt. Die FFT zerlegt Sig-nale in ihre einzelnen Frequenzbestandteile und kommt in Kommunikationsanwendungen zum Einsatz. Der 802.11g Wireless PHY wickelt z.B. 64-Punkt-/Radix-4-Frequenzdezimierungs-FFTs ab, die alle 3,2 µs ausgeführt werden. Radix-4-FFTs werden meist mit Schmetterlingsblöcken in Hardware implementiert (Schmetterling ist die grundlegende FFT-Operation). Dies erfordert zwölf 16 × 16-Bit-Multiplizierer und mehr als 20 16-Bit-Addierer. Eine FFT in Software zu implementieren ist eher ungewöhnlich (Tabelle 1), da hohe Taktraten erforderlich wären. Mit direktem C-Code benötigt ein 32-Bit-RISC-Prozessor (ohne Hardware-Multiplizierer) 32.187 Zyklen zur Ausführung des FFT-Algorithmus. Um eine dieser FFTs alle 3,2 µs auszuführen, müsste der Prozessor mit 10 GHz getaktet werden. Dies wäre selbst für jeden Prozessor eine eindeutig nicht erfüllbare Taktrate, geschweige denn für einen synthetisierten SOC.

ISA-Anpassung: Gleiche Zeitdauer – weniger Befehle

Tabelle 1 zeigt das Ergebnis der zunehmenden ISA-Anpassung bei der FFT. Das Hinzufügen eines 32-Bit-Multiplizierers zum RISC-Prozessor verringert die erforderliche Taktrate auf 1,6 GHz, was zwar als besser erscheint, aber immer noch außerhalb der Reichweite synthetisierbarer Prozessoren liegt. Eine superskalare CPU, die gleichzeitig mehrere RISC-Befehle ausgeben kann und das Hinzufügen eines Hardware-Multiplizierers verringert die Taktrate nur auf 930 MHz, was an der Grenze des Machbaren für einen synthetisierbaren Prozessor liegt. Das Hinzufügen eines Radix-4-Schmetterlings-Befehls verringert die Taktrate allerdings auf 46 MHz (um das 217-Fache) und die Stromaufnahme um das 62-Fache.

Fast jeder Algorithmus lässt sich ähnlich adressieren. So entwickelte Tensilica den Diamond 330HiFi Audio Engine Prozessor-Core, der eine Vielzahl digitaler Audio-Codecs bei niedrigen Taktfrequenzen bearbeiten kann – und das über eine Erweiterung der eigenen Xtensa-RISC-Prozessor-Core-ISA um etwa 300 neue Befehle. Als Ergebnis erfordern viele der digitalen Audio-Codecs nur noch wenige MHz Prozessorbandbreite, was die Stromaufnahme zur Ausführung dieser Codec-Algorithmen erheblich verringert.

Die Firmware-Programmierbarkeit der Audio Engine erlaubt die Bearbeitung verschiedener Codecs. Mit so einem Audio-Prozessor lassen sich Produkte entwickeln, die Musik in verschiedenartig codierten Formaten mit einer Batterieladung über 100 Stunden wiedergeben können. Kunden schätzen dies und sind auch bereit, für solche Produkte mehr zu zahlen. Die Programmierbarkeit und die geringe Stromaufnahme, die diese konfigurierbaren Prozessoren bieten, ermöglichen also Strom sparende Produkte für verschiedenste Märkte.

*Steve Leibson ist Technology Evangelist bei Tensilica, Santa Clara, Kalifornien.

(ID:261913)

:quality(80)/p7i.vogel.de/wcms/46/7c/467c0afffbfd10c3553c2888a4a6289f/0130479810v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/12/3d/123d9eb2c2e4ce13296371a2ad3718a4/0130412664v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d8/78/d878b7bfc23826e6ddfce42443836d28/0130384280v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ac/da/acda3bafe46d3bf8e104a2a7bc2ac557/0130535476v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/42/cb/42cbcb66dffa2ef6548d5fb2edee4b4a/0130519441v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/51/39/513947834151d4d220913a68592e342c/0130517810v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ca/9b/ca9b681785123f9700518a46897f9779/0130428786v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/38/cb/38cbe19e814dd30b94780bc3946547ab/0130446533v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6b/61/6b61373f1c3f06f7f9343e6b0f0e9cc8/0130225062v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/88/c28805ea7b2261235475146a5b0c61f8/0130313028v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/8d/fa8dedee195f29c33c89d86311c258ee/0130104146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cc/13/cc1378375499a26b5ddbb309d2155acb/0130085649v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/7a/697a270ed7538378d1fbc0f0b240ed25/0130534691v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/e7/a4/e7a4e048491e60cb30e22a860f5d68bc/0130519425v4.jpeg)

:quality(80)/p7i.vogel.de/wcms/1b/f0/1bf02d41e3eac721823841a4c1228753/0130519149v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1a/53/1a539631c940d184689460600bd2b395/0130410666v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/10/45/1045969e69a1db4aaa73d0f74f55cc02/0129962687v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c7/f6/c7f61d0437c7f8fca3c6ff947ba2ad62/0129322490v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/e4/bae4e54395e5a53088060531ef99b814/0130359274v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/af/35af7dd326d198475d06fbb69aa600b5/0130175971v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/2e/c02e7bf72bfc434888c37100e2511681/0130127767v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/e1/0b/e10bc04827e33786548587e32bbae422/0130438700v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/06/3506f2a8d33a696aaef12a30771bd8d8/0130496747v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/ed/e5ed08c670c44565a9130e95a760dddc/0130494578v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ce/33/ce336bc438b912829effe8d4704dc159/0130480307v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/79/cd/79cd655c965ba69363382e5202450ea9/0130532716v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/66/95/66955b49a1ac94a639b83e70354d2736/0130526171v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/68/85/68852cc81fd6425ff9084ac5ad8944bc/0130521303v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/3c/55/3c5505dd3ca3971cddd09c583a4c907d/0130458429v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/47/ce/47ce64bad7990f276f68cbb24505f6dd/0130472850v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/15/56/15564dea31861c376a385658c3b961a3/0130465243v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bf/2a/bf2aad428ab1a80e6738fdbdc2efeb7e/0130453420v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/c8/b6c8f7732da417bda3d298412f4c0ed8/0130453104v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/64/21/64219ce08bf52/logo.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/5f/15/5f157c2d880f4/ish-logo2020.jpg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/72000/72046/65.jpg)

:quality(80)/p7i.vogel.de/wcms/92/43/9243cfe82b7ab3448679ded83cb50204/0129762425v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)