Aufbau- und Verbindungstechnik System-in-Package entwickelt sich zur Technologie für die Massenproduktion

System-in-Package (SIP) hat sich zu einem alternativen Ansatz zum System-on-Chip (SOC) entwickelt. Zukünftige SIPs basieren weitestgehend auf der 3D-Integration. Für diese komplexe Systemarchitektur sind neben neuen Technologien auch verbesserte Materialien sowie adäquate Systemdesign-Tools und geeignete Zuverlässigkeitsmodelle erforderlich.

Anbieter zum Thema

Die Entwicklung in der Mikroelektronik bezüglich Integrationsdichte wird seit Jahren durch das „Moore’sche Gesetz“ charakterisiert. Diese Tendenz wird sich in den nächsten Jahren auch weiter fortsetzen. Allerdings kann eine Skalierung der Strukturgrößen in der Mikroelektronik allein nicht mehr den heutigen Anforderungen von intelligenten elektronischen Systemen in Bezug auf Funktionalität, Leistung, Miniaturisierung, geringe Fertigungskosten sowie schnelle Markteinführung gerecht werden.

Die traditionelle Aufbau- und Verbindungstechnik wandelt sich mehr und mehr zu einer komplexen Systemintegration. Dieser Trend führt zu neuen System-in-Package-(SiP-)Lösungen, welche die Synergie und Kombination von Wafer- und Board-Level-Integrationstechnologien erfordern. Zukünftige SiPs basieren weitestgehend auf der 3D-Integration, was zu einer komplexen Systemarchitektur führt, die neben der Beherrschung neuer Technologien auch verbesserte Materialien sowie adäquate System-Design-Tools und geeignete Zuverlässigkeitsmodelle erfordert. Diesen zukünftigen Herausforderungen muss sich die Systemintegration bereits heute stellen.

SiP ist ein alternativer Ansatz zur SoC-Lösung, aber kein Ersatz

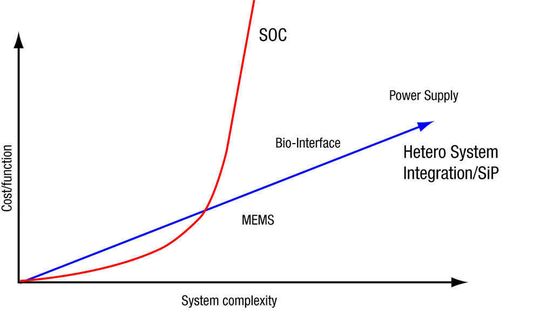

System-in-Package (SiP) hat sich zu einem alternativen Ansatz zu System-on-Chip (SoC) für die Integration elektronischer Komponenten entwickelt, da sie gegenüber SoC einige wesentliche Vorteile in vielen Marktsegmenten aufweist. SiP ist kein Ersatz für Siliziumintegration, sondern ist als Ergänzung anzusehen.

SiP- und SoC-Technologien zeichnen den Weg für eine weitere, kontinuierliche Leistungsverbesserung, Verlustleistungsreduzierung, Kostenreduzierung und Miniaturisierung auf Systemebene. Für einige Anwendungen mit hohen Produktionsstückzahlen wird SoC der bevorzugte Ansatz sein. In anderen Anwendungsgebieten werden komplexe SiPs, die ebenfalls SoC-Komponenten enthalten, zum Einsatz kommen.

Die System-in-Package-Technologie (SiP) entwickelt sich rasant von einer ehemals Spezialtechnologie zu einer Technologie für die Massenproduktion mit weitreichendem Einfluss, besonders auf dem preissensiblen Consumer-, Kommunikations- und Informationsmarkt.

Voraussetzungen für eine schnelle Markteinführung

Um eine schnelle Markteinführung neuer Produkte mit den gestiegenen Funktionalitäts- und Zuverlässigkeitsansprüchen bei gleichzeitig niedrigen Produktionskosten zu genügen, müssen eine Reihe von Anforderungen an die Infrastruktur erfüllt sein. Diese betrifft unter anderem die Verfügbarkeit geeigneter Integrationstechnologien auf Wafer- und Board-Level, preiswerte, hochdichte Substratverdrahtungsträger sowie verbesserte Materialien und kostengünstige Montageverfahren und -anlagen. Darüber hinaus ist die Verfügbarkeit von geeigneten Tools für das Chip-Package-Co-Design sowie für die Zuverlässigkeitsbewertung erforderlich. [Referenz: White Paper SiP, ITRS, TWG A&p]

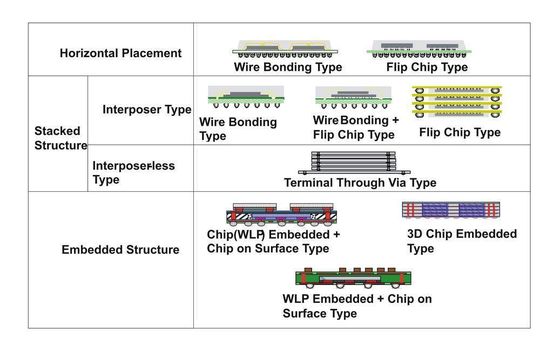

Zahlreiche SiP-Konzepte werden besonders durch die Anforderungen von mobilen Produkten aus dem Consumer-Bereich bestimmt. Die Grafik gibt einen Überblick über die SiP-Technologien, wie sie von der International Technology Roadmap of Semiconductors (ITRS) definiert werden.

Schlüsseltechnologie 3D-Systemintegration

Heute ist die 3D-Systemintegration eine Schlüsseltechnologie, deren Entwicklung vor allem durch Anwendungen in den Bereichen Information und Kommunikation Transport Sicherheit und Mobilität, Energie und Umwelt sowie Gesundheit vorangetrieben wird. Hierfür sind, unter anderem, elektronische Systeme wie Kamera- und Sensormodule, ultra-kleine Sensorknoten, Prozessor/Speichersysteme mit hoher Kapazität und Performance sowie Systeme mit Parallelprozessorarchitektur notwendig.

Haupttriebkräfte für die 3D-Integration sind:

- Formfaktor: Reduzierung von Systemgröße, Gewicht und Fläche,

- Leistung: Verbesserung der Integrationsdichte, kurze Signallaufzeiten, Reduzierung des Leistungsverbrauchs und

- Kostenreduzierung.

Es gibt verschiedene Konzepte für den 3D-Integrationsansatz. Diese beinhalten:

- Package-on-Package (PoP) und Package-in-Package (PiP),

- Chip-Stacking auf Leiterplatte (PCB) mit Drahtbond- und Flip-Chip-Kontaktierung,

- eingebettete elektronische Komponenten in der Leiterplatte mit Stapeln von dünnen, organischen Substratträgern,

- Wafer-Level-Systemintegration mit Siliziumdurchkontaktierungen (TSV).

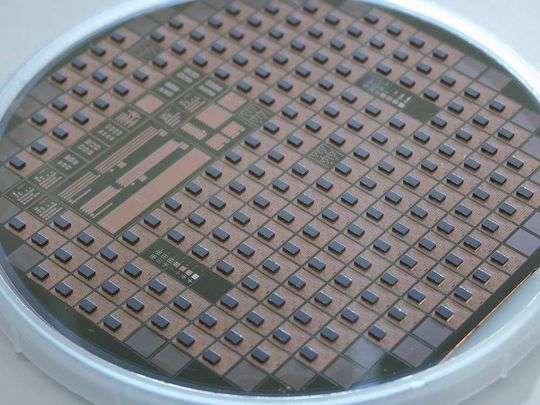

Eine der zukunftsweisenden 3D-Technologien ist die Durchkontaktierung von Silizium, sogenannte Through Silicon Vias (TSV), um sehr hohe Verdrahtungsdichten, ausgezeichnete elektrische Verbindungen zwischen Komponenten auf kleinstem Raum zu realisieren sowie gleichzeitig eine heterogene Integration von analogen, digitalen und MEMS-Komponenten zu ermöglichen.

Through Silicon Vias (TSV): Schlüssel für Durchbruch der 3D-Systemintegration

Die Verfügbarkeit kostengünstiger Technologien auf der Basis von TSVs ist ein Schlüssel für den Durchbruch der 3D-Integration. Deshalb werden weltweit große Anstrengungen unternommen, um entsprechende produktionstaugliche Prozesse zu entwickeln. In Kombination mit der sogenannten „Umverdrahtungstechnologie“ (RDL) können zusätzlich passive und aktive Komponenten integriert werden und somit modulare 3D-Konzepte umgesetzt werden.

Generell gibt es zurzeit unterschiedlichste Technologien im Entwicklungs- und Forschungsstadium. Einige Kernthemen sind:

- hochdichte und kostengünstige Siliziumdurchkontaktierungen (TSV) mit hohem Aspektverhältnis in aktiven und passiven Siliziumträgern (interposer),

- Waferdünnen und Handling gedünnter Wafer und Komponenten,

- Wafer-(die to wafer/ wafer to wafer)/Board-Level-Assemblierungstechnologien,

- Niedrigtemperaturverbindungsprozesse,

- eingebettete Komponenten (SI. InP, GaAS, SiGe), Passive und MEMS-Integration,

- integrierte Kühlkonzepte,

- hochfrequenzkompatible 3D-Systeme (Abschirmung, Impedanzkontrolle),

- optische Chip-zu-Chip-Verbindungen,

- integrierte Energieversorgung.

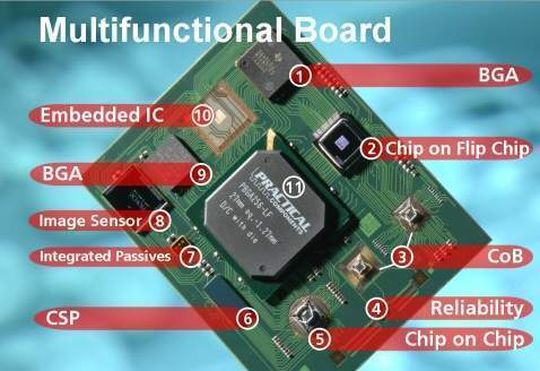

Leiterplatte wandelt sich zum multifunktionalen Systemboard

Auch auf Board-Level wurden auf der Basis von kostengünstigen, Flip-Chip- und drahtbondkompatiblen Substratmaterialien neue Integrationskonzepte entwickelt. Besondere Herausforderungen liegen hier im Supply-Chain, was grundsätzlich für alle neuen 3D-Integrationstechnologien gilt.

In letzter Zeit wurden einige Technologien entwickelt, um aktive Komponenten in das Substratmaterial zu integrieren. Ein Beispiel ist der „Chip in Polymer“-Ansatz des Fraunhofer IZM. Weitere Herausforderungen für die Integration auf Board-Ebene sind die Montage von sehr kleinen Komponenten, von dünnen Halbleiterkomponenten, die Integration von polytronischen Komponenten, die Entwicklung von geeigneten Kühlkonzepten sowie zukünftig auch die Integration der Energieversorgung. Die traditionelle Leiterplatte wird sich in naher Zukunft zu einem multifunktionalen System-Board wandeln.

(ID:276212)

:quality(80)/p7i.vogel.de/wcms/12/3d/123d9eb2c2e4ce13296371a2ad3718a4/0130412664v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d8/78/d878b7bfc23826e6ddfce42443836d28/0130384280v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e9/ce/e9ce137e87eccac328ec5504c586c477/0129711019v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/6a/02/6a02a8a58bcaf3736921685cbed39a1e/0130347041v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6b/61/6b61373f1c3f06f7f9343e6b0f0e9cc8/0130225062v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/15/93/1593dd152e6d58c5fc5da0d331777c54/0130357398v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/88/c28805ea7b2261235475146a5b0c61f8/0130313028v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/8d/fa8dedee195f29c33c89d86311c258ee/0130104146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cc/13/cc1378375499a26b5ddbb309d2155acb/0130085649v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6d/91/6d91abfa1b16ffcf470c7147facd7aa8/0130387695v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/85/b0/85b0b32128f6d1968e975043f1e0b67b/0130342166v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/81/c0/81c03683c33cf69903df78a57145bcca/0130328599v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1a/53/1a539631c940d184689460600bd2b395/0130410666v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/10/45/1045969e69a1db4aaa73d0f74f55cc02/0129962687v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c7/f6/c7f61d0437c7f8fca3c6ff947ba2ad62/0129322490v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/e4/bae4e54395e5a53088060531ef99b814/0130359274v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/af/35af7dd326d198475d06fbb69aa600b5/0130175971v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/2e/c02e7bf72bfc434888c37100e2511681/0130127767v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/b3/65/b365dd5433c8b6d36c56c92b72f5b368/0130401081v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ac/31/ac31fbd47f85c24ae7d13a73555c85e6/0130236430v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ef/a0/efa0d8af7bcf1d64636b877a04b853d9/0130136738v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bf/82/bf82f81061b759c454e15ec4c2e7560b/0130110139v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/85/6a/856aec9f218925fb1f721e7c85375bb8/0130433994v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/07/e0/07e00d0f3d9cabf1d537aca05fa0798a/0130437089v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/22/80/22809bb6b20cad637f38e877a95b01fd/0130428252v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ff/da/ffdab6ffda9fbb1e1665fef8bc8786db/0130361632v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e8/e9/e8e960a3a1fbdc151b6bdfb3ef0e608f/0130392421v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/47/f7/47f702467fac99e96e3bc5e5ff072691/0129859530v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/da/49/da496f69f977a3bff5c2303a7ec48a14/0130415034v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/66/1f/661fa8e004810/heitec-logo-2024-1200px-ae.png)

:quality(80)/p7i.vogel.de/wcms/b7/61/b761ebb964e26288096b67f05fb30594/0127976474v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b9/b4/b9b48e164a8adfc48d941f0d06eb8e31/0128873058v2.jpeg)