Serie CompactPCI Plus, Teil 24 Signalintegrität auf CompactPCI Plus Backplanes

Bei CompactPCI Plus hat sich die Übertragungsrate gegenüber dem alten parallelen Bus um den Faktor 300 erhöht. Anstatt der ca. 150 Netze sind es bei CompactPCI Plus über 360, davon 340 Highspeed-Netze. Mit der Highspeed-Datenübertragung und höheren Leistungsdichte auf der Backplane steigt allerdings die Bitfehlerrate.

Anbieter zum Thema

Bei CompactPCI Plus wurde der parallele PCI-Bus durch das Highspeed-Interface PCI Express ersetzt. Zusätzlich wurden noch die ebenso auf Highspeed/Punkt-zu-Punkt-Verbindungen basierenden Schnittstellen SATA, USB und Ethernet hinzugefügt. Die Übertragungsrate erhöhte sich dabei gegenüber dem alten parallelen Bus um den Faktor 300. Anstatt der ca. 150 Netze sind es bei CompactPCI Plus über 360, davon 340 Highspeed-Netze. Wo liegen nun die Probleme, die die Bitfehlerrate (BER) erhöhen?

Mit steigender Takt- oder Datenfrequenz verringert sich die Wellenlänge des Datensignals entsprechend

v/f (v = Signalausbreitungsgeschwindigkeit im Medium, f = Frequenz)

Kommt die Länge von Leiterbahnelementen in die Größenordnung der Wellenlänge entstehen Wechselwirkungen, die zu Resonanzen und starken Signalverzerrungen führen können.

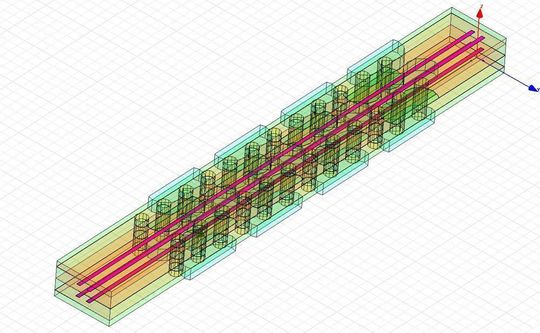

War bei CompactPCI die gesamte Leiterplatte noch deutlich kleiner als die Wellenlänge des Signals, können jetzt schon wenige mm Leiterbahnlänge zwischen zwei Diskontinuitäten des Signalpfades eine große Rolle spielen, so wie auch die Länge eines Vias (Bild 1). An jedem Impedanzsprung wird Signalenergie reflektiert. Hier liegt das Problem relativ kurzer Leitungen, da die Reflexion nicht genügend gedämpft wird.

Reflexionen erhöhen die Bitfehlerrate

Es sind weniger die Verluste langer Leitungen, die die Bitfehlerrate am Empfänger erhöhen, sondern die Reflexionen. Verluste lassen sich durch Signalkonditionierung (Pre-Emphasis, Equalization) relativ gut kompensieren, Reflexionen hingegen nicht. Sie erhöhen das Rauschen und den Jitter und damit die BER.

CompactPCI Plus Backplanes haben doppelt so viele Signale und weniger Platz zwischen den Steckverbindern, wodurch sich eine hohe Leistungsdichte ergibt. Dadurch werden Signalleitungen zwangsweise sehr eng geführt und können zuviel Übersprechen verursachen. Übersprechen aber trägt wie Reflexionen zum Rauschen und Jitter bei. Das Geschick des Designers erfordert, den richtigen Kompromiss für die Leitungsdichte und die Zahl der Lagen zu finden und generell Impedanzdiskontinuitäten zur verringern.

Die 3-D-Modellierung der Leiterplattenelemente und Simulation des gesamten Übertragungskanals zur Bestimmung der Bitfehlerrate ist eine sehr hilfreiche Methode, Boards und Backplanes im ersten Entwurf mit einer ausreichend niedrigen Bitfehlerrate zu entwickeln (siehe Augendiagramm).

(ID:316776)

:quality(80)/p7i.vogel.de/wcms/d8/78/d878b7bfc23826e6ddfce42443836d28/0130384280v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e9/ce/e9ce137e87eccac328ec5504c586c477/0129711019v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/68/46/684697b6eb687384e0d8c6803450401a/0130056395v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/88/a1/88a15070daae8c090f4256580cf8a61c/0130329906v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f7/90/f79070d95e48c6d1a5c77c5d05a7e4da/0130344018v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/1b/bb/1bbb096db776f5ab19ff87fc7f86392f/0130318021v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6a/42/6a423ced6604acf7d3eef8e4c0c2bd39/0130317237v4.jpeg)

:quality(80)/p7i.vogel.de/wcms/a2/31/a2319b6d6b473424b275f6489bbce348/0130213768v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/88/c28805ea7b2261235475146a5b0c61f8/0130313028v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/8d/fa8dedee195f29c33c89d86311c258ee/0130104146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cc/13/cc1378375499a26b5ddbb309d2155acb/0130085649v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/85/b0/85b0b32128f6d1968e975043f1e0b67b/0130342166v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/81/c0/81c03683c33cf69903df78a57145bcca/0130328599v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6d/f0/6df06a1488ceb6357c287fee993fad65/0130161592v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/10/45/1045969e69a1db4aaa73d0f74f55cc02/0129962687v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c7/f6/c7f61d0437c7f8fca3c6ff947ba2ad62/0129322490v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/66/0c/660c31afa35398bac9be42f2be73fdc4/0129073529v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/e4/bae4e54395e5a53088060531ef99b814/0130359274v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/af/35af7dd326d198475d06fbb69aa600b5/0130175971v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/2e/c02e7bf72bfc434888c37100e2511681/0130127767v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/ac/31/ac31fbd47f85c24ae7d13a73555c85e6/0130236430v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ef/a0/efa0d8af7bcf1d64636b877a04b853d9/0130136738v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bf/82/bf82f81061b759c454e15ec4c2e7560b/0130110139v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/74/96/74964a7715c738a9e8b17681445ceed3/0130103633v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/2f/b5/2fb51bc9f8702faa2195070c97fe7754/0130349161v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/78/ab/78abfaed29756f96d23ae135f707026a/0130332461v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b9/e5/b9e56a5eba2fbf56a6e3efac57f96dbb/0130345302v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9c/06/9c0651d3c2cec436277af3f698a6cf3f/0130342944v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/02/f8/02f84dfb1ad4ccfe94f3b4045bcee023/0130316909v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a2/b5/a2b54e377a6050b54acf8ac938b63ef8/0130318106v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/00/08/0008cc4b713f15ab39492f6c66b0485f/0130362942v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/63/88/63887b860cf66/me-logo-400px.jpeg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/127300/127366/65.jpg)

:fill(fff,0)/p7i.vogel.de/companies/66/1f/661fa8e004810/heitec-logo-2024-1200px-ae.png)

:quality(80)/p7i.vogel.de/wcms/6b/c0/6bc05651543f3d23dcd1f8fb811ff0fe/0126006256v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/5e/6b/5e6b5884a3188984c14796fdad74d307/0125018815v2.jpeg)