Schnittstellen-, Treiber- und Taktkonzepte für High-Speed-ADC Schaltungen mit schnellen Pipeline-A/D-Wandlern

Auflösung, Abtastrate und die dynamischen Leistungsfähigkeit von schnellen Pipeline-A/D-Wandler werden immer besser. Für den Designer besteht die Herausforderung darin, die statischen, insbesondere aber die dynamischen Kenndaten auf dem im Datenblatt angegebenen Niveau zu halten. Voraussetzung ist, dass die externen Bauelemente in der Umgebung des Datenwandlers sorgfältig ausgewählt werden.

Anbieter zum Thema

Im ersten Teil dieses Beitrages (siehe Link am Ende) wurde am Beispiel eines modernen 14-Bit-A/D-Wandlers dargelegt, wie sich die Leistungsfähigkeit eines schnellen Pipeline-A/D-Wandlers mit einer passenden Taktschaltung optimieren lässt. Dieser Teil erklärt, wie eine einwandfreie analoge Eingangsbeschaltung aussehen muss und wie sich die Daten mit dieser hohen Geschwindigkeit unverzerrt vom A/D-Wandler an ein FPGA oder ASIC übertragen lassen.

Die Eingangs-Beschaltung

Beim Auswählen und Testen eines A/D-Wandlers verwendet man in der Regel Signalgeneratoren zum Ansteuern des Eingangs. Es versteht sich, dass die gemessene Leistungsfähigkeit des A/D-Wandlers nicht besser sein kann als die Reinheit des angelegten Eingangssignals.

Das Ausgangssignal des Signalgenerators filtert man, damit harmonische Verzerrungen und Rauschen aus dem Generator nur begrenzt an den ADC-Eingang durchschlagen. Die harmonischen Verzerrungen zweiter Ordnung (H2) eines typischen Frequenz-Synthesizers dürften zwischen 40 und 50 dB liegen, während der entsprechende Wert des ADC14V155 bei 238 MHz 85 dBFS beträgt. Empfehlenswert ist das Verwenden abstimmbarer Bandpassfilter beispielsweise der Serie Trilithic VF, die Oberschwingungen zweiter und dritter Ordnung um 90 dB abschwächen.

Kritisch: Filtern des Eingangssignals in der Applikation

Auf jeden Fall kritisch ist das Filtern des Eingangssignals in der endgültigen Applikation. Die extrem große Eingangsbandbreite des ADC14V155 von 1,1 GHz bedeutet, dass der Baustein dieses gesamte Spektrum abtastet – einschließlich aller unerwünschten Artefakte, wie sie im ersten Teil dieses Beitrages im Abschnitt „Fallstricke“ beschrieben wurden.

Auch wenn der A/D-Wandler nur mit einer Abtastrate von 155 MSPS arbeitet, werden Störungen oberhalb dieser Frequenz durch Aliasing als Artefakte in das erste Nyquist-Band zurückgefaltet. Die Auswirkungen auf den Signal-Rauschabstand kann man sich leicht ausmalen. Vermeiden lässt sich dieses Problem durch Bandpassfilterung des Signals um seine Mittenfrequenz.

Kompromiss zwischen A/D-Wandler- und Verstärkerverzerrung

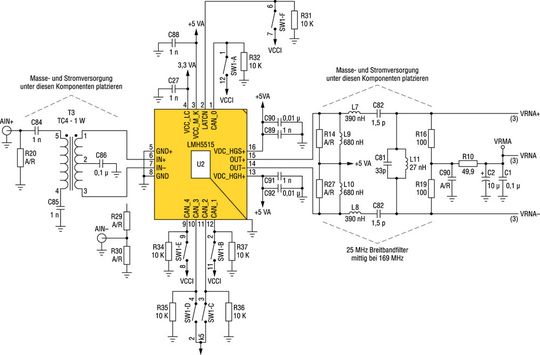

In der Mehrzahl der praktischen Anwendungsfälle wird das Eingangssignal mit einem Übertrager und/oder Verstärker an den A/D-Wandler gekoppelt. In Bild 1 ist zu sehen, wie der ADC14V155 mit dem DVGA LMH6515 angesteuert wird. Zwischen Verstärker und A/D-Wandler wird deshalb ein Filter 4. Ordnung mit einer auf 169 MHz zentrierten Bandbreite von 25 MHz eingefügt. Die Widerstände R16 und R19 stellen einen Gleichtakt-Bias für den A/D-Wandler her und legen die Lastimpedanz des Filters fest. Diese sollte übrigens nicht zu hoch gewählt werden, da hierdurch die Dämpfung des Filters sinkt und sich der SFDR-Wert verschlechtert. Es hat sich herausgestellt, dass ein Wert von 500 Ω den besten Kompromiss zwischen ADC- und Verstärker-Verzerrung ergibt.

Störungsfreien Dynamikbereich maximieren

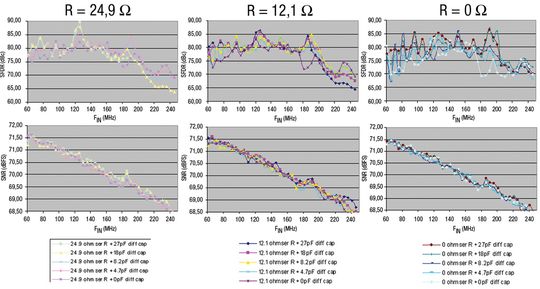

Zum Maximieren des störungsfreien Dynamikbereichs (SDFR) kann ein zusätzliches RC-Netzwerk eingefügt und auf die Eingangsfrequenz der Applikation abgestimmt werden. Das Netzwerk besteht aus zwei Reihenwiderständen an den Eingangs-Pins des A/D-Wandlers und einem Shunt-Kondensator. Diese Bauelemente haben infolge von Störungen aus der Sample-and-Hold-Schaltung am Eingang des ADC Rückwirkungen auf die Einschwingzeit.

Schließlich fungiert die RC-Kombination als letzter Tiefpass vor dem A/D-Wandler, und ihre Sperr-Frequenz wirkt sich auf die Rauschunterdrückung und die Oberwellen-Dämpfung aus. Hat der Shunt-Kondensator einen höheren Kapazitätswert, senkt dies die Sperr-Frequenz des Tiefpassfilters und verringert die Verzerrung bei niederen Frequenzen, allerdings auf Kosten der Eingangsbandbreite (Bild 2).

Im Datenblatt des ADC14V155 sind zwei 12,1-Ω-Widerstände und ein 15-pF-Kondensator angegeben, was über einen weiten fin-Bereich einen guten Kompromiss ergibt.

Faustregeln zur Entkopplung

Störungen können auch über die Referenz- und Stromversorgungs-Anschlüsse in den ADC eingekoppelt werden. Als Faustregel gilt, Entkoppel-Kondensatoren möglichst nahe am Gehäuse und den Pins des A/D-Wandlers zu platzieren. Hier zählt jeder Millimeter. Es sind mindestens zwei Kapazitätswerte (0,1 und 0,01 µF) für die Entkopplung zu verwenden, und überdies müssen die Kondensatoren direkt mit der Positiven bzw. Masse-Ebene verbunden werden.

Vermeiden sollte man lange Leiterbahnen mit ihren parasitären Widerständen und Induktivitäten. Messungen der SNR- und SFDR-Werte des ADC14155 im LLP bzw. TQFP-Gehäuse ergaben, dass es angesichts der langen Anschlüsse des TQFP-Gehäuses nötig ist, die Entkoppel-Kondensatoren auf der Unterseite der Leiterplatte direkt unterhalb der Referenz- und Stromversorgungs-Pins zu platzieren, damit ein Leistungs-Optimum erreicht wird. Bei Anordnung der Kondensatoren an der Oberseite verschlechterte sich der SNR um beinahe 3 dB, der SFDR-Wert um über 3 dB.

Die Ausgangs-Schnittstelle

Ist das analoge Eingangssignal digitalisiert, muss das Resultat einer weiteren Verarbeitungsstufe wie beispielsweise einem FPGA oder ASIC zugeführt werden. Jahrelang wurden CMOS-Ausgangsstufen zum Übertragen digitalisierter Daten verwendet. Der Ausgangspegel einer CMOS-Stufe ist jedoch lastabhängig und das Signal liegt als Spannung vor. Bei einem Single-Ended-Ausgang kommt hinzu, dass Gleichtaktstörungen nicht unterdrückt werden.

Da mit zunehmenden Schaltgeschwindigkeiten immer höhere Ströme zum Treiben der Lastkapazitäten benötigt werden, reduziert sich der Spannungshub der CMOS-Ausgänge bis bei etwa 150 MHz der Datentransfer mit CMOS-Schnittstellen nicht mehr zuverlässig möglich ist. Eine andere Schnittstelle muss verwendet werden: LVDS ist hier gut geeignet. Ein LVDS-Treiber liefert ein differenzielles Ausgangssignal von konstant 3,5 mA. Möglichst nah an den Empfänger-Pins müssen die differenziellen Ausgangsleitungen mit 100-Ω-Abschlusswiderständen verbunden werden.

Der ADC14V155 arbeitet mit einem zeitlich versetzten DDR-Ausgangsschema (Dual Data Rate), bei dem zunächst die ungeraden Bits und anschließend an denselben Pins die geraden Bits ausgegeben werden. Die Zustandswechsel an den Ausgängen erfolgen bei steigenden und fallenden Taktflanken. Das Gehäuse kommt deshalb mit 14 Pins aus, das sind 50% weniger. Am Empfängerbaustein ergibt sich dieselbe Ersparnis. Abgesehen von den Daten-Pins werden auch der Over-Range Indicator (OVR) und der Data Ready Strobe (DRDY) im LVDS-Format ausgegeben.

*Uwe Kopp ist als Field Applications Engineer bei National Semiconductor in Johannishov/Schweden tätig.

(ID:239373)

:quality(80)/p7i.vogel.de/wcms/37/ec/37ece4c276f37114e8f40696ff5dcd66/0130537789v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/46/7c/467c0afffbfd10c3553c2888a4a6289f/0130479810v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/12/3d/123d9eb2c2e4ce13296371a2ad3718a4/0130412664v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/e7/b6e755d9e704319c0bb59dc1ac2d67e8/0130537290v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/8b/10/8b10d1edceb749de99c1df3ad97be01e/0130564619v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ac/da/acda3bafe46d3bf8e104a2a7bc2ac557/0130535476v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ca/9b/ca9b681785123f9700518a46897f9779/0130428786v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/38/cb/38cbe19e814dd30b94780bc3946547ab/0130446533v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/88/c28805ea7b2261235475146a5b0c61f8/0130313028v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/8d/fa8dedee195f29c33c89d86311c258ee/0130104146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/7a/697a270ed7538378d1fbc0f0b240ed25/0130534691v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/e7/a4/e7a4e048491e60cb30e22a860f5d68bc/0130519425v4.jpeg)

:quality(80)/p7i.vogel.de/wcms/1b/f0/1bf02d41e3eac721823841a4c1228753/0130519149v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1a/53/1a539631c940d184689460600bd2b395/0130410666v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/10/45/1045969e69a1db4aaa73d0f74f55cc02/0129962687v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/e4/bae4e54395e5a53088060531ef99b814/0130359274v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/af/35af7dd326d198475d06fbb69aa600b5/0130175971v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/2e/c02e7bf72bfc434888c37100e2511681/0130127767v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/e1/0b/e10bc04827e33786548587e32bbae422/0130438700v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/06/3506f2a8d33a696aaef12a30771bd8d8/0130496747v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/ed/e5ed08c670c44565a9130e95a760dddc/0130494578v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ce/33/ce336bc438b912829effe8d4704dc159/0130480307v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/3a/72/3a722ed2ad6ac4894c352e6ce87b6560/0130567207v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e4/d1/e4d122a8ecce14b98c8298c1cc130194/0130561462v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1c/33/1c3399d0f7fb55bda7808310088accaf/0130565746v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/3c/55/3c5505dd3ca3971cddd09c583a4c907d/0130458429v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/2e/95/2e9597b5dc1873771c7fe9c32ac41e82/0130549010v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/15/56/15564dea31861c376a385658c3b961a3/0130465243v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bf/2a/bf2aad428ab1a80e6738fdbdc2efeb7e/0130453420v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/62/16/621651a93b1ef/logo-we-rgb-pos.png)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/111200/111228/65.jpg)

:fill(fff,0)/p7i.vogel.de/companies/68/62/68621fc4f1d39/logo.png)

:quality(80)/p7i.vogel.de/wcms/c4/c0/c4c0de4fce72a4d7ec90b7af787d7ddb/0124484092v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/c8/1e/c81efe8237fc680c7c14d23751a2c5ee/0127863835v2.jpeg)