Schnittstellen-, Treiber- und Taktkonzepte für High-Speed-ADC Schaltungen mit schnellen Pipeline-A/D-Wandlern - Teil 1

Die Auflösung, Abtastrate und die dynamischen Leistungsfähigkeit integrierter Pipeline-A/D-Wandler wurden in neue Bereiche vorangetrieben. Die Herausforderung für den Designer besteht darin, die statischen und insbesondere die dynamischen Kenndaten auf dem im Datenblatt angegebenen Niveau zu halten. Dazu müssen die externen Bauelemente in der Umgebung des Datenwandlers mit großer Sorgfalt ausgewählt werden.

Anbieter zum Thema

Die Leistung intergrierter, schneller Pipeline-A/D-Wandler hat derzeit neue Dimensionen erreicht. Der Designer steht vor der Aufgabe diese Leistungsfähigkeit mit einer entsprechenden Schaltung zu erhalten und zu optimieren. Im ersten Teil dieses Beitrages wird zunächst ein moderner 14-Bit-A/D-Wandler vorgestellt. Im zweiten Teil wird erklärt, wie eine einwandfreie analoge Eingangsbeschaltung aussehen muss und wie sich die Daten mit dieser hohen Geschwindigkeit unverzerrt vom ADC an ein FPGA oder ASIC übertragen lassen.

Der hier als Anwendungsbeispiel herangezogene ADC14V155 arbeitet mit einer Auflösung von 14 Bit und einer Abtastrate bis zu 155 MSPS. Der Baustein basiert auf einer differenziellen Pipeline-Architektur. Seine jitterarme Sample-and-Hold-Stufe sorgt für eine Leistungsbandbreite von 1,1 GHz.

Die Fähigkeit zum Abtasten von Signalen bis zu 450 MHz bewirkt eine höhere Flexibilität bei der Frequenzplanung. Der Entwickler ist nicht mehr an einfache Trägerarchitekturen gebunden und kann stattdessen auf Mehrfach-Trägerkonzepte setzen, indem er mit einem A/D-Wandler mehrere Kanäle oder Träger gleichzeitig digitalisieren lässt.

Störungsfrei Daten an FPGAs übertragen

Die Daten werden vom Chip über eine parallele LVDS-Schnittstelle (Low Voltage Differential Signaling) im DDR-Format (Dual Data Rate) übertragen, damit ein störungsfreier Datentransfer an moderne FPGAs möglich ist. Separate Stromversorgungen für die Ausgangs-Schnittstelle (1,8 V) und den analogen Teil (3,3 V) sollen das Störaufkommen und die Leistungsaufnahme des Bausteins weiter verringern. Die Verlustleistung des Bausteins liegt im Regelfall unter 1 W. Bei einer Eingangsfrequenz von 70 MHz kommt der A/D-Wandler auf einen Signal-Rauschabstand (SNR) von 71,7 dBFS sowie einen störungsfreien Dynamikbereich (SFDR) von 86,9 dBFS.

Diese Parameter werden nachfolgend genauer untersucht. Außerdem wird analysiert, an welchen Stellen das Design genauer betrachtet werden sollte.

Bei hohen Eingangsfrequenzen und großer Auflösung sind der Takt-Jitter und der Daten-Jitter diejenigen Faktoren, die den Signal-Rauschabstand eines ADC am gravierendsten beeinträchtigen. Um den SNR nicht zu reduzieren, muss der Jitter kleiner als das Quantisierungsrauschen (½ LSB) sein. Berechnet wird er nach Gleichung 1.

Optimiert man den Bereich der Eingangsspannung (Vin(p-p)) dahingehend, dass er exakt dem Eingangsbereich des A/D-Wandlers entspricht, wird der erste Term der Gleichung 1, sodass nur noch die Auflösung N und die Eingangsfrequenz fin eine Rolle spielen.

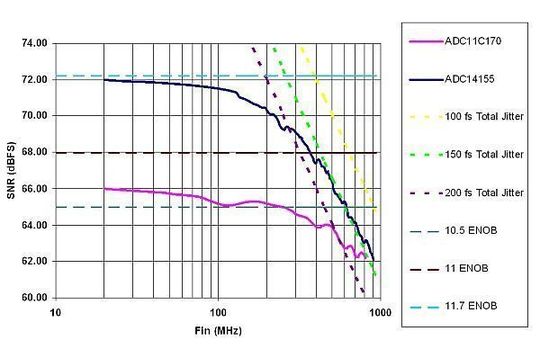

Eine Messung des Signal-Rauschabstands von ADCs mit Auflösungen von 11 bis 14 Bit ergibt, dass der Gesamt-Jitter des Systems bei Eingangsfrequenzen über 100 MHz bei einem 11-Bit-A/D-Wandler nicht größer als 200 fs sein darf und beim Beispielwandler ADC14V155 (11,5 ENOB) ca. 100 fs betragen sollte (Bild 1).

Taktquelle: Phasenrauschen und Jitter

Jetzt sollte ein genauerer Blick auf die Taktquelle geworfen werden. Für die meisten Takt-Produkte sind die Frequenz und das Phasenrauschen im Datenblatt angegeben. Die Begriffe Phasenrauschen und Jitter beschreiben dasselbe Phänomen, wobei das Phasenrauschen im Frequenzbereich dargestellt wird und man den Jitter durch Integration der Phasenrauschkurve erhält.

Einen guten Eindruck davon, was den unerwünschten Jitter auf dem A/D-Wandler-Takt verursacht, bekommt man somit durch die Auswertung des Phasenrausch-Diagramms. Günstig es ist, das Diagramm zunächst in zwei Bereiche zu untergliedern, nämlich das (Close-in-) Phasenrauschen in unmittelbarer Nähe des Nutzsignals und das Breitbandrauschen.

Da sich das Breitbandrauschen problemlos ausfiltern lässt, liegt das Augenmerk auf dem Close-in-Phasenrauschen. Wünschenswert ist eine Taktquelle mit möglichst geringem Rauschen nahe an der Taktfrequenz, die außerdem eine möglichst steile Bandbegrenzung bei geringst möglichem Offset aufweist.

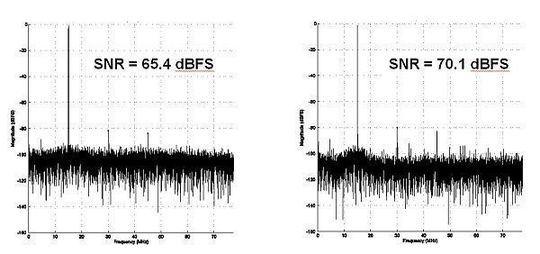

Die Notwendigkeit zum Ausfiltern des Breitbandrauschens ergibt sich aus der Tatsache, dass das Signal am Takteingang des ADC mit dem analogen Eingangssignal gefaltet wird. Der sehr hohen Eingangsbandbreite des ADC14V155 von 1,1 GHz steht eine entsprechend große Takteingangsbandbreite gegenüber. Dies hat zur Folge, dass ein großer Teil des Breitbandrauschens aus der Taktquelle durch Aliasing in Form von Artefakten in die erste Nyquist-Zone zurückgelangt und den Signal-Rauschabstand beeinträchtigen kann, wenn das Ausfiltern unterbleibt (Bild 2).

Fallstricke beim Subsampling

Wenn mit Subsampling gearbeitet wird, warten weitere Fallstricke. Unter Subsampling versteht man den Fall, dass die Taktfrequenz größer als das Doppelte der Signalfrequenz ist, womit im Prinzip das Nyquist-Kriterium verletzt wird. Darin heißt es, dass fS größer als das Doppelte von fin sein muss, um Aliasing zu vermeiden.

Subsampling hat zur Folge, dass das Signal und seine Oberschwingungen durch Aliasing in das erste Nyquist-Band zurückgelangen. Dies ist unproblematisch, solange bekannt ist, auf welche Frequenz sie abgebildet werden. Man arbeitet deshalb einen Frequenzplan aus, um sicherzugehen, dass der interessierende Frequenzbereich nicht durch aliasbedingte Artefakte verfälscht wird.

Ein beliebter Frequenzplan verwendet die Eingangsfrequenz, deren Artefakte auf fS/4 abgebildet werden. Nach diesem Frequenzplan fallen alle Oberwellen auf DC, fS/4 oder fS/2. Der Vorteil dieses Plans ist, dass ein maximaler Abstand zwischen den durch Oberschwingungen bedingten Artefakten entsteht, was die Filterung erleichtert und die Grundschwingung in der Mitte des Nyquist-Bands ansiedelt. Allerdings maskiert dieser Frequenzplan auch alle Oberschwingungs-Artefakte des A/D-Wandlers durch Überlappung, sodass das Ausgangsspektrum des ADC wesentlich besser aussieht als es eigentlich ist. Die tatsächliche Leistung wird sichtbar, wenn die Eingangsfrequenz um 0,1 bis 1 MHz verschoben wird, womit die Maskierung der einander überlappenden Artefakte wegfällt.

A/D-Wandler-Taktempfänger-Schaltung

Leider wird sogar die Taktempfänger-Schaltung im ADC selbst einen gewissen Jitter erzeugen. Ursache hierfür ist, dass jegliche Störungen auf der Versorgungsspannung den Ansprechpunkt des Taktempfängers geringfügig verändern, sodass sich diese Störungen als Phasenrauschen äußern, wenn ein Taktsignal mit endlicher Flankensteilheit verwendet wird. Dies entspricht der Umwandlung von Amplitudenmodulation (AM) in Phasenmodulation (PM).

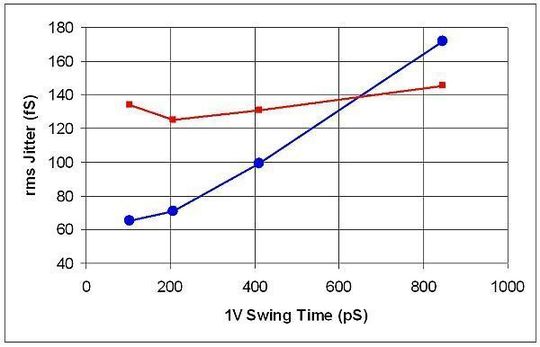

Bei den Störungen auf der Versorgungsspannung handelt es sich um Amplitudenmodulationen, die zu Taktstörungen (Phasenmodulationen) wird, die sich im Zeitbereich als Jitter äußern. Der Jitter ist umso stärker, je geringer die Anstiegsgeschwindigkeit des Taktsignals ist. Ein Takt mit hoher Flankensteilheit vermindert diesen Effekt somit (Bild 3). Als Taktsignal empfiehlt sich deshalb ein Rechtecksignal mit möglichst steilen Flanken, da dies den besten Signal-Rauschabstand ergibt.

Im Labor und für Testzwecke sind hochwertige Signalgeneratoren aufgrund ihrer Frequenz-Agilität die beste Wahl. Im vorliegenden Fall wurden mit den Modellen Agilent HP8644B und dem Rohde & Schwarz SMA100A zufriedenstellende Ergebnisse erzielt.

Ist der Frequenzplan festgelegt, liefert ein fest eingestellter Quarzoszillator das reinste Taktsignal. Sollten auf einer Leiterplatte mehrere Takte benötigt werden, empfiehlt sich die Verwendung eines Präzisions-Taktaufbereiters wie z.B. dem der Serie LMK0300/LMK0200 von National.

Im zweiten Teil wird dargelegt, wie eine einwandfreie analoge Eingangsbeschaltung aussehen sollte und wie die Daten unverzerrt übertragen werden.

*Uwe Kopp ist als Field Applications Engineer bei National Semiconductor in Johannishov/Schweden tätig.

(ID:236150)

:quality(80)/p7i.vogel.de/wcms/46/7c/467c0afffbfd10c3553c2888a4a6289f/0130479810v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/12/3d/123d9eb2c2e4ce13296371a2ad3718a4/0130412664v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d8/78/d878b7bfc23826e6ddfce42443836d28/0130384280v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/3c/55/3c5505dd3ca3971cddd09c583a4c907d/0130458429v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/51/54/5154dea79a134358001d1392c7319c5a/0130451629v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/13/20/13208d1c2797edd67d9ff216b403726b/0130471595v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/ca/9b/ca9b681785123f9700518a46897f9779/0130428786v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/38/cb/38cbe19e814dd30b94780bc3946547ab/0130446533v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6b/61/6b61373f1c3f06f7f9343e6b0f0e9cc8/0130225062v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/88/c28805ea7b2261235475146a5b0c61f8/0130313028v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/8d/fa8dedee195f29c33c89d86311c258ee/0130104146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cc/13/cc1378375499a26b5ddbb309d2155acb/0130085649v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/ed/e5ed08c670c44565a9130e95a760dddc/0130494578v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6d/91/6d91abfa1b16ffcf470c7147facd7aa8/0130387695v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1a/53/1a539631c940d184689460600bd2b395/0130410666v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/10/45/1045969e69a1db4aaa73d0f74f55cc02/0129962687v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c7/f6/c7f61d0437c7f8fca3c6ff947ba2ad62/0129322490v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/e4/bae4e54395e5a53088060531ef99b814/0130359274v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/af/35af7dd326d198475d06fbb69aa600b5/0130175971v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/2e/c02e7bf72bfc434888c37100e2511681/0130127767v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/06/3506f2a8d33a696aaef12a30771bd8d8/0130496747v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ce/33/ce336bc438b912829effe8d4704dc159/0130480307v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/7c/04/7c04916c305164fb10bc6cb05b51d934/0130431065v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ea/88/ea8807be45b913b774d18fd55e19f17b/0130468185v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/85/c0/85c0cdd8fd326013aed52ca96777c998/0130426877v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/47/ce/47ce64bad7990f276f68cbb24505f6dd/0130472850v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/15/56/15564dea31861c376a385658c3b961a3/0130465243v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bf/2a/bf2aad428ab1a80e6738fdbdc2efeb7e/0130453420v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/c8/b6c8f7732da417bda3d298412f4c0ed8/0130453104v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/69/72/69721860571ff/logo.jpeg)

:quality(80)/p7i.vogel.de/wcms/c8/1e/c81efe8237fc680c7c14d23751a2c5ee/0127863835v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/28/13/281318524d236feca2118e358cfda889/0129146156v2.jpeg)