IPC/JEDEC-Standard J-STD-020 RoHS-konforme Halbleiter richtig verarbeiten

Die Umstellung auf RoHS-konforme Baugrppenfertigungen ist eine Herausforderung für Produzenten und Anwender von Halbleitern. Neben bereits eingeführtem NiPd(Au) behauptet sich auch rein Zinn für Lotoberflächen bedrahteter Komponenten und SnAgCu-Lotkugeln für BGAs. Die gute Lötbarkeit dieser Anschlüsse ist sowohl mit SnPb als auch SnAgCu-Loten gegeben. Das Löten der Bauteile bedarf jedoch sorgfältiger Beachtung der MSL/PPT Forderungen nach J-STD-020C.

Anbieter zum Thema

Ein in den USA und Europa anerkannter Standard zur Bestimmung der Temperatursensitivität von Halbleiterbauelementen und den daraus abgeleiteten Lager- und Verarbeitungsbedingungen ist der von IPC (Institut for Printed Circuit Boards) und JEDEC (Joint Electron Device Engineering Council) gemeinsam erarbeitete J-STD-020A-Standard (siehe Link).

Dieser Standard entwickelte sich über Jahre und wurde erst kürzlich seitens IPC/JEDEC unter Mitwirkung von Fachleuten aus herstellenden und verarbeitenden Industrien von ICs mit der Rev. C auf den neuesten Stand gebracht. Der Standrad formuliert Kriterien für die Verarbeitbarkeit feuchteempfindlicher Bauelemente bei der Oberflächenmontage unter Wahrung der Gehäuseintegrität im Lötprozess.

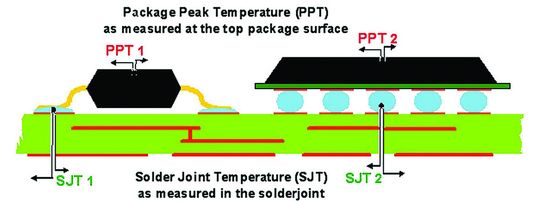

Die bei diesem Arbeitsschritt für die Bauteilzuverlässigkeit relevante Temperatur wird an seiner Oberseite gemessen und ist mittlerweile fachlich als Package Peak Temperature (PPT) festgeschrieben. Sie ist die wichtige Bezugsgröße bei der Bestimmung der Feuchteempfindlichkeit (MSL = Moisture Sensitivity Level), womit ausgesagt wird, wie lange die Bauelemente nach Öffnen einer gegebenenfalls vorhandenen Trockenverpackung vor einem Lötvorgang und ohne neuerlichen Trockenbackens an der Atmosphäre unter Normalbedingungen von 30°C und spezifizierter relativer Luftfeuchtigkeit (RH) gelagert werden dürfen.

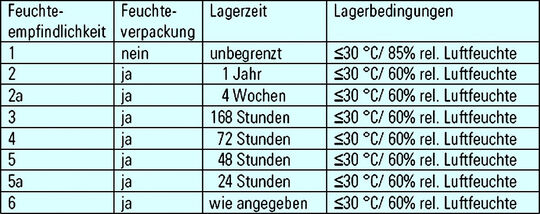

Klassifizierung der Feuchtempfindlichkeit von Bauteilen nach J-STD-020

Die Richtlinien in Tabelle 1 stammen aus dem J-STD-020C und sind auch für die Lagerung und Weiterverarbeitung von teilbestückten Leiterplatten bzw. für Reparatur oder Ablöten defekter Bauelemente für die weitere Analyse zutreffend und daher sinngemäß anzuwenden.

Die technische Notwendigkeit für diesen MSL/PPT Standard liegt in der grundsätzlichen Eigenschaft von Bauelementen begründet, die von Vergussmassen umhüllt, geklebt, abgedichtet oder unterfüllt sind, dass sich diese Plastikmaterialien über kurz oder lang wie Schwämme mit Wasser sättigen und dadurch unter anderem die Haftung an den Grenzflächen der beteiligten Materialien geschwächt wird.

Temperaturanstieg beim Löten kann Delaminationen und Risse verursachen

Wenn beim Löten die unterschiedlichen thermischen Ausdehnungskoeffizienten dieser Materialien zum Tragen kommen, können dadurch Delaminationen von Grenzflächen und Risse im Gehäuse auftreten, die einerseits zum Sofortausfall der Bauteile z.B. durch Bond-Abheber oder Bonddrahtscherungen führen, andererseits aber viel unangenehmere Folgen nach sich ziehen können, so dass es durch den Verlust an Gehäuseintegrität auch zu latenten Ausfällen kommen kann.

Verminderte Wärmeabfuhr durch den geringeren Flächenkontakt von Chip zum Gehäusekörper oder aber das beschleunigte Eindringen von Feuchte und chemisch aktiver Verunreinigungen sind beispielhaft als mögliche Mechanismen zu nennen und leiten hiermit dann spätere Systemausfälle wegen Überhitzung oder Leckströme oder Korrosion ein.

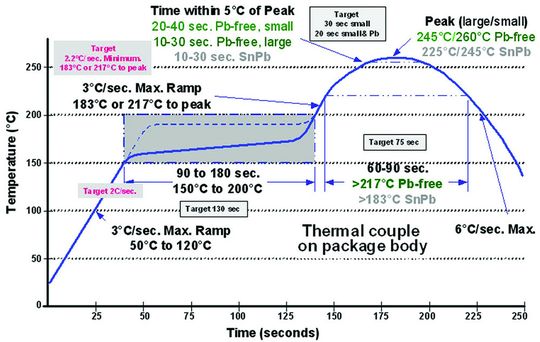

Die Schwierigkeit beim Verarbeiten von Bauteilen liegt im nahezu widersprüchlichen Bestreben, dass eine Lötung möglichst heiß und schnell erfolgen soll, dabei aber die Zuverlässigkeit des verarbeiteten Gutes nicht vergessen werden darf, wozu die Komponenten beim Löten möglichst kühl bleiben müssen und nur schonend, d.h. langsam erhitzt werden dürfen. Diese grundsätzliche Problematik tritt wieder verstärkt in den Vordergrund, wo die zur Ausbildung guter Lötstellen notwendige, d.h. minimalen Lötstellentemperaturen von Pb-freien SnAgCu Loten (liquidus 221 bis 227°C) mit 225 bis 235°C wesentlich höher liegen als die der vorher üblichen und naheutektischen SnPb Lote (liquidus 183 bis 210°C) mit einst 205 bis 220°C.

Zudem sind auf einer Baugruppe Gehäuse unterschiedlicher Bauformen, Materialien und Dimensionen angeordnet, d.h. verschiedene Wärmekapazitäten und Wärmeanbindungen, was dort insgesamt zu ungleichen Energieverteilungen und damit auch zu verschiedenen Temperaturen führt.

Prozesfenster im Bleifrei-Prozess ist enger als bei bleifreien Loten

Dieses Delta-T auf den Leiterplatten und zugehörige Prozess- oder Ofentoleranzen resultieren in Gehäusetemperaturen von 225 bis 245°C bei der konventionellen Verarbeitung mit bleihaltigen Loten und zu 245 bis 260°C beim Pb-freien Löten, wo das Prozessfenster auch noch enger ist. Die für die Leiterplattenfertigung relevanten Temperaturen müssen für zuverlässige Resultate detailliert bestimmt und befolgt werden (Bild 1).

„Kleine Bauteile werden heißer als große!“, kann als grobe Richtlinie vermerkt werden. Bei genauerem Hinsehen wird aber noch zu unterscheiden sein, ob das jeweilige Bauteil mehr Metall als Plastik enthält. Man denke hier nur an QFPs mit mehr oder weniger großen Trägerstreifen und gegebenenfalls eingebetteten Kühlkörpern oder auch an mehrlagige Substrate von zudem thermisch aufgebesserten BGAs, die aber rein äußerlich jeweils gleiche Abmessungen vorspielen, wobei die Anschlüsse unberücksichtigt bleiben.

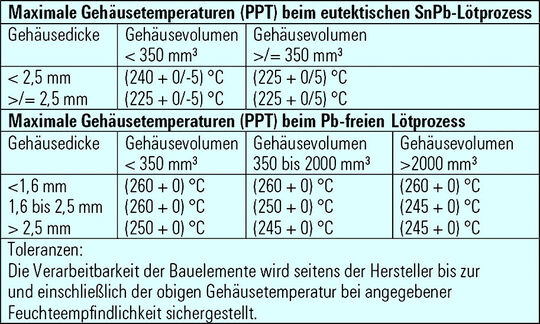

Maximale Gehäusetemperatur gemäß J-STD-020C gilt als Richtschnur

Tabelle 2 zeigt die veränderte thermische Belastung der Bauteilkörper beim herkömmlichen SnPb-Löten gegenüber der kommenden Pb-freien Verarbeitung. Diese dem oben genannten J-STD-020C entliehene Zuordnung von maximalen Gehäusetemperaturen an den durch Volumen und Dicke grob beschriebenen Bauteilen gilt als Richtschnur und ist im Zweifelsfall immer durch Messungen an der Bauteiloberseite auf der Leiterplatte während des Lötens zu verifizieren.

Zur Charakterisierung der Feuchteempfindlichkeit verwendet Freescale das in Bild 2 prinzipiell dargestellte Profil der während des Reflow-Lötvorgangs an der Gehäuseoberseite gemessenen Temperatur. Dieses Temperaturprofil basiert auf dem JEDEC/IPC J-STD-020 sowie der Auswertung und Einarbeitung von Kundenspezifikationen und deren realen Anwendungsprofilen aus Fertigungen.

Dr. Friedrich-Wilhelm Wulfert hat in seiner Publikation „Chancen und Risiken mit Pb-freien Halbleiterbauelementen“ beschrieben. Die ausführliche Dokumentation steht über den unten stehenden Link als PDF zur Verfügung.

*Dr. Friedrich-Wilhelm Wulfert, EMEA Quality Technologies & Standards bei Freescale Halbleiter Deutschlangd GmbH in München.

Artikelfiles und Artikellinks

(ID:232420)

:quality(80)/p7i.vogel.de/wcms/46/7c/467c0afffbfd10c3553c2888a4a6289f/0130479810v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/12/3d/123d9eb2c2e4ce13296371a2ad3718a4/0130412664v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d8/78/d878b7bfc23826e6ddfce42443836d28/0130384280v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/13/20/13208d1c2797edd67d9ff216b403726b/0130471595v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/38/cb/38cbe19e814dd30b94780bc3946547ab/0130446533v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a3/3e/a33e6d8a927d539ec6c3a0537f48f0f1/0130440028v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6b/61/6b61373f1c3f06f7f9343e6b0f0e9cc8/0130225062v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/15/93/1593dd152e6d58c5fc5da0d331777c54/0130357398v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/88/c28805ea7b2261235475146a5b0c61f8/0130313028v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/8d/fa8dedee195f29c33c89d86311c258ee/0130104146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cc/13/cc1378375499a26b5ddbb309d2155acb/0130085649v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6d/91/6d91abfa1b16ffcf470c7147facd7aa8/0130387695v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/85/b0/85b0b32128f6d1968e975043f1e0b67b/0130342166v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/1a/53/1a539631c940d184689460600bd2b395/0130410666v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/10/45/1045969e69a1db4aaa73d0f74f55cc02/0129962687v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c7/f6/c7f61d0437c7f8fca3c6ff947ba2ad62/0129322490v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/e4/bae4e54395e5a53088060531ef99b814/0130359274v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/af/35af7dd326d198475d06fbb69aa600b5/0130175971v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/2e/c02e7bf72bfc434888c37100e2511681/0130127767v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/7c/04/7c04916c305164fb10bc6cb05b51d934/0130431065v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/64/e5/64e5e333492f182ab7df5ab4c2b54c1e/0130463252v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/0a/95/0a95db4508128c4e11d5d268bf2c0a77/0130440053v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b3/65/b365dd5433c8b6d36c56c92b72f5b368/0130401081v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/85/c0/85c0cdd8fd326013aed52ca96777c998/0130426877v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f0/78/f07826d6c4e995980f1ada3377416aac/0130403626v4.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/c8/b6c8f7732da417bda3d298412f4c0ed8/0130453104v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/47/ce/47ce64bad7990f276f68cbb24505f6dd/0130472850v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/15/56/15564dea31861c376a385658c3b961a3/0130465243v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/98/ad/98ad595a6372aae8dbeac71681d23f41/0130450258v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bf/2a/bf2aad428ab1a80e6738fdbdc2efeb7e/0130453420v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/64/21/64219ce08bf52/logo.jpeg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/9700/9772/65.jpg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/56200/56252/65.jpg)

:quality(80)/p7i.vogel.de/wcms/d4/17/d4176bb4c4deb8e3e91b67c593794861/0124202466v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/45/6d/456d7a78ea1f15fe971bc6dbf0fc9c6c/0126526318v2.jpeg)