Anbieter zum Thema

Auch die Fertigungsprobleme, um eine durchgehend konstante Leistungsfähigkeit zu erzielen, müssen berücksichtigt werden, wenn verschiedene Anbieter für die Lieferung des Quarzes in Frage kommen. Quarze weisen viele Feinheiten in ihrer Spezifikation auf, die deren Leistungsfähigkeit und Interaktion beeinflussen. Dies wird meist nicht berücksichtigt. Somit kann ein Quarz eines Anbieters korrekt funktionieren, während ein scheinbar äquivalenter Quarz eines anderen Anbieters ein geringfügig anderes Merkmal besitzt, das zu Leistungsänderungen führt. Solche Probleme können zu erheblichen Problemen und Verzögerungen in der Fertigungs- und Testphase führen.

Ein Gehäuse für alle Taktgeber zusammen

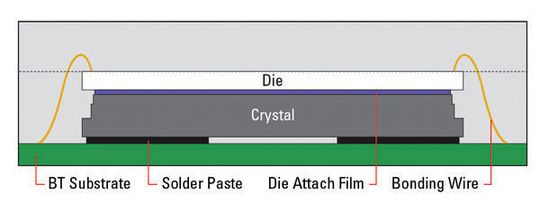

Die Lösung für die Probleme, die entstehen, wenn der Quarz in der Nähe des Taktgenerators platziert wird, scheint einfach: der Quarz wird in das Gehäuse des Oszillator-ICs integriert – entweder neben oder über dem Taktgenerator-IC (stacked). Fortschritte in der Gehäusetechnik machen dieses Co-Packaging möglich. Es findet bereits breiten Einsatz bei Multi-IC-Designs mit Prozessoren, die in einem Halbleiterprozess gefertigt werden und mit integriertem Speicher, der in einem anderen Prozess gefertigt wird.

Die Platzierung eines Chips oberhalb des Quarzes spart selbstverständlich Platz auf der Leiterplatte ein. Diese Integrationstechnik stand bis vor kurzem jedoch nur für Taktgenerator-ICs mit einer Ausgangsfrequenz zur Verfügung. Mehrere Takte konnten durch einen integrierten Quarz-/Taktgenerator-IC so nicht erzeugt werden. Der Co-Packaging-Ansatz war daher nur eingeschränkt nutzbar.

Einige Hersteller bieten MEMS-basierte Alternativen zu Quarz-Oszillatoren an. Mit einem MEMS-basierten Oszillator ist es möglich, eine kleine Single-Chip- oder Dual-Chip-Co-Packaged-Taktlösung zu erstellen. Generell reicht die Leistungsfähigkeit dieser Bausteine für bestimmte Anwendungen aus – aber nicht für alle. Aber auch hier gilt dies nur für einen einzigen Taktausgang. Also ergibt sich auch bei MEMS-Oszillatoren ein Problem, wenn mehrere Taktausgänge und Programmierbarkeit in einem Baustein vereint werden sollen.

Es existiert allerdings inzwischen eine alternative Lösung, mit der sich die Wahl zwischen einem Co-Packaged-Taktgenerator mit einer Ausgangsfrequenz und einem getrennten Quarz mit programmierbarem Multi-Output-Taktgenerator erübrigt. Die VersaClock5-Serie von IDT deckt verschiedene Bausteine mit integriertem Co-Packaged-Quarz ab, der unter einem Multi-Output-Taktgenerator-Chip angebracht ist – und das in einem Standardgehäuse mit der gleichen Stellfläche und Bauhöhe (0,9 mm), die der Taktgenerator-IC allein einnehmen würde (Bild 2).

(ID:43796579)

:quality(80)/p7i.vogel.de/wcms/37/ec/37ece4c276f37114e8f40696ff5dcd66/0130537789v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/46/7c/467c0afffbfd10c3553c2888a4a6289f/0130479810v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/12/3d/123d9eb2c2e4ce13296371a2ad3718a4/0130412664v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/e7/b6e755d9e704319c0bb59dc1ac2d67e8/0130537290v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/8b/10/8b10d1edceb749de99c1df3ad97be01e/0130564619v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ac/da/acda3bafe46d3bf8e104a2a7bc2ac557/0130535476v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ca/9b/ca9b681785123f9700518a46897f9779/0130428786v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/38/cb/38cbe19e814dd30b94780bc3946547ab/0130446533v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/88/c28805ea7b2261235475146a5b0c61f8/0130313028v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/8d/fa8dedee195f29c33c89d86311c258ee/0130104146v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/7a/697a270ed7538378d1fbc0f0b240ed25/0130534691v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/e7/a4/e7a4e048491e60cb30e22a860f5d68bc/0130519425v4.jpeg)

:quality(80)/p7i.vogel.de/wcms/1b/f0/1bf02d41e3eac721823841a4c1228753/0130519149v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1a/53/1a539631c940d184689460600bd2b395/0130410666v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/10/45/1045969e69a1db4aaa73d0f74f55cc02/0129962687v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/32/cd3243e4a9a6476265ef6ea9463dfbd8/0129852659v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/e4/bae4e54395e5a53088060531ef99b814/0130359274v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/af/35af7dd326d198475d06fbb69aa600b5/0130175971v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/2e/c02e7bf72bfc434888c37100e2511681/0130127767v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/8c/42/8c4211320be4a5ef78ca36d37b2406f2/0130561321v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e1/0b/e10bc04827e33786548587e32bbae422/0130438700v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/06/3506f2a8d33a696aaef12a30771bd8d8/0130496747v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/ed/e5ed08c670c44565a9130e95a760dddc/0130494578v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/34/6d/346d110316228e54143f67e9f273972b/0130589338v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c0/7a/c07aaa9f6122aeb6faed4f2a74dcb77f/0130542642v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/3a/72/3a722ed2ad6ac4894c352e6ce87b6560/0130567207v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e9/19/e919aaa1fb20114acd7f56479d9d6c0d/0130599660v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1c/33/1c3399d0f7fb55bda7808310088accaf/0130565746v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/2e/95/2e9597b5dc1873771c7fe9c32ac41e82/0130549010v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/15/56/15564dea31861c376a385658c3b961a3/0130465243v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/ea/d6eac438c362c545cab42ef0f30bcfc0/0130136975v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e5/6c/e56ceb935ba09cb66a4fd0f961b2d3e9/0129642888v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1f/691f39ba12be3cad90eb88bdabc456a6/0127321404v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/60/b6/60b601af20368/et-system-logo-rgb.png)

:fill(fff,0)/p7i.vogel.de/companies/66/1f/661fa8e004810/heitec-logo-2024-1200px-ae.png)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/68800/68851/65.jpg)

:quality(80)/p7i.vogel.de/wcms/61/6c/616c1e8041dbfc3c2faaa29430c62f8d/0127093746v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/42/cb/42cbcb66dffa2ef6548d5fb2edee4b4a/0130519441v3.jpeg)